基于超高性能指标输出的超声电机启动装置及方法

本发明涉及超声电机启动领域,特别是涉及一种基于超高性能指标输出的超声电机启动装置及方法。

背景技术:

1、超声电机具有摩擦驱动、断电自锁、响应速度快、力矩/质量比大、无电磁干扰等特点。当行波型超声电机参数调试、机械特性测试完成,并经过一段时间(短则十几分钟,长则数月数年)的静置以后,往往会随机出现原因不明的首次加电超声电机没有正常启动旋转,后续再怎么加电超声电机仍然无法正常启动的现象。该现象严重的制约了行波型超声电机技术研发和工程应用,例如:航空、航天、医疗、航海、车辆、深海、核能等安全可靠性要求达到99.99%的无人值守领域。目前行波型超声电机启动方法有线性扫频式(见图1)、升压式(见图2)等启动方法,以上启动方法虽然能够解决行波型超声电机的启动问题,但其安全可靠性仅为90%左右比较差,仅能够用于一般的民用行业。

技术实现思路

1、本发明的目的是提供一种基于超高性能指标输出的超声电机启动装置及方法,以解超声电机的启动时安全可靠性差的问题。

2、为实现上述目的,本发明提供了如下方案:

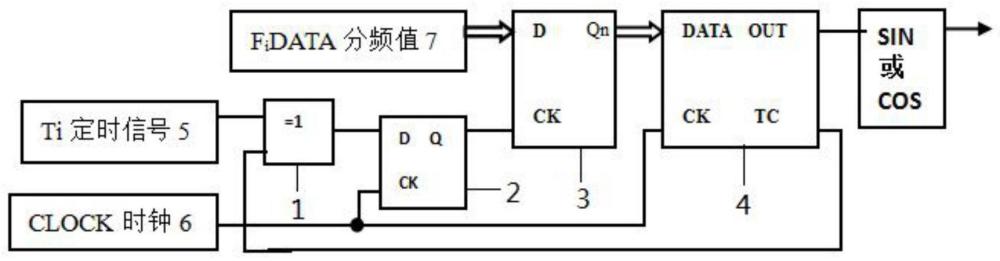

3、一种基于超高性能指标输出的超声电机启动装置,包括:双输入与门、d触发器、锁存器以及分频计数器;

4、所述双输入与门包括第一输入端、第二输入端以及输出端;所述第一输入端用于输入ti定时信号;所述ti定时信号为时长ti段的触发电平信号;所述第二输入端与所述分频计数器的脉冲输出端相连接;所述双输入与门输出端与所述d触发器的输入端相连接;

5、所述d触发器的时钟端,与所述分频计数器的时钟端相连接,并接收clock时钟;所述clock时钟为系统时钟;所述d触发器的输出端与所述锁存器的时钟端相连接;

6、所述锁存器的输入端用于接收fidata分频值;所述fidata分频值为时长ti段的输入信号;所述锁存器的多路数据输出端与所述分频计数器的数据输入端相连接;

7、所述分频计数器的输出端输出sin驱动信号或者cos驱动信号;

8、所述d触发器的时钟端在所述clock时钟同步时序作用下,当所述ti定时信号为‘1’高电平时,通过双输入与门将所述ti定时信号与所述分频计数器的脉冲输出端输出‘1’脉冲电平作与逻辑运算后输入至所述d触发器的输入端,同时所述d触发器的输出端输出上跳沿,强行将所述锁存器的多路数据输出端输出的上一时刻fi-1data分频值切换为所述锁存器的输入端输入的当前时刻fidata分频值,并锁存保持至所述d触发器的输出端下一次输出上跳沿,完成一次零相位同步时间差操作;同时,所述分频计数器的输出端输出sin驱动信号以及cos驱动信号,完成一次对分折叠频率差操作;从上限驱动信号频率开始,按照所述零相位同步时间差操作以及所述对分折叠频率差操作,一直跳至超声电机的工作频率,完成启动。

9、可选的,所述d触发器为数据触发逻辑电路;当所述d触发器的时钟端有上升沿脉冲触发时,所述d触发器的输出端的电平值由所述d触发器的输入端的电平值决定;

10、当所述d触发器的时钟端未接收到上升沿脉冲触发时,所述d触发器的输出端的电平值保持不变。

11、可选的,所述锁存器为多路数据同步触发逻辑电路;当所述锁存器的时钟端有上升沿脉冲触发时,所述锁存器的多路数据输出端输出的电平值由所述锁存器的输入端输入的电平值决定,此时,所述多路数据输出端输出的fidata分频值等于所述锁存器的输入端输入的fidata分频值;

12、当所述锁存器的时钟端未接收到上升沿脉冲触发时,所述锁存器的多路数据输出端的电平值保持不变。

13、可选的,所述分频计数器为减法计数器逻辑电路;当分频计数器的时钟端有上升沿脉冲触发时,所述分频计数器依据所述d触发器的输入端上一时刻的fi-1data分频值作减1运算;

14、所述分频计数器的计数值小于fi-1data/2值,所述分频计数器的输出端的电平值为‘0’电平值;

15、所述分频计数器的计数值大于等于fi-1data/2值时,所述分频计数器的输出端的电平值为‘1’电平值;

16、所述分频计数器的计数值等于fi-1data分频值时,所述分频计数器的计数值将重载所述d触发器的输入端的当前时刻的fidata分频值,所述分频计数器的脉冲输出端输出一个与所述分频计数器的时钟端相等周期的脉冲;

17、当分频计数器的时钟端未接收到上升沿脉冲触发时,所述分频计数器的输出端的电平值保持不变,且不受所述d触发器的输入端输入的fidata分频值的影响,所述分频计数器的脉冲输出端保持‘0’电平值。

18、一种基于超高性能指标输出的超声电机启动方法,所述启动方法包括:

19、控制clock时钟作为d触发器的时钟端以及所述分频计数器的时钟端的时钟信号;

20、控制ti定时信号作为双输入与门的允许信号;在所述clock时钟同步时序作用下,当所述ti定时信号为‘1’高电平时,通过双输入与门将所述ti定时信号与所述分频计数器的脉冲输出端输出‘1’脉冲电平作与逻辑运算后输入至所述d触发器的输入端;

21、控制当前时刻的fidata分频值作为锁存器的输入端的输入信号;当所述锁存器的时钟端接收到所述d触发器的输出端输出的上跳沿,强行将所述锁存器的多路数据输出端输出的上一时刻fi-1data分频值切换为所述锁存器的输入端输入的当前时刻fidata分频值,并锁存保持至所述d触发器的输出端下一次输出上跳沿,完成一次零相位同步时间差操作;

22、控制所述clock时钟依据所述分频计数器的输入端输入的当前时刻的fidata分频值,进行分频逻辑运算后,由所述分频计数器的输出端输出sin驱动信号或cos驱动信号,完成一次对分折叠频率差操作;

23、从上限驱动信号频率开始,按照所述零相位同步时间差操作以及所述对分折叠频率差操作,一直跳至超声电机的工作频率,完成启动。

24、可选的,所述分频计数器的输出端输出占空比为1:1的sin驱动信号或cos驱动信号。

25、根据本发明提供的具体实施例,本发明公开了以下技术效果:本发明在所述clock时钟同步时序作用下,当所述ti定时信号为‘1’高电平时,通过双输入与门将所述ti定时信号与所述分频计数器的脉冲输出端输出‘1’脉冲电平作与逻辑运算后输入至所述d触发器的输入端,同时所述d触发器的输出端输出上跳沿,强行将所述锁存器的多路数据输出端输出的上一时刻fi-1data分频值切换为所述锁存器的输入端输入的当前时刻fidata分频值,并锁存保持至所述d触发器的输出端下一次输出上跳沿,完成一次零相位同步时间差操作;同时,所述分频计数器的输出端输出sin驱动信号以及cos驱动信号,完成一次对分折叠频率差操作;从上限驱动信号频率开始,按照所述零相位同步时间差操作以及所述对分折叠频率差操作,一直跳至超声电机的工作频率,完成启动。大约四步即可完成一次安全可靠的快速启动过程,本发明将行波型超声电机启动的安全可靠性从原来的90%提升至99.99%以上。

- 还没有人留言评论。精彩留言会获得点赞!