车规级芯片、电路及设备的制作方法

本技术涉及电子,尤其涉及一种车规级芯片、电路及设备。

背景技术:

1、车规级芯片(也称为核心芯片(core chip))是一种用于车辆控制的芯片。车规级芯片的接地端口电连接印制电路板(printed circuit board,pcb)的接地端口,车规级芯片的部分端口电连接微控制单元(microcontroller unit,mcu)。车规级芯片用于在与微控制单元mcu进行信号传输的过程中,控制是否采用印制电路板pcb的电源端口bat2上的电压对负载load进行供电。其中,车规级芯片和微控制单元mcu均设置在印制电路板pcb上。

2、在传统技术中,通常按照低边挡反接保护方式,在车规级芯片的接地端口gnd1和印制电路板pcb的接地端口gnd2之间增加二极管,以在电源反接时(即印制电路板pcb的接地端口gnd2电连接电源的正极),对车规级芯片进行保护。

3、在低边挡反接保护方式中,车规级芯片的部分端口上的电压等于高电压(即电源的电压),导致车规级芯片的内部电路组件损坏。因此设计一种电路,以在电源反接时,防止车规级芯片的内部电路组件损坏,以提高车规级芯片的可靠性,成为亟待解决的技术问题。

技术实现思路

1、本技术提供一种车规级芯片、电路及设备,以解决在电源反接时车规级芯片的内部电路组件损坏的问题,实现了防止车规级芯片的内部电路组件损坏,提高车规级芯片的可靠性的目的。

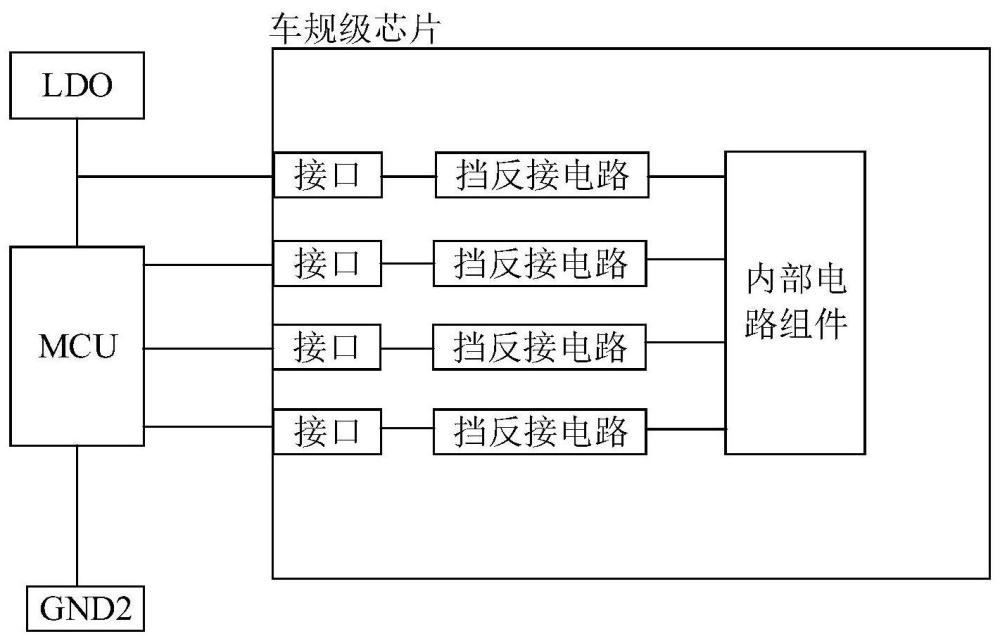

2、第一方面,本技术提供一种车规级芯片,包括:多个挡反接电路、多个端口和内部电路组件。所述挡反接电路电连接于所述端口和所述内部电路组件之间。所述端口还电连接控制器或者电连接于所述控制器和低压差线性稳压器之间。

3、所述挡反接电路,用于在对应的端口上的电压等于所述控制器的反接电压时,关断所述端口与所述内部电路组件之间的通路和/或控制所述内部电路组件停止工作。

4、通过第一方面提供的车规级芯片,在车规级芯片中设置端口对应的挡反接电路,在挡反接电路在对应的端口上的电压等于控制器的反接电压时(即在对应的端口上的电压等于高电压时),关断对应的端口与内部电路组件之间的通路和/或控制内部电路组件停止工作,可以避免内部电路组件在高电压下工作,防止内部电路组件损坏,提高车规级芯片的可靠性。

5、在一种可能的设计中,所述多个挡反接电路包括:第一挡反接电路、第二挡反接电路和第三挡反接电路。所述第一挡反接电路对应的端口为串行外设端口。所述第二挡反接电路对应的端口为第一端口。所述第三挡反接电路对应的端口为串行数据输出端口。所述内部电路组件包括所述第一内部电路和第二内部电路。所述第一挡反接电路分别电连接所述第一内部电路、所述第二内部电路和所述第三挡反接电路,所述第二挡反接电路电连接于所述第一端口和所述第一内部电路之间,所述第三挡反接电路电连接于所述串行数据输出端口和所述第二内部电路之间,所述第三挡反接电路还与所述串行外设端口电连接。

6、所述第一挡反接电路,用于在所述串行外设端口上的电压等于所述反接电压时,关断所述串行外设端口与所述第一内部电路之间的通路,关断所述串行外设端口与所述第二内部电路之间的通路,以及关断所述串行外设端口与所述第三挡反接电路之间的通路。

7、所述第二挡反接电路,用于在所述第一端口上的电压等于所述反接电压时,关断所述第一端口与所述第一内部电路之间的通路。

8、所述第三挡反接电路,用于在所述串行数据输出端口上的电压等于所述反接电压时,控制所述第二内部电路停止工作。

9、在一种可能的设计中,所述第一挡反接电路包括:第一高压晶体管、第一低压晶体管、第二低压晶体管、第一钳位二极管和第一电流源。

10、所述第一高压晶体管的第一端电连接所述串行外设端口,所述第一高压晶体管的第二端分别电连接所述第一内部电路、所述第二内部电路和所述第三挡反接电路,所述第一电流源的第一端接入所述车规级芯片的电荷泵输出电压,所述第一电流源的第二端电连接所述第一钳位二极管的阴极,所述第一钳位二极管的阳极电连接所述第二低压晶体管的第二端,所述第二低压晶体管的第一端电连接所述第一低压晶体管的第二端,所述第一低压晶体管的第一端电连接所述车规级芯片的接地端口,所述第一高压晶体管的控制端电连接于所述第一电流源的第二端和所述第一钳位二极管的阴极之间,所述第二低压晶体管的控制端电连接于所述第二低压晶体管的第一端和第一低压晶体管的第二端之间,所述第一低压晶体管的控制端电连接于所述第一低压晶体管的第一端和车规级芯片的接地端口之间。

11、在一种可能的设计中,所述第二挡反接电路包括:第一电阻和第二高压晶体管。

12、所述第一电阻的第一端电连接所述第一端口,所述第一电阻的第二端电连接所述第二高压晶体管的第一端,所述第二高压晶体管的第二端电连接所述第一内部电路的第二输入端,所述第二高压晶体管的控制端接入所述参考电压。

13、在一种可能的设计中,所述第一端口包括串行时钟端口和/或串行数据输入端口。

14、在一种可能的设计中,所述第三挡反接电路包括:第二钳位二极管、第三钳位二极管、第四钳位二极管、第二电阻、第三电阻、第四电阻、第五电阻、第三高压晶体管、第三低压晶体管、第四低压晶体管和第五低压晶体管。

15、所述串行外设端口电连接所述第二内部电路,所述第三钳位二极管的阴极电连接于所述串行外设端口和所述第二内部电路之间,所述第三钳位二极管的阳极电连接所述第二电阻的第一端,所述第二电阻的第二端电连接所述第三电阻的第一端,所述第三电阻的第二端电连接所述车规级芯片的接地端口。

16、所述第二钳位二极管的阴极电连接于所述串行外设端口和所述第二内部电路之间,所述第二钳位二极管的阳极电连接所述第三高压晶体管的第二端,所述第三高压晶体管的第一端电连接所述车规级芯片的接地端口,所述第三高压晶体管的控制端电连接于所述第三钳位二极管的阳极和所述第二电阻的第一端之间,所述第二内部电路还电连接于所述第二钳位二极管的阳极和所述第三高压晶体管的第二端之间。

17、所述第四钳位二极管的阴极、所述第三低压晶体管的控制端和所述第四低压晶体管的控制端均电连接于所述第二电阻的第二端和所述第三电阻的第一端之间,所述第四钳位二极管的阳极、所述第三低压晶体管的第二端、所述第四低压晶体管的第二端和第五低压晶体管的第二端均电连接于所述第三电阻的第二端和所述车规级芯片的接地端口之间,所述第三低压晶体管的第二端电连接所述第二内部电路,所述第四低压晶体管的第二端通过所述第四电阻电连接所述第一挡反接电路电连接,所述第五低压晶体管的控制端电连接于所述第四低压晶体管的第二端和所述第四电阻电连接,所述第五低压晶体管的第一端通过所述第五电阻电连接于所述第二内部电路和所述第三高压晶体管的第二端之间。

18、第二方面,本技术提供一种保护电路,应用于第一方面中任一项所述的车规级芯片,所述保护电路包括:开关器和电压控制器。所述开关器的第一端电连接印制电路板的接地端口,所述开关器的第二端电连接所述车规级芯片的接地端口,所述开关器的控制端电连接所述电压控制器的第一端,所述电压控制器的第二端电连接于所述开关器的第二端与所述车规级芯片的接地端口之间,所述电压控制器的第三端电连接所述印制电路板的电源端口。其中,所述车规级芯片、所述开关器、所述电压控制器和所述保护电路设置在所述印制电路板上。

19、所述电压控制器,用于在所述印制电路板的电源端口上的电压小于所述反接电压时,控制所述开关器断开,以关断所述印制电路板的接地端口和所述车规级芯片的接地端口之间的通路。并在所述印制电路板的电源端口上的电压等于所述反接电压时,控制所述开关器导通,以导通所述印制电路板的接地端口和所述车规级芯片的接地端口之间的通路,所述开关器在导通时的压降小于预设电压阈值。

20、在本技术实施例中,在电源反接时,电压控制器控制开关器断开,以关断印制电路板的接地端口和车规级芯片的接地端口之间的通路,避免内部电路组件在高电压下工作,防止内部电路组件损坏,提高车规级芯片的可靠性。在电源正接时,电压控制器控制开关器导通,导通印制电路板的接地端口和车规级芯片的接地端口之间的通路。由于开关器在导通时的压降小于预设电压阈值,因此可以提高车规级芯片的冷启动性。

21、在一种可能的设计中,所述开关器包括:第四高压晶体管。

22、所述第四高压晶体管的第一端电连接所述印制电路板的接地端口,所述第四高压晶体管的第二端电连接所述车规级芯片的接地端口,所述第四高压晶体管的控制端电连接所述电压控制器的第一端。

23、在一种可能的设计中,所述电压控制器包括:第七高压晶体管、第五电阻、第六电阻、第八高压晶体管、第五钳位二极管和第二电流源。

24、所述第七高压晶体管的第二端、所述第五电阻的第一端和所述第六电阻的第一端均电连接所述印制电路板的电源端口,所述第七高压晶体管的控制端和所述第八高压晶体管的控制端电连接,所述第六电阻的第二端电连接于所述第七高压晶体管的控制端和所述第八高压晶体管的控制端之间,所述第五电阻的第一端电连接所述第八高压晶体管的第二端,所述第八高压晶体管的第一端电连接所述第四高压晶体管的控制端,所述第四高压晶体管的第一端电连接所述印制电路板的接地端口,所述第四高压晶体管的第二端电连接所述车规级芯片的接地端口,所述第五钳位二极管的阴极电连接于所述第八高压晶体管的第一端和所述第四高压晶体管的控制端之间,所述第五钳位二极管的阳极电连接于所述第四高压晶体管的第二端和所述车规级芯片的接地端口之间,所述第七高压晶体管的第一端通过所述第二电流源电连接于所述第四高压晶体管的第二端和所述车规级芯片的接地端口之间。

25、在一种可能的设计中,所述电压控制器还包括:第六低压晶体管和第七低压晶体管。

26、所述第六低压晶体管的第二端电连接所述印制电路板的接地端口,所述第六低压晶体管的第一端电连接所述第七低压晶体管的第二端,所述第六低压晶体管的控制端电连接于所述第六低压晶体管的第一端和所述第七低压晶体管的第二端之间,所述第七低压晶体管的第一端和所述第七低压晶体管控制端均电连接于所述第七高压晶体管的控制端和所述第八高压晶体管的控制端之间。

27、第三方面,本技术提供一种车载电路,包括:控制器、低压差线性稳压器、第一挡反二极管、第二挡反二极管和如第一方面任一项所述的车规级芯片。

28、所述第二挡反二极管的阳极电连接印制电路板的电源端口,所述第二挡反二极管的阴极电连接所述低压差线性稳压器的输入端,所述低压差线性稳压器的输出端电连接所述控制器的输入端,所述控制器的接地端电连接所述印制电路板的接地端口。

29、所述车规级芯片的第一端口和串行数据输出端口电连接所述控制器,所述车规级芯片的串行外设端口电连接于所述低压差线性稳压器的输出端和所述控制器的电压输入端之间,所述车规级芯片的电源端口电连接所述印制电路板的电源端口,所述车规级芯片的接地端口电连接所述第一挡反二极管的阳极,所述第一挡反二极管阴极电连接所述印制电路板的接地端口。

30、上述第三方面中所提供的车载电路,其有益效果可以参见上述第一方面和第一方面的任一项所带来的有益效果,在此不再赘述。

31、第四方面,本技术提供一种车载电路,包括:控制器、低压差线性稳压器、第二挡反二极管、如第一方面任一项所述的车规级芯片以及如第二方面任一项所述的保护电路。

32、所述第二挡反二极管的阳极电连接印制电路板的电源端口,所述第二挡反二极管的阴极电连接所述低压差线性稳压器的输入端,所述低压差线性稳压器的输出端电连接所述控制器的电压输入端,所述控制器的接地端电连接所述印制电路板的接地端口。

33、所述车规级芯片的第一端口和串行数据输出端口电连接所述控制器,所述车规级芯片的串行外设端口电连接于所述低压差线性稳压器的输出端和所述控制器的电压输入端之间,所述车规级芯片的电源端口电连接所述印制电路板的电源端口,所述车规级芯片的接地端口电连接所述保护电路的第一端,所述保护电路的第二端电连接所述印制电路板的接地端口,所述保护电路的第三端电连接所述印制电路板的电源端口。

34、上述第四方面中所提供的车载电路,其有益效果可以参见上述第一方面、第一方面的任一项、第二方面和第二方面的任一项所带来的有益效果,在此不再赘述。

35、第五方面,本技术提供一种车辆,包括:如第三方面或者第四方面所述的车载电路。

36、上述第五方面中所提供的车辆,其有益效果可以参见上述第三方面或者第四方面所带来的有益效果,在此不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!