一种欠频、过压检测硬件保护电路的制作方法

本技术涉及保护电路,具体的涉及一种欠频、过压检测硬件保护电路。

背景技术:

1、现在设备对于一些参数的保护实现,通常采用软件的数字保护来实现,软件保护的优点也是非常的明显,保护参数整定简单,保护速度快;然而,软件保护在下面的应用场合并不适用:一、有隔离需要:数字处理器需要采集的信息一般比较多,大量的采集信号电位通常电位不一致,因此采用数字处理器的软件计算的话,需要采取相当多的隔离措施,隔离成本会比较高;二、纯硬件控制的需要,控制部分并没有数字处理器:在一些逆变器、电源、整流器等设备,本身并没有数字处理器,整个控制和电路均采用纯硬件的方式来实现;三、小型化的需要:不能采用较大的时间继电器、热继电器等应用场合。

2、此外,专利公开号为cn210224934u的中国实用新型专利文献公开一种硬件保护电路,包括分压电路、硬件保护电路和检测电路,其中:分压电路与硬件保护电路连接,硬件保护电路和检测电路连接,硬件保护电路包括欠压保护电路和过压保护电路,该硬件保护电路实现了采用硬件的方式对设备进行欠压和过压保护。然而,上述的硬件保护电路功能比较单一,仅有欠压和过压保护功能,并不具备欠频保护、保护锁定、以及故障恢复以后的解锁恢复等功能。

技术实现思路

1、为了克服现有技术中硬件保护电路存在功能比较单一,不具备欠频保护、保护锁定、以及故障恢复以后的解锁恢复等功能的问题,本实用新型提供一种欠频、过压检测硬件保护电路。

2、本实用新型技术方案如下所述:

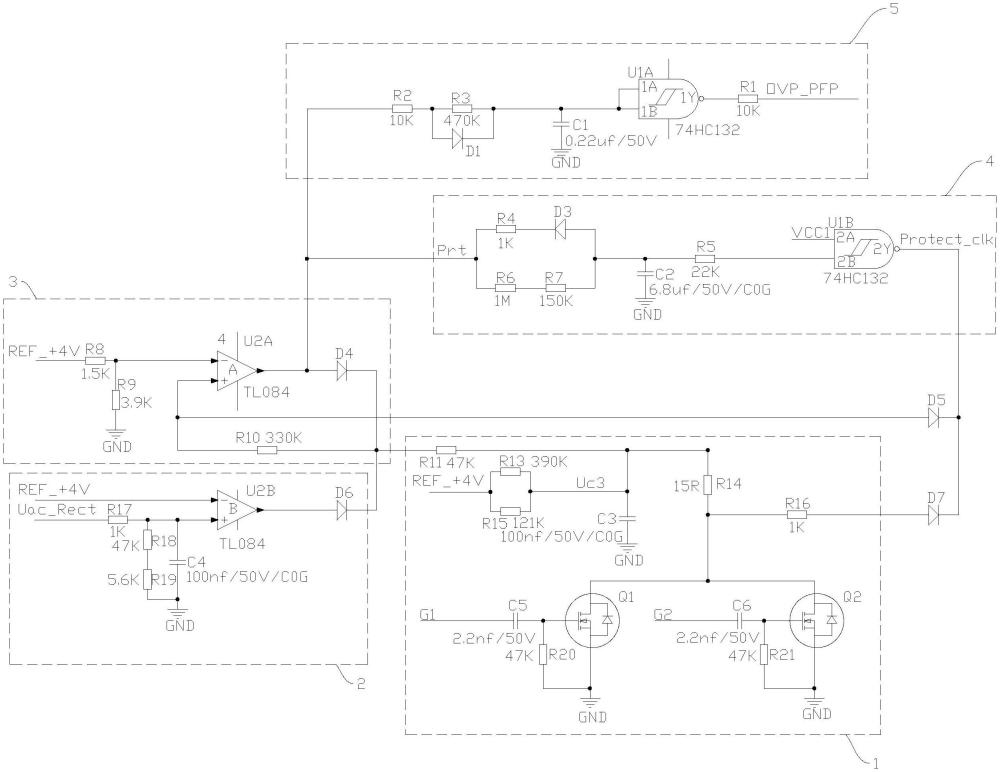

3、一种欠频、过压检测硬件保护电路,包括频率检测电路、过压检测电路、保护动作电路、复位时钟电路及故障锁定延时电路,所述频率检测电路的输出端、所述过压检测电路的输出端及所述复位时钟电路的输出端均与所述保护动作电路的输入端连接,所述保护动作电路的输出端分别与所述复位时钟电路的输入端和所述故障锁定延时电路的输入端连接。

4、根据上述的欠频、过压检测硬件保护电路,所述频率检测电路包括电阻r11、电阻r13、电阻r15、电阻r14、电阻r16、电阻r20、电阻r21、电容c3、电容c5、电容c6、开关管q1、开关管q2,所述保护动作电路的输入端与电阻r11的一端连接,电阻r11的另一端分别与电阻r13的一端、电阻r15的一端、电容c3的一端、电阻r14的一端连接,电阻r13的另一端和电阻r15的另一端均与基准电压连接,电容c3的另一端与接地端连接,电阻r14的另一端分别与电阻r16的一端、开关管q1的第一端、开关管q2的第一端连接,电阻r16的另一端与所述复位时钟电路的输出端连接,开关管q1的第二端分别与电容c5的一端、电阻r20的一端连接,电容c5的另一端与第一脉冲驱动信号连接,开关管q1的第三端分别与电阻r20的另一端、接地端连接,开关管q2的第二端分别与电容c6的一端、电阻r21的一端连接,电容c6的另一端与第二脉冲驱动信号连接,开关管q2的第三端分别与电阻r21的另一端、接地端连接。

5、进一步的,所述第一脉冲驱动信号为输入电压的正半周脉冲信号,所述第二脉冲驱动信号为输入电压的负半周脉冲信号。

6、进一步的,电阻r16的另一端经过二极管d7后与所述复位时钟电路的输出端连接。

7、根据上述的欠频、过压检测硬件保护电路,所述过压检测电路包括运算放大器u2b、电阻r17、电阻r18、电阻r19、电容c4、二极管d6,运算放大器u2b的负极输入端与基准电压连接,运算放大器u2b的正极输入端分别与电阻r17的一端、电阻r18的一端、电容c4的一端连接,电阻r17的另一端与输入电压连接,电阻r18的另一端经过电阻r19后分别与电容c4的另一端和接地端连接,运算放大器u2b的输出端经过二极管d6后与所述保护动作电路的输入端连接。

8、根据上述的欠频、过压检测硬件保护电路,所述保护动作电路包括运算放大器u2a、电阻r8、电阻r9、电阻r10、二极管d4,运算放大器u2a的负极输入端分别与电阻r8的一端和电阻r9的一端连接,电阻r8的另一端与基准电压连接,电阻r9的另一端与接地端连接,运算放大器u2a的正极输入端分别与电阻r10的一端和所述复位时钟电路的输出端连接,电阻r10的另一端分别与二极管d4的一端、所述频率检测电路的输出端、所述过压检测电路的输出端连接,运算放大器u2a的输出端分别与二极管d4的另一端、所述复位时钟电路的输入端、所述故障锁定延时电路的输入端连接。

9、根据上述的欠频、过压检测硬件保护电路,所述复位时钟电路包括电阻r4、电阻r5、电阻r6、电阻r7、二极管d3、电容c2、与非门u2a,电阻r4的一端和电阻r5的一端分别与所述保护动作电路的输出端连接,电阻r4的另一端与二极管d3的一端连接,电阻r6的另一端与电阻d7的一端连接,二极管d3的另一端分别与电阻r7的另一端、电容c2的一端、电阻r5的一端连接,电容c2的另一端与接地端连接,电阻r5的另一端与与非门u2a的第一输入端连接,与非门u2a的第二输入端与供电电压连接,与非门u2a的输出端与所述复位时钟电路的输出端连接。

10、进一步的,与非门u2a的输出端经过二极管d5后与所述复位时钟电路的输出端连接。

11、根据上述的欠频、过压检测硬件保护电路,所述故障锁定延时电路包括电阻r1、电阻r2、电阻r3、二极管d1、电容c1、与非门u1a,电阻r2的一端分别与所述保护动作电路的输出端和所述复位时钟电路的输入端连接,电阻r2的另一端分别与电阻r3的一端和二极管d1的一端连接,电阻r3的另一端分别与二极管d1的另一端、电容c1的一端、与非门u1a的输入端连接,电容c1的另一端与接地端连接,与非门u1a的输出端经过电阻r1后与外部电路连接。

12、与现有技术相比,本实用新型的有益效果在于:

13、本实用新型提供的一种欠频、过压检测硬件保护电路通过设置频率检测电路、过压检测电路、保护动作电路、复位时钟电路及故障锁定延时电路,实现了对欠频、过压的保护,以及保护锁定、故障恢复以后的解锁恢复功能,可以防止出现故障信号的抖动,也能躲过复位保护动作电路的复位时钟低脉冲,从而不影响故障信号的锁定,适用于有隔离需要、纯硬件控制需要以及小型化的需要应用场合。

技术特征:

1.一种欠频、过压检测硬件保护电路,其特征在于,包括频率检测电路、过压检测电路、保护动作电路、复位时钟电路及故障锁定延时电路,所述频率检测电路的输出端、所述过压检测电路的输出端及所述复位时钟电路的输出端均与所述保护动作电路的输入端连接,所述保护动作电路的输出端分别与所述复位时钟电路的输入端和所述故障锁定延时电路的输入端连接;

2.根据权利要求1所述的欠频、过压检测硬件保护电路,其特征在于,所述频率检测电路包括电阻r11、电阻r13、电阻r15、电阻r14、电阻r16、电阻r20、电阻r21、电容c3、电容c5、电容c6、开关管q1、开关管q2,所述保护动作电路的输入端与电阻r11的一端连接,电阻r11的另一端分别与电阻r13的一端、电阻r15的一端、电容c3的一端、电阻r14的一端连接,电阻r13的另一端和电阻r15的另一端均与基准电压连接,电容c3的另一端与接地端连接,电阻r14的另一端分别与电阻r16的一端、开关管q1的第一端、开关管q2的第一端连接,电阻r16的另一端与所述复位时钟电路的输出端连接,开关管q1的第二端分别与电容c5的一端、电阻r20的一端连接,电容c5的另一端与第一脉冲驱动信号连接,开关管q1的第三端分别与电阻r20的另一端、接地端连接,开关管q2的第二端分别与电容c6的一端、电阻r21的一端连接,电容c6的另一端与第二脉冲驱动信号连接,开关管q2的第三端分别与电阻r21的另一端、接地端连接。

3.根据权利要求2所述的欠频、过压检测硬件保护电路,其特征在于,所述第一脉冲驱动信号为输入电压的正半周脉冲信号,所述第二脉冲驱动信号为输入电压的负半周脉冲信号。

4.根据权利要求2所述的欠频、过压检测硬件保护电路,其特征在于,电阻r16的另一端经过二极管d7后与所述复位时钟电路的输出端连接。

5.根据权利要求1所述的欠频、过压检测硬件保护电路,其特征在于,所述过压检测电路包括运算放大器u2b、电阻r17、电阻r18、电阻r19、电容c4、二极管d6,运算放大器u2b的负极输入端与基准电压连接,运算放大器u2b的正极输入端分别与电阻r17的一端、电阻r18的一端、电容c4的一端连接,电阻r17的另一端与输入电压连接,电阻r18的另一端经过电阻r19后分别与电容c4的另一端和接地端连接,运算放大器u2b的输出端经过二极管d6后与所述保护动作电路的输入端连接。

6.根据权利要求1所述的欠频、过压检测硬件保护电路,其特征在于,所述保护动作电路包括运算放大器u2a、电阻r8、电阻r9、电阻r10、二极管d4,运算放大器u2a的负极输入端分别与电阻r8的一端和电阻r9的一端连接,电阻r8的另一端与基准电压连接,电阻r9的另一端与接地端连接,运算放大器u2a的正极输入端分别与电阻r10的一端和所述复位时钟电路的输出端连接,电阻r10的另一端分别与二极管d4的一端、所述频率检测电路的输出端、所述过压检测电路的输出端连接,运算放大器u2a的输出端分别与二极管d4的另一端、所述复位时钟电路的输入端、所述故障锁定延时电路的输入端连接。

7.根据权利要求1所述的欠频、过压检测硬件保护电路,其特征在于,与非门u2a的输出端经过二极管d5后与所述复位时钟电路的输出端连接。

技术总结

本技术公开了一种欠频、过压检测硬件保护电路,包括频率检测电路、过压检测电路、保护动作电路、复位时钟电路及故障锁定延时电路,所述频率检测电路的输出端、所述过压检测电路的输出端及所述复位时钟电路的输出端均与所述保护动作电路的输入端连接,所述保护动作电路的输出端分别与所述复位时钟电路的输入端和所述故障锁定延时电路的输入端连接。本技术提供的硬件保护电路实现了对欠频、过压的保护,以及保护锁定、故障恢复以后的解锁恢复功能。

技术研发人员:李金龙,沈振雄,尹巧红

受保护的技术使用者:深圳市费思泰克科技有限公司

技术研发日:20230504

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!