一种高速低功耗CMOS电压转换电路的制作方法

本发明涉及集成电路,特别涉及一种高速低功耗cmos电压转换电路。

背景技术:

1、cmos电路中总是有低压和高压电源域,不同电源域之间的信号沟通就涉及到电压抓转换,因此电压转换电路是一个基本电路。传统的电压转换电路如图1所示,核心电路是两个io pmos连接成latch结构,由两个io nmos驱动。电路输出为1时完全由上方的pmos驱动,电路输出为0时由下方的nmos驱动。

2、这种传统的电路存在功耗大,速度低的缺点,原因如下:在电路翻转时存在nmos和pmos的竞争,也就是nmos的下拉能力要远大于pmos的上拉能力。由于core(核心)电压远低于io电压,同时core电压面对的是io nmos,因此nmos的过驱动电压远远低于pmos的过驱动电压,必须将io nmos的尺寸设计的特别大才可以竞争过pmos;而过大的nmos尺寸对前面的电路来说是巨大的负载,因此严重影响速度同时增加功耗。

3、先进制程中的core电压和io电压的差距越来越大,而现在电路的速度越来越高。因此传统电路面临的速度和功耗瓶颈越来越大,甚至不能满足要求。因此迫切需要一种新的电路能够提供高速转换,并且在兼顾高速的同时还能够降低功耗,以适应更多的实际应用场景。

技术实现思路

1、本发明的目的在于提供一种高速低功耗cmos电压转换电路,以解决背景技术中的问题。

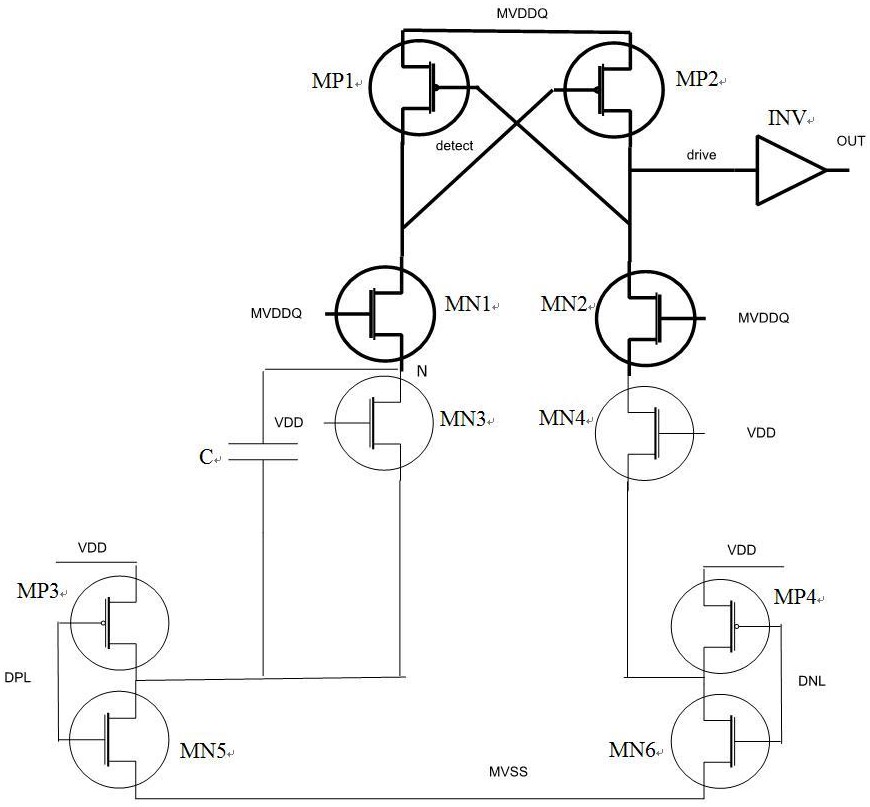

2、为解决上述技术问题,本发明提供了一种高速低功耗cmos电压转换电路,包括pmos管mp1~mp4、nmos管mn1~mn6;

3、pmos管mp1的源端和pmos管mp2的源端均接mvddq,pmos管mp1的漏端同时接pmos管mp2的栅端和nmos管mn1的漏端,pmos管mp2的漏端同时接pmos管mp1的栅端和nmos管mn2的漏端;

4、nmos管mn1的栅端和nmos管mn2的栅端均接mvddq,nmos管mn1的源端接nmos管mn3的漏端,nmos管mn3的源端同时接pmos管mp3的漏端和nmos管mn5的漏端,pmos管mp3的源端接vdd,栅端接信号dpl,nmos管mn5的源端接地mvss,栅端接dpl;

5、nmos管mn2的源端接nmos管mn4的漏端,nmos管mn4的源端同时接pmos管mp4的漏端和nmos管mn6的漏端,pmos管mp4的源端接vdd,栅端接信号dnl,nmos管mn6的源端接地mvss,栅端接dnl;nmos管mn3的栅端和nmos管mn4的栅端均接vdd。

6、在一种实施方式中,还包括反相器inv和电容c,反相器inv的输入端接pmos管mp2的漏端,输出端用电容c连接到nmos管mn1的源端和nmos管mn3的漏端之间。

7、在一种实施方式中,所述pmos管mp1~mp2、所述nmos管mn1~mn2是io mos器件;所述pmos管mp3~mp4、所述nmos管mn3~mn6是core mos器件;其中mvddq和vdd分别代表io电压和core电压。

8、在一种实施方式中,所述nmos管mn3和mn4为下拉管。

9、在一种实施方式中,所述电容c为前馈电容,容值为50ff。

10、在一种实施方式中,所述电容c用mom实现。

11、本发明提供的一种高速低功耗cmos电压转换电路,基于t22ulp的仿真表明本发明的电路即使在电压core=0.8v,io=1.8v的情况下可以达到12.5g的时钟频率,这个是传统电路远远没有办法达到的。而同等速度下的功耗也表明本发明远低于现有电路。电路完全兼容cmos工艺,没有增加任何mask也没有增加面积,因此完美的兼顾了高速,低功耗和低成本。先进制程中core的电压和io电压差距越来越大,而速度和功耗的要求越来越高,因此本发明的方案具有很大的使用价值。

技术特征:

1.一种高速低功耗cmos电压转换电路,其特征在于,包括pmos管mp1~mp4、nmos管mn1~mn6;

2.如权利要求1所述的高速低功耗cmos电压转换电路,其特征在于,还包括反相器inv和电容c,反相器inv的输入端接pmos管mp2的漏端,输出端用电容c连接到nmos管mn1的源端和nmos管mn3的漏端之间。

3.如权利要求1所述的高速低功耗cmos电压转换电路,其特征在于,所述pmos管mp1~mp2、所述nmos管mn1~mn2是io mos器件;所述pmos管mp3~mp4、所述nmos管mn3~mn6是coremos器件;其中mvddq和vdd分别代表io电压和core电压。

4.如权利要求1所述的高速低功耗cmos电压转换电路,其特征在于,所述nmos管mn3和mn4为下拉管。

5.如权利要求2所述的高速低功耗cmos电压转换电路,其特征在于,所述电容c为前馈电容,容值为50ff。

6.如权利要求5所述的高速低功耗cmos电压转换电路,其特征在于,所述电容c用mom实现。

技术总结

本发明公开一种高速低功耗CMOS电压转换电路,属于集成电路领域,包括PMOS管MP1~MP4、NMOS管MN1~MN6、反相器INV和电容C;所述PMOS管MP1~MP2、所述NMOS管MN1~MN2是IO MOS器件;所述PMOS管MP3~MP4、所述NMOS管MN3~MN6是core MOS器件。基于T22ULP的仿真表明本发明的电路即使在电压core=0.8V,IO=1.8V的情况下可以达到12.5G的时钟频率,这个是传统电路远远没有办法达到的。而同等速度下的功耗也表明本发明远低于现有电路。电路完全兼容CMOS工艺,没有增加任何MASK也没有增加面积,因此完美的兼顾了高速,低功耗和低成本。先进制程中core的电压和IO电压差距越来越大,而速度和功耗的要求越来越高,因此本发明的方案具有很大的使用价值。

技术研发人员:曾令刚,陈博宇,李晓慧

受保护的技术使用者:上海昇贻半导体科技有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!