半导体结构及半导体结构的制作方法与流程

本申请涉及半导体,尤其涉及一种半导体结构及半导体结构的制作方法。

背景技术:

1、现有vgaa(vertical gate all around)技术中,电容接触的主流设计为:利用曝光对准序列,仅在晶体管硅柱的顶部表面与电容金属接触。然而,由于硅柱的顶部表面的面积较小,导致硅柱与电容的接触电阻较大,影响器件性能。

技术实现思路

1、本申请的一个主要目的在于克服上述现有技术的至少一种缺陷,提供一种硅柱与电容的接触电阻较小的半导体结构。

2、本申请的另一个主要目的在于克服上述现有技术的至少一种缺陷,提供一种能够减小硅柱与电容的接触电阻的半导体结构的制作方法。

3、为实现上述目的,本申请采用如下技术方案:

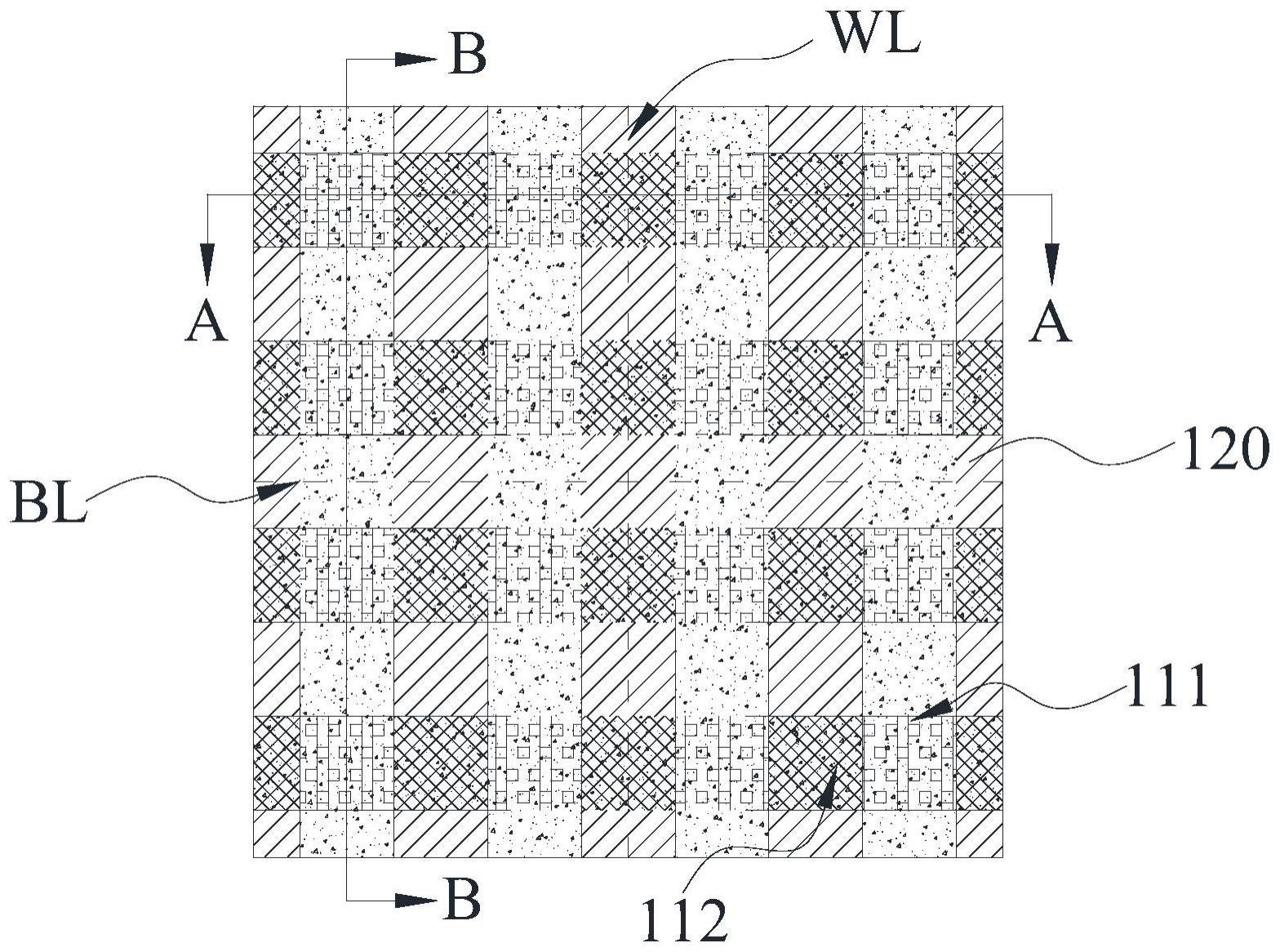

4、根据本申请的一个方面,提供一种半导体结构,包含衬底,所述衬底交叉布置有多条沟槽,使得所述衬底形成多个硅柱,所述沟槽中填充有隔离层;其中,所述硅柱顶部设置有导电层,所述导电层覆盖所述硅柱的顶面及邻接顶面的部分侧面,所述导电层用于与电容接触。

5、根据本申请的其中一个实施例,所述隔离层的顶面与所述导电层的顶面平齐。

6、根据本申请的其中一个实施例,所述隔离层的材质为氮化硅。

7、根据本申请的其中一个实施例,所述导电层的材质为氮化钛或者钨。

8、根据本申请的其中一个实施例,所述硅柱上环绕设置有环栅结构,所述环栅结构与所述硅柱之间设置有介质层。

9、根据本申请的其中一个实施例,所述介质层覆盖于所述硅柱的未被所述导电层覆盖的其余侧面。

10、根据本申请的其中一个实施例,所述介质层与所述导电层的厚度相等。

11、根据本申请的其中一个实施例,所述硅柱具有上部及下部,所述上部连接于所述下部的上端,且所述上部的尺寸小于所述下部的尺寸,所述环栅结构环绕设置于所述上部,并相间隔地位于所述导电层下方。

12、根据本申请的其中一个实施例,所述环栅结构的材质为氮化钛或者钨。

13、根据本申请的其中一个实施例,所述介质层的材质为氧化硅。

14、根据本申请的另一个方面,提供一种半导体结构的制作方法,其中,包含:提供衬底,所述衬底交叉布置有多条沟槽,使得所述衬底形成多个硅柱;形成隔离层,所述隔离层填充于所述沟槽,且所述隔离层的顶面显露于所述沟槽;去除所述硅柱的顶面及邻接顶面的部分侧面上的所述隔离层,在所述硅柱顶端周围形成凹痕;在所述衬底表面形成导电层,所述导电层覆盖所述硅柱的顶面及邻接顶面的部分侧面。

15、根据本申请的其中一个实施例,半导体结构的制作方法还包含:形成环栅结构及介质层,所述环栅结构环绕所述硅柱,所述环栅结构与所述硅柱之间设置有介质层,所述介质层覆盖所述硅柱的侧面和顶面并位于所述环栅结构与所述硅柱之间。

16、根据本申请的其中一个实施例,所述形成环栅结构、介质层及隔离层的步骤中,包含:在所述硅柱的顶面及侧面覆盖介质材料形成第一介质层;在所述沟槽中填充隔离材料形成第一隔离层;去除位于所述硅柱的顶面及邻接顶面的部分侧面的所述第一介质层;部分去除所述硅柱的未被所述第一介质层覆盖的侧面,并于所述硅柱的顶面及部分去除后的侧面形成第二介质层,所述第二介质层与所述第一隔离层具有间隙,剩余的所述第一介质层与所述第二介质层共同构成所述介质层;在所述间隙的下部空间中形成环绕所述硅柱的环栅结构;在所述间隙的上部空间中填充隔离材料形成第二隔离层,所述第一隔离层与所述第二隔离层共同构成所述隔离层。

17、根据本申请的其中一个实施例,在所述形成第二介质层的步骤之前,还包含对半导体结构进行清洗。

18、根据本申请的其中一个实施例,形成于所述硅柱的顶面的所述第二介质层的厚度,小于形成于所述硅柱的顶面的所述第一介质层的厚度,使得所述第一隔离层的顶部高于所述第二介质层的顶面;其中,所述去除所述硅柱的顶面及邻接顶面的部分侧面上的所述介质层的步骤之前,还包含研磨所述第一隔离层的顶部,使其与所述第二介质层的顶面平齐。

19、由上述技术方案可知,本申请提出的半导体结构及半导体结构的制作方法的优点和积极效果在于:

20、本申请提出的半导体结构在硅柱顶部设置导电层,导电层覆盖硅柱的顶面及邻接顶面的部分侧面,导电层用于与电容接触。通过上述设计,本申请能够利用导电层覆盖硅柱顶面及部分侧面的设计,增加硅柱与电容之间间接的电接触的接触面积,从而减小硅柱与电容之间的接触电阻,改善器件性能。

技术特征:

1.一种半导体结构,包含衬底,所述衬底交叉布置有多条沟槽,使得所述衬底形成多个硅柱,所述沟槽中填充有隔离层;其特征在于,所述硅柱顶部设置有导电层,所述导电层覆盖所述硅柱的顶面及邻接顶面的部分侧面,所述导电层用于与电容接触。

2.根据权利要求1所述的半导体结构,其特征在于,所述隔离层的顶面与所述导电层的顶面平齐。

3.根据权利要求1所述的半导体结构,其特征在于,所述隔离层的材质为氮化硅。

4.根据权利要求1所述的半导体结构,其特征在于,所述导电层的材质为氮化钛或者钨。

5.根据权利要求1所述的半导体结构,其特征在于,所述硅柱上环绕设置有环栅结构,所述环栅结构与所述硅柱之间设置有介质层。

6.根据权利要求5所述的半导体结构,其特征在于,所述介质层覆盖于所述硅柱的未被所述导电层覆盖的其余侧面。

7.根据权利要求6所述的半导体结构,其特征在于,所述介质层与所述导电层的厚度相等。

8.根据权利要求5所述的半导体结构,其特征在于,所述硅柱具有上部及下部,所述上部连接于所述下部的上端,且所述上部的尺寸小于所述下部的尺寸,所述环栅结构环绕设置于所述上部,并相间隔地位于所述导电层下方。

9.根据权利要求5所述的半导体结构,其特征在于,所述环栅结构的材质为氮化钛或者钨。

10.根据权利要求5所述的半导体结构,其特征在于,所述介质层的材质为氧化硅。

11.一种半导体结构的制作方法,其特征在于,包含:

12.根据权利要求11所述的半导体结构的制作方法,其特征在于,还包含:

13.根据权利要求12所述的半导体结构的制作方法,其特征在于,所述形成环栅结构、介质层及隔离层的步骤中,包含:

14.根据权利要求13所述的半导体结构的制作方法,其特征在于,在所述形成第二介质层的步骤之前,还包含对半导体结构进行清洗。

15.根据权利要求13所述的半导体结构的制作方法,其特征在于,形成于所述硅柱的顶面的所述第二介质层的厚度,小于形成于所述硅柱的顶面的所述第一介质层的厚度,使得所述第一隔离层的顶部高于所述第二介质层的顶面;其中,所述去除所述硅柱的顶面及邻接顶面的部分侧面上的所述介质层的步骤之前,还包含研磨所述第一隔离层的顶部,使其与所述第二介质层的顶面平齐。

技术总结

本申请提出一种半导体结构及半导体结构的制作方法,半导体结构包含衬底,衬底交叉布置有多条沟槽,使得衬底形成多个硅柱,沟槽中填充有隔离层;其中,硅柱顶部设置有导电层,导电层覆盖硅柱的顶面及邻接顶面的部分侧面,导电层用于与电容接触。通过上述设计,本申请能够利用导电层覆盖硅柱顶面及部分侧面的设计,增加硅柱与电容之间间接的电接触的接触面积,从而减小硅柱与电容之间的接触电阻,改善器件性能。

技术研发人员:张世明,文浚硕,肖德元,朴淳秉,金若兰

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!