高写入效率的反熔丝阵列的制作方法

本发明有关一种反熔丝晶体管,特别是关于一种高写入效率的反熔丝阵列。

背景技术:

1、反熔丝晶体管主要是以电容方式在两个导体间加入介电层,写入时在两端导体各加一偏压使该介电层崩溃而击穿,写入后反熔丝的电阻值会下降。随着集成电路的高速发展,元件尺寸日益缩小,近年来已发展出使用mos元件制作反熔丝晶体管,其写入方式是以闸极介电层崩溃机制为主。由于反熔丝晶体管基于闸极介电层的破裂以形成永久的导电路径,其局限在于必须施加足以使闸极介电层崩溃的电压。然而,传统的反熔丝晶体管中,反熔丝闸极于闸极介电层上方的交界处多呈平坦表面,其电荷密度会均匀分布,为了达成击穿闸极介电层的目的,因此需要高电压,相对也需要较高电流,且造成较大的元件面积。

2、本案申请人已提出一种低电压反熔丝元件及阵列,即中国台湾专利申请第109103372号。请参照图1,每一反熔丝记忆晶胞1的反熔丝闸极2设计成是由四个闸极介电层3所共用,使得反熔丝闸极2与闸极介电层3的交界处形成有尖角,以此利用尖端放电原理而降低击穿电压,减少电流消耗,同时可缩小元件面积。当进行写入操作时,将选择线sl1或sl2接地,来选择阵列中上排或下排的反熔丝记忆晶胞1,施加低压于位线bl1,并提供低压于字线wl1或wl2,来选择阵列中一排中特定的一个反熔丝记忆晶胞1,以击穿闸极介电层3。然而,此反熔丝阵列选取反熔丝记忆晶胞1来予以写入时,其他未选取的反熔丝记忆晶胞容易受到选取偏压影响,可能导致漏电流会经由位线bl1流到未选取的反熔丝记忆晶胞,且这样的源极架构不够稳定,进而提高成本需求;同时,其写入效率也有待提升。

技术实现思路

1、鉴于以上的问题,本发明的主要目的在于提供一种高写入效率的反熔丝阵列,其利用两个选择晶体管共用一个通道,增大了选择晶体管的通道宽度,也增加了写入效率,且利用源极接点共用的配置方式,来减少晶胞面积,稳固源极架构,进而降低成本;同时,本发明更可减少控制电压种类,避免漏电流的发生。

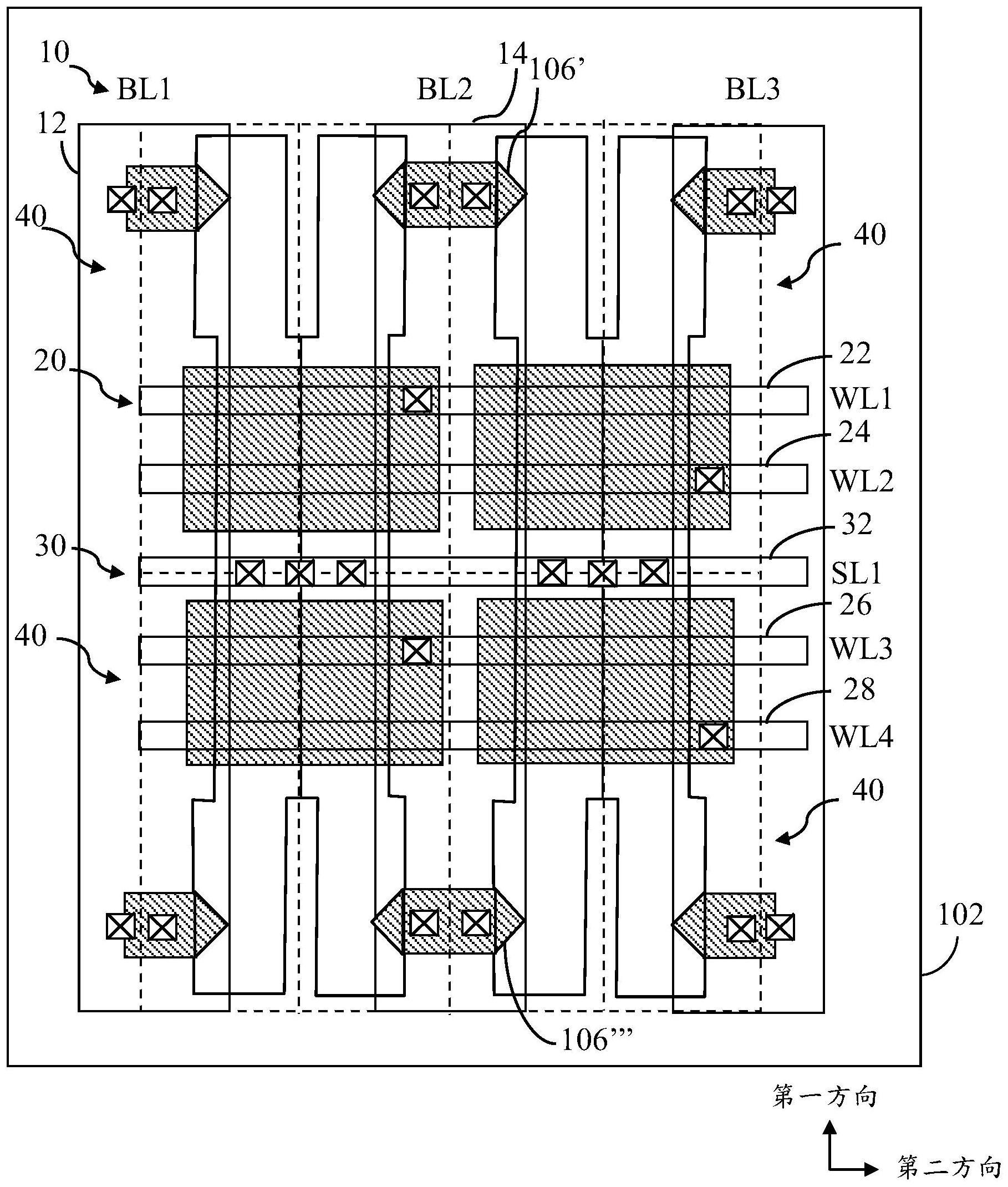

2、因此,为达上述目的,本发明提供一种高写入效率的反熔丝晶体管,包含多条平行的位线、字线、选择线以及至少一子存储器阵列。其中,位线在第一方向上延伸,并包含相邻的第一位线和第二位线;字线在不同于第一方向的第二方向上延伸,而与位线互相垂直,并包含第一字线;选择线在第二方向上延伸,而与字线互相平行,并包含第一选择线;而子存储器阵列包含第一和第二反熔丝记忆晶胞。第一反熔丝记忆晶胞包含第一反熔丝晶体管和第一选择晶体管,第一反熔丝晶体管连接第一位线,第一选择晶体管串联连接至第一反熔丝晶体管,并连接至第一字线及第一选择线。第二反熔丝记忆晶胞包含第二反熔丝晶体管和第二选择晶体管,第二反熔丝晶体管连接至第二位线,第二选择晶体管串联连接至第二反熔丝晶体管,并连接至第一字线及第一选择线。第一、第二反熔丝记忆晶胞在第二方向上彼此相邻,且位于第一位线和第二位线之间。

3、其中,第一反熔丝晶体管与第二反熔丝晶体管皆包括第一闸极介电层和反熔丝闸极。反熔丝闸极具有一个以上的尖角重叠于第一闸极介电层上;在一实施例中,反熔丝闸极与每个第一闸极介电层的重叠部分形成至少一个尖角,进行操作时,是通过电荷于尖端处的密度较高,以降低击穿电压,而可降低程序化反熔丝记忆晶胞的电流需求,同时可缩小元件面积。而第一选择晶体管与第二选择晶体管皆包括第二闸极介电层,每一第二闸极介电层彼此连接;在一实施例中,反熔丝闸极下方具有第一通道区,第一选择晶体管与第二选择晶体管共用第二通道区,第二通道区的宽度大于第一通道区的宽度。以此,可以增大选择晶体管的通道宽度,增加了写入效率,且没有增加整体布局面积。

4、以下通过具体实施例配合所附的图式详加说明,当更容易了解本发明的目的、技术内容、特点及其所达成的功效。

技术特征:

1.一种高写入效率的反熔丝阵列,其特征在于,包含:

2.根据权利要求1所述的高写入效率的反熔丝阵列,其特征在于,该反熔丝闸极下方具有一第一通道区,该第一选择晶体管与该第二选择晶体管共用一第二通道区,该第二通道区的宽度大于该第一通道区的宽度。

3.根据权利要求1所述的高写入效率的反熔丝阵列,其特征在于,该第一闸极介电层与该反熔丝闸极的重叠部分的形状为三角形。

4.根据权利要求1所述的高写入效率的反熔丝阵列,其特征在于,该第一闸极介电层与该反熔丝闸极的重叠部分为五边形,该五边形包括两条平行对边与从该两条平行对边延伸且相交的两条斜边。

5.根据权利要求1所述的高写入效率的反熔丝阵列,其特征在于,该第一反熔丝晶体管包含:

6.根据权利要求1所述的高写入效率的反熔丝阵列,其特征在于,该第二反熔丝晶体管包含:

7.根据权利要求5或6所述的高写入效率的反熔丝阵列,其特征在于,该基底为p型半导体基底,则该第二离子掺杂区与该第一离子掺杂区为n型掺杂区。

8.根据权利要求5或6所述的高写入效率的反熔丝阵列,其特征在于,该基底为n型半导体基底,则该第二离子掺杂区与该第一离子掺杂区为p型掺杂区。

技术总结

本发明公开一种高写入效率的反熔丝阵列,其包含至少一子存储器阵列,子存储器阵列具有并排配置于相邻的两条位线之间的两个反熔丝记忆晶胞,两个反熔丝记忆晶胞的反熔丝晶体管皆包含具有一个以上的尖角重叠于第一闸极介电层上的反熔丝闸极,且两个反熔丝记忆晶胞的选择晶体管的第二闸极介电层彼此连接,使得两个反熔丝记忆晶胞可连接到不同位线,并连接到相同选择线和相同字线。本发明利用源极接点共用及两个选择晶体管共用一个通道的配置方式,不但可稳固源极架构,同时可增大选择晶体管的通道宽度,而增加写入效率,且没有增加整体布局面积。

技术研发人员:黄郁婷,吴其沛

受保护的技术使用者:亿而得微电子股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!