半导体结构及其形成方法与流程

本发明涉及半导体制造,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、nand闪存是一种非易失性存储器,具有读写速度快、功耗低、存储密度高等优点,目前被广泛应用于电子产品中,如固态硬盘(ssd)、手机、数码相机等。进入21世纪以来,随着cpu主频以及io频率的不断提高,传统硬盘由于读写速度慢等原因已经成为pc、服务器存储等领域发展的瓶颈。由于基于nand flash的存储相比于传统硬盘存储具有体积小、读写速度快、抗震动强、温湿度适应范围宽等优点,nand闪存的市场份额正在迅速扩大,逐步取代传统硬盘。尤其在航天航空、国防军事等特殊的应用环境领域中,nand闪存已经成为存储设备的首选。

2、nand闪存向浮栅注入电荷的技术采用f-n隧道效应(fowler nordheimtunneling),nand闪存的编程和擦除电压很高(~22v),隧穿氧化层需要较高的电场(~10mv/cm)。因此,随着芯片尺寸下降,编程和擦除电压无法大幅地下降。随着器件尺寸降低,窄沟道的浅沟槽隔离(shallow-trench isolation,sti)的边缘处,由于电场密集、硼离子的严重聚集,导致窄宽度效应,使数据保存性能变差,硅中的阈值电压分布的均匀性变差。

3、因此,现有的nand闪存结构的性能有待进一步提高。

技术实现思路

1、本发明解决的技术问题是提供一种半导体结构及其形成方法,以提高形成的半导体结构的性能。

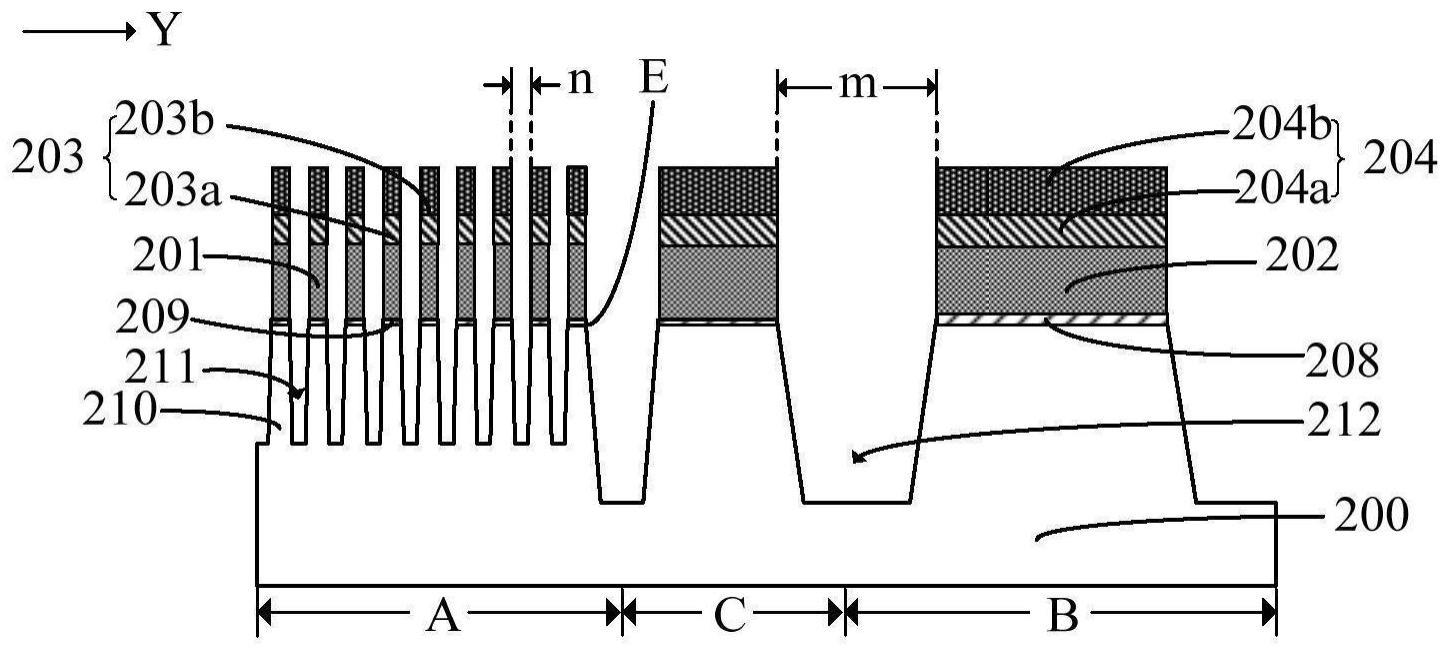

2、为解决上述技术问题,本发明技术方案提供一种半导体结构,包括:衬底,所述衬底包括存储区和与外围区;位于所述存储区内具有若干有源区和相邻有源区之间的第一沟槽,所述有源区的角部呈圆弧型;位于所述有源区顶部表面具有第一栅极层;位于部分所述外围区表面具有第二栅极层;位于所述第二栅极层两侧的外围区内具有若干第二沟槽。

3、可选的,包括:位于所述第一沟槽内具有第一隔离结构;位于所述第二沟槽内具有第二隔离结构。

4、可选的,所述第一栅极层沿第一方向延伸,且沿第二方向排列,所述第一方向与所述第二方向垂直。

5、可选的,所述第二栅极层沿第一方向延伸,且沿第二方向排列,在沿所述第二方向上,相邻的所述第二栅极层之间的具有第一距离值,相邻的所述第一栅极层之间具有第二距离值,所述第一距离值大于所述第二距离值。

6、相应地,本发明的技术方案还提供一种半导体结构的形成方法,包括:提供衬底,所述衬底包括存储区和与外围区;在部分所述存储区上形成第一栅极层,所述第一栅极层沿第一方向延伸,且沿第二方向排列,所述第一方向与所述第二方向垂直;在部分所述外围区上形成第二栅极层,所述第二栅极层沿第一方向延伸,且沿第二方向排列,在沿所述第二方向上,相邻的所述第二栅极层之间的具有第一距离值,相邻的所述第一栅极层之间具有第二距离值,所述第一距离值大于所述第二距离值;以所述第一栅极层和所述第二栅极层为掩膜,刻蚀所述衬底,在所述存储区内形成有源区和相邻有源区之间的第一沟槽,在所述外围区形成第二沟槽;在所述第一沟槽内形成第一隔离结构;在所述第二沟槽内形成第二隔离结构。

7、可选的,所述第一栅极层、所述第二栅极层的形成方法包括:在所述衬底上形成栅极材料层;在所述栅极材料层表面形成第一硬掩膜层,所述第一硬掩膜层暴露出部分所述存储区上的栅极材料层表面;在所述栅极材料层表面形成第二硬掩膜层,所述第二硬掩膜层暴露出部分所述外围区上的栅极材料层表面;以所述第一掩膜层刻蚀所述栅极材料层,形成所述第一栅极层;以所述第二掩膜层刻蚀所述栅极材料层,形成所述第二栅极层。

8、可选的,所述外围区包括高压区,所述第二栅极层位于部分所述高压区表面。

9、可选的,形成第一栅极层之前,还在所述存储区表面形成第一栅介质材料层;形成所述第二栅极层之前,还在所述高压区表面形成第二栅介质材料层,所述第二栅介质材料层的厚度大于所述第一栅介质材料层的厚度。

10、可选的,形成所述第一栅极层和所述第二栅极层后,且在形成所述第一沟槽和所述第二沟槽前,还包括:在所述存储区上形成光刻胶层,所述光刻胶层还位于所述第一栅极表面,所述光刻胶层暴露出所述高压区上的第二栅介质材料层和所述第二栅极层表面;以所述光刻胶层和所述第二栅极层为掩膜,刻蚀所述第二栅介质材料层,直到暴露出所述高压区表面,形成所述第二栅介质层;形成所述第二栅介质层后,去除所述光刻胶层。

11、可选的,在去除所述光刻胶后,且在形成所述第一沟槽前,还包括:以所述第一栅极层为掩膜刻蚀所述第一栅介质材料层,直到暴露出所述存储区表面,形成所述第一栅介质层。

12、可选的,所述第一栅介质材料层的厚度范围为65埃至75埃;所述第二栅介质材料层的厚度范围为350埃至460埃。

13、可选的,所述第一栅介质材料层的材料包括氧化硅;所述第二栅介质材料层的材料包括氧化硅。

14、可选的,所述外围区还包括低压区,所述第二栅极层还位于部分所述低压区表面。

15、可选的,刻蚀所述衬底的工艺为干法刻蚀工艺。

16、可选的,在沿所述第二方向上,所述第一距离值与所述第二距离值的比值范围为20:1至50:1。

17、现有技术相比,本发明实施例的技术方案具有以下有益效果:

18、本发明技术方案提供的半导体结构的形成方法中,以所述第一栅极层和所述第二栅极层为掩膜,刻蚀所述衬底,在所述存储区内形成有源区和相邻有源区之间的第一沟槽,在所述外围区形成第二沟槽,由于相邻的所述第二栅极层之间的具有第一距离值,相邻的所述第一栅极层之间具有第二距离值,所述第一距离值大于所述第二距离值,使所述第二栅极层暴露出的外围区表面的面积大于所述第一栅极层暴露出的存储区表面的面积,在刻蚀工艺的负载效应(loading effect)下,所述第二沟槽的深度大于所述第一沟槽的深度,因此可以采用一步光刻即可以形成所述第一沟槽和所述第二沟槽,所述第一沟槽的形成过程不需要光罩,避免了光刻胶材料的影响,有源区的角部在所述第一沟槽的刻蚀工艺中被刻蚀,可以提高所述角部的圆度,从而可有效地降低有源区角部在写入和擦除时的电场,减缓写入/擦除循环时栅氧化层的退化,提高先进闪存的写入/擦除循环耐久性和数据保留性能。

19、进一步,以所述光刻胶层和所述第二栅极层为掩膜,刻蚀所述第二栅介质材料层,直到暴露出所述高压区表面,形成所述第二栅介质层,所述刻蚀过程将高压区表面的第二栅介质材料层打开,避免了因第二栅介质材料层较厚影响后续第二沟槽的刻蚀深度。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,包括:位于所述第一沟槽内具有第一隔离结构;位于所述第二沟槽内具有第二隔离结构。

3.如权利要求1所述的半导体结构,其特征在于,所述第一栅极层沿第一方向延伸,且沿第二方向排列,所述第一方向与所述第二方向垂直。

4.如权利要求1所述的半导体结构,其特征在于,所述第二栅极层沿第一方向延伸,且沿第二方向排列,在沿所述第二方向上,相邻的所述第二栅极层之间的具有第一距离值,相邻的所述第一栅极层之间具有第二距离值,所述第一距离值大于所述第二距离值。

5.一种半导体结构的形成方法,其特征在于,包括:

6.如权利要求5所述的半导体结构形成方法,其特征在于,所述第一栅极层、所述第二栅极层的形成方法包括:在所述衬底上形成栅极材料层;在所述栅极材料层表面形成第一硬掩膜层,所述第一硬掩膜层暴露出部分所述存储区上的栅极材料层表面;在所述栅极材料层表面形成第二硬掩膜层,所述第二硬掩膜层暴露出部分所述外围区上的栅极材料层表面;以所述第一掩膜层刻蚀所述栅极材料层,形成所述第一栅极层;以所述第二掩膜层刻蚀所述栅极材料层,形成所述第二栅极层。

7.如权利要求5所述的半导体结构形成方法,其特征在于,所述外围区包括高压区,所述第二栅极层位于部分所述高压区表面。

8.如权利要求7所述的半导体结构形成方法,其特征在于,形成第一栅极层之前,还在所述存储区表面形成第一栅介质材料层;形成所述第二栅极层之前,还在所述高压区表面形成第二栅介质材料层,所述第二栅介质材料层的厚度大于所述第一栅介质材料层的厚度。

9.如权利要求8所述的半导体结构形成方法,其特征在于,形成所述第一栅极层和所述第二栅极层后,且在形成所述第一沟槽和所述第二沟槽前,还包括:在所述存储区上形成光刻胶层,所述光刻胶层还位于所述第一栅极表面,所述光刻胶层暴露出所述高压区上的第二栅介质材料层和所述第二栅极层表面;以所述光刻胶层和所述第二栅极层为掩膜,刻蚀所述第二栅介质材料层,直到暴露出所述高压区表面,形成所述第二栅介质层;形成所述第二栅介质层后,去除所述光刻胶层。

10.如权利要求9所述的半导体结构形成方法,其特征在于,在去除所述光刻胶后,且在形成所述第一沟槽前,还包括:以所述第一栅极层为掩膜刻蚀所述第一栅介质材料层,直到暴露出所述存储区表面,形成所述第一栅介质层。

11.如权利要求8所述的半导体结构形成方法,其特征在于,所述第一栅介质材料层的厚度范围为65埃至75埃;所述第二栅介质材料层的厚度范围为350埃至460埃。

12.如权利要求8所述的半导体结构形成方法,其特征在于,所述第一栅介质材料层的材料包括氧化硅;所述第二栅介质材料层的材料包括氧化硅。

13.如权利要求7所述的半导体结构形成方法,其特征在于,所述外围区还包括低压区,所述第二栅极层还位于部分所述低压区表面。

14.如权利要求5所述的半导体结构形成方法,其特征在于,刻蚀所述衬底的工艺为干法刻蚀工艺。

15.如权利要求5所述的半导体结构形成方法,其特征在于,在沿所述第二方向上,所述第一距离值与所述第二距离值的比值范围为20:1至50:1。

技术总结

一种半导体结构及其形成方法,其方法包括:在部分所述存储区上形成第一栅极层,所述第一栅极层沿第一方向延伸,且沿第二方向排列,所述第一方向与所述第二方向垂直;在所述外围区上形成第二栅极层,所述第二栅极层沿第一方向延伸,且沿第二方向排列,在沿所述第二方向上,相邻的所述第二栅极层之间的具有第一距离值,相邻的所述第一栅极层之间具有第二距离值,所述第一距离值大于所述第二距离值;以所述第一栅极层和所述第二栅极层为掩膜,刻蚀所述衬底,在所述存储区内形成有源区和相邻有源区之间的第一沟槽,在所述外围区形成第二沟槽,有源区的角部在所述第一沟槽的刻蚀工艺中被刻蚀,可以提高有源区角部的圆度,提高先进闪存的数据保留性能。

技术研发人员:李勇,谈晋椹,代洪刚

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!