半导体结构的形成方法与流程

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构的形成方法。

背景技术:

1、随着超大规模集成电路的发展趋势,集成电路特征尺寸持续减小,人们对 集成电路的封装技术的要求相应也不断提高。现有的封装技术包括球栅阵列封 装(ball gridarray,bga)、芯片尺寸封装(chip scale package,csp)、晶圆级封 装(wafer levelpackage,wlp)、三维封装(3d)和系统封装(sip)等。

2、在进行封装的整个工艺流程中,集成电路中包含巨大数量的半导体元件。 随着半导体器件制造技术的进一步发展,半导体器件之间的高性能、高密度连 接不仅在单个互连层中进行,而且要在多层之间进行互连。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体结构的形成方法,有利于提高 半导体结构的性能。

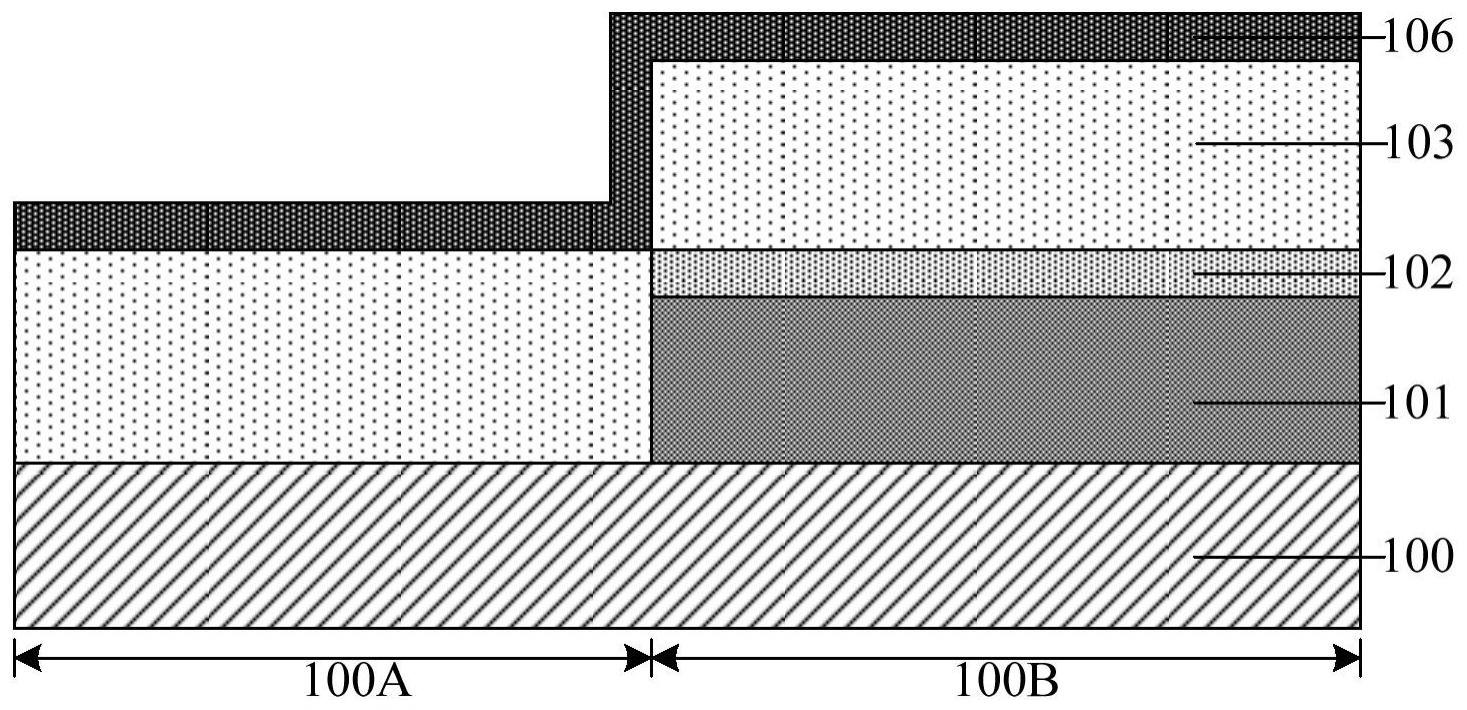

2、为解决上述问题,本发明实施例还提供一种半导体结构的形成方法,包括: 提供衬底,所述衬底包括工作区和互连区,所述工作区的所述衬底上形成有器 件结构;在所述器件结构的顶部、以及所述互连区的所述衬底的顶部形成互连 层,所述互连区的互连层与所述器件结构电连接;在所述互连区的所述互连层 的顶部形成保护层;形成所述保护层之后,去除所述器件结构顶部的所述互连 层;去除所述器件结构顶部的所述互连层之后,去除所述保护层。

3、与现有技术相比,本发明实施例的技术方案具有以下优点:

4、本发明实施例提供一种半导体结构的形成方法,在所述互连区的所述互连 层的顶部形成保护层,所述保护层能对所述互连区的互连层的顶面起到保护作 用,在后续去除所述器件结构顶部的互连层的工艺过程中,所述保护层使得所 述互连层的顶面不易与相关湿法工艺所采用的溶液相接触,相应的,也就降低 了在所述互连层的顶面出现聚集析出现象的概率,同时,也降低了在互连层中 出现空洞的概率,从而提高了所述互连层顶面形貌的完整性,进而提高了所述 半导体结构的性能,同时,通过后续对工作区进行减薄处理的工艺中去除保护 层,简化了工艺流程。

技术特征:

1.一种半导体结构的形成方法,其特征在于,包括:

2.如权利要求1所述的半导体结构的形成方法,其特征在于,去除所述器件结构顶部的所述互连层的步骤包括:在所述互连区的所述保护层的顶部形成掩膜层;以所述掩膜层为掩膜,去除所述器件结构顶部的所述互连层;去除所述器件结构顶部的所述互连层之后,去除所述掩膜层。

3.如权利要求1或2所述的半导体结构的形成方法,其特征在于,在所述互连区的所述互连层的顶部形成保护层的步骤中,所述保护层还形成在所述工作区的所述互连层的顶部;

4.如权利要求1所述的半导体结构的形成方法,其特征在于,采用干法刻蚀工艺,去除所述保护层。

5.如权利要求1所述的半导体结构的形成方法,其特征在于,所述提供衬底的步骤中,所述器件结构的顶部还形成有钝化层;

6.如权利要求5所述的半导体结构的形成方法,其特征在于,所述形成方法还包括:进行钝化层减薄处理,去除部分厚度的所述钝化层;

7.如权利要求6所述的半导体结构的形成方法,其特征在于,所述钝化层减薄处理的步骤包括:以无掩膜方式,刻蚀所述保护层和钝化层。

8.如权利要求1所述的半导体结构的形成方法,其特征在于,去除所述器件结构顶部的所述互连层的工艺包括干法刻蚀工艺。

9.如权利要求2所述的半导体结构的形成方法,其特征在于,所述掩膜层的材料包括光刻胶、旋涂碳和旋涂玻璃中的一种或多种。

10.如权利要求2所述的半导体结构的形成方法,其特征在于,去除所述掩膜层的工艺包括湿法工艺或者干法刻蚀工艺。

11.如权利要求6所述的半导体结构的形成方法,其特征在于,进行钝化层减薄处理的步骤中,去除的所述钝化层的厚度与去除的所述保护层的厚度比值为850:800至1200:1000。

12.如权利要求1所述的半导体结构的形成方法,其特征在于,形成所述保护层的步骤中,所述保护层的厚度为100埃至1000埃。

13.如权利要求1所述的半导体结构的形成方法,其特征在于,所述保护层的材料为钛、氮化钛、氮化铝和钼中的一种或多种。

14.如权利要求5所述的半导体结构的形成方法,其特征在于,所述钝化层的材料为氮化硅、氧化硅和磷硅玻璃中的一种或多种。

15.如权利要求1所述的半导体结构的形成方法,其特征在于,所述互连层的材料包括cu、alcu合金、au和sncu合金中的一种或多种。

16.如权利要求1所述的半导体结构的形成方法,其特征在于,所述器件结构包括smr、fbar和saw滤波器中的一种或多种。

技术总结

一种半导体结构的形成方法,形成方法包括:提供衬底,所述衬底包括工作区和互连区,所述工作区的所述衬底上形成有器件结构;在所述器件结构的顶部、以及所述互连区的所述衬底的顶部形成互连层,所述互连区的互连层与所述器件结构电连接;在所述互连区的所述互连层的顶部形成保护层;形成所述保护层之后,去除所述器件结构顶部的所述互连层;去除所述器件结构顶部的所述互连层之后,去除所述保护层。所述保护层降低了在所述互连层的顶面出现聚集析出现象的概率,同时,也降低了在互连层中出现空洞的概率,从而提高了所述互连层顶面形貌的完整性,进而提高了所述半导体结构的性能。

技术研发人员:时亚南,齐飞

受保护的技术使用者:中芯集成电路(宁波)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!