延迟锁定环电路以及测量延迟锁定环电路的延迟的方法与流程

本公开涉及一种延迟锁定环电路,尤其涉及一种延迟锁定环电路以及能够准确测量延迟锁定环电路的延迟的测量延迟的方法。

背景技术:

1、延迟锁定环(delay locked loop,dll)电路是一种用于在输入参考时钟与源自dll输出且通常通过dll外部的反馈路径反馈到dll反馈时钟输入的时钟之间提供相位对准的电路。驱动反馈路径的dll输出是输入参考时钟的受控缓冲版本,且dll电路通过调整dll内部的缓冲器(dll延迟线)的延迟来进行操作,直到dll输入处实现相位对准。

2、在包括例如存储器等dll电路的电子装置中,必须测量的关键参数是dll电路周围的延迟。此延迟通常被设计成对从存储器芯片边沿到存储器阵列的信号路径中的元件的延迟进行匹配。使用dll电路,基本上可移除这些延迟且可在系统中的期望点之间提供相位对准。准确地确定dll的延迟以调节存储器的操作是重要的。

技术实现思路

1、本公开介绍一种延迟锁定环(dll)电路及可准确测量dll电路周围的延迟的方法。

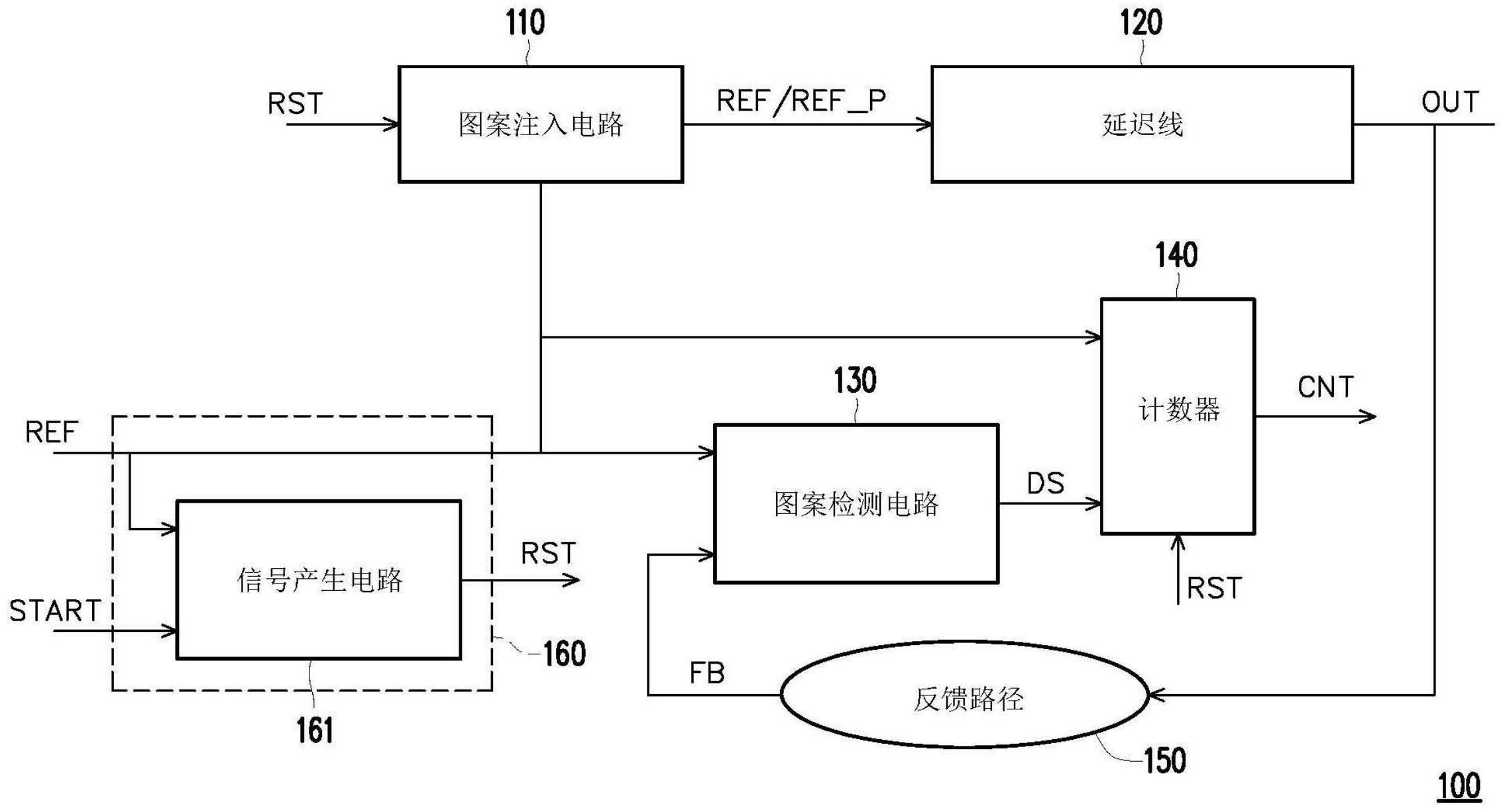

2、在一些实施例中,所述dll电路包括延迟线、图案注入电路、图案检测电路及计数器。所述延迟线被配置成将参考时钟信号的相位与反馈时钟信号的相位对准。所述图案注入电路耦合到所述延迟线且被配置成将预定图案注入到所述参考时钟信号以产生注入参考时钟信号。所述图案注入电路可将所述注入参考时钟信号置位(assert)到所述延迟线。所述图案检测电路耦合到所述延迟线且被配置成检测所述反馈时钟信号中的所述预定图案。所述计数器耦合到所述图案检测电路且被配置成根据所述注入参考时钟信号被置位到所述延迟线时的第一定时以及在所述反馈时钟信号中检测到所述预定图案时的第二定时来确定所述延迟锁定环电路的延迟。

3、在一些实施例中,所述测量dll电路的延迟的方法包括以下步骤:将参考时钟信号置位到所述延迟锁定环电路的延迟线,其中所述延迟线被配置成将所述参考时钟信号的相位与反馈时钟信号的相位对准;将预定图案注入到所述参考时钟信号,以产生注入参考时钟信号;将所述注入参考时钟信号置位到所述延迟线;检测所述反馈时钟信号中的所述预定图案;以及根据所述注入参考时钟信号被置位到所述延迟线时的第一定时以及在所述反馈时钟信号中检测到所述预定图案时的第二定时来确定所述延迟锁定环电路的所述延迟。

4、根据本公开的实施例,可在延迟线被校准且dll电路处于锁定状态之后执行dll延迟的测量。这样一来,所测量的dll反映在dll电路的正常工作期间看到的延迟且实现具有高准确度的dll延迟的测量。另外,由于dll延迟的测量是基于向参考时钟信号注入预定图案及在反馈时钟信号中检测到预定图案来执行,因此测量可在不扰乱系统环境的情况下在任何时间执行。

技术特征:

1.一种测量延迟锁定环电路的延迟的方法,包括:

2.根据权利要求1所述的方法,其中将所述预定图案注入到所述参考时钟信号以产生所述注入参考时钟信号包括:

3.根据权利要求2所述的方法,其中

4.根据权利要求2所述的方法,其中

5.根据权利要求2所述的方法,其中

6.根据权利要求2所述的方法,还包括:

7.根据权利要求1所述的方法,其中检测所述反馈时钟信号中的所述预定图案包括:

8.根据权利要求1所述的方法,其中基于从所述注入参考时钟信号被供应到所述延迟线时的所述第一定时到在所述反馈时钟信号中检测到所述预定图案时的所述第二定时的时间周期来确定所述延迟锁定环电路的所述延迟包括:

9.根据权利要求8所述的方法,其中从所述第一定时到所述第二定时对所述参考时钟信号的所述时钟循环数目进行计数包括:

10.一种延迟锁定环电路,包括:

11.根据权利要求10所述的延迟锁定环电路,其中

12.根据权利要求11所述的延迟锁定环电路,其中

13.根据权利要求11所述的延迟锁定环电路,其中

14.根据权利要求11所述的延迟锁定环电路,其中

15.根据权利要求11所述的延迟锁定环电路,其中

16.根据权利要求11所述的延迟锁定环电路,还包括:

17.根据权利要求16所述的延迟锁定环电路,其中

18.根据权利要求10所述的延迟锁定环电路,其中所述图案检测电路包括边沿检测电路,所述边沿检测电路被配置成:

19.根据权利要求18所述的延迟锁定环电路,其中所述计数器包括:

20.根据权利要求19所述的延迟锁定环电路,其中

技术总结

本发明提供一种延迟锁定环电路以及测量延迟锁定环电路的延迟的方法,介绍一种包括延迟线、图案注入电路、图案检测电路及计数器的延迟锁定环(DLL)电路。所述延迟线可将参考时钟信号的相位与反馈时钟信号的相位对准。所述图案注入电路将预定图案注入到参考时钟信号以产生注入参考时钟信号且将注入参考时钟信号置位到延迟线。所述图案检测电路检测反馈时钟信号中的预定图案。计数器根据所述注入参考时钟信号被置位到延迟线时的第一定时以及在反馈时钟信号中检测到预定图案时的第二定时来确定延迟锁定环电路的延迟。还介绍一种测量DLL电路的延迟的方法。

技术研发人员:约翰·奥斯汀,约瑟夫·伊丹萨,弗兰·凯瑟

受保护的技术使用者:南亚科技股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!