形成微电子装置的方法及相关的微电子装置、存储器装置及电子系统与流程

在各个实施例中,本公开大体上涉及微电子装置设计及制造领域。更具体来说,本公开涉及形成微电子装置的方法,且涉及相关微电子装置、存储器装置、电子系统及额外方法。

背景技术:

1、微电子装置设计者通常期望通过减小个别特征的尺寸及通过减小邻近特征之间的分离距离来增加微电子装置内的特征的集成水平或密度。另外,微电子装置设计者通常期望设计不仅紧凑而且提供性能优势以及简化设计的架构。

2、微电子装置的一个实例是存储器装置。存储器装置通常被提供为计算机或其它电子装置中的内部集成电路。存在许多类型的存储器装置,包含但不限于非易失性存储器装置(例如,nand快闪存储器装置)。一种增加非易失性存储器装置中的存储器密度的方式是利用垂直存储器阵列(也称为“三维(3d)存储器阵列”)架构。常规垂直存储器阵列包含延伸穿过包含导电结构及介电材料的阶层的一或多个层叠(例如,堆叠结构)中的开口的垂直存储器串。每一垂直存储器串可包含串联耦合到垂直堆叠存储器单元的串联组合的至少一个选择装置。如与具有晶体管的常规平面(例如,二维)布置的结构相比,此配置通过在裸片上向上(例如,垂直)建构阵列而允许更多数目个开关装置(例如,晶体管)定位于一个单位的裸片区域(即,所消耗有源表面的长度及宽度)中。

3、下伏于或上覆于存储器装置(例如,非易失性存储器装置)的存储器阵列的所述存储器装置的控制逻辑区内的控制逻辑装置已用来控制对所述存储器装置的存储器单元的操作(例如,存取操作、读取操作、写入操作、擦除操作)。可以布线及互连结构的方式提供与存储器阵列的存储器单元电连通的控制逻辑装置的组合件。然而,用于在控制逻辑区上方形成存储器阵列的处理条件(例如,温度、压力、材料)及/或设计可限制控制逻辑区内的控制逻辑装置的配置及性能;或用于在存储器阵列的水平边界外部形成控制逻辑区的处理条件及/或设计可限制存储器阵列的特征的配置及性能。另外,常规存储器装置配置还可为复杂且制造成本高,可阻碍存储器装置的大小(例如,水平占据面积)的减小,及/或可阻碍所述存储器装置的性能的改进(例如,较快存储器单元通/断速度、较低阈值开关电压要求、较快数据传送速率、较低功耗)。

技术实现思路

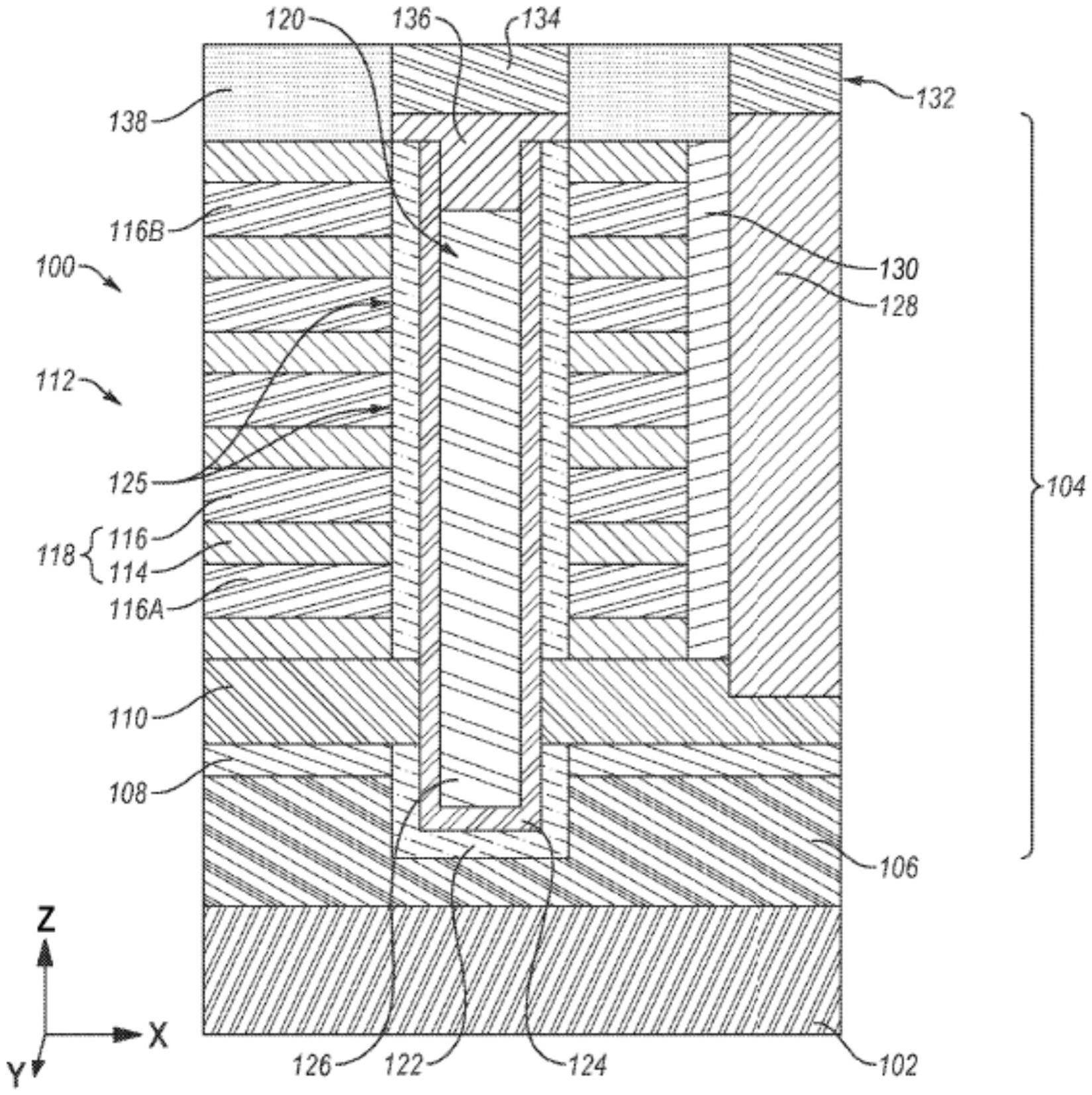

1、在一些实施例中,一种微电子装置包括堆叠结构、单元支柱结构、有源主体结构、数字线结构及控制逻辑装置。所述堆叠结构包括垂直邻近阶层,所述垂直邻近阶层中的每一者包括导电结构及垂直邻近所述导电结构的绝缘结构。所述单元支柱结构垂直延伸穿过所述堆叠结构且各自包括沟道材料及水平插置于所述沟道材料与所述堆叠结构之间的外材料堆叠。所述有源主体结构垂直上覆于所述堆叠结构且与所述单元支柱结构的所述沟道材料接触。所述有源主体结构包括具有大于或等于约4.7电子伏特的功函数的金属材料。所述数字线结构垂直下伏于所述堆叠结构且经耦合到所述单元支柱结构。

2、在额外实施例中,一种形成微电子装置的方法包括形成包括控制逻辑装置的第一微电子装置结构。形成第二微电子装置结构以包括:基底结构;掺杂半导电材料,其上覆于所述基底结构;堆叠结构,其上覆于所述掺杂半导电材料且包括垂直交替的导电结构与绝缘结构;单元支柱结构,其垂直延伸穿过所述堆叠结构且到所述掺杂半导电材料中,所述单元支柱结构各自包括由外材料堆叠环绕的半导电沟道材料;及数字线结构,其垂直上覆于所述堆叠结构且经耦合到所述单元支柱结构。将所述第二微电子装置结构附接到所述第一微电子装置结构以形成微电子装置结构组合件,所述数字线结构垂直插置于所述微电子装置结构组合件内所述堆叠结构与所述控制逻辑装置之间。移除所述基底结构以及所述掺杂半导电材料及所述单元支柱结构的所述外材料堆叠的部分以暴露所述单元支柱结构的所述半导电沟道材料的部分。在所述单元支柱结构的所述半导电沟道材料的所述经暴露部分上形成金属材料,所述金属材料具有大于或等于约4.7电子伏特的功函数。

3、在进一步实施例中,一种存储器装置包括存储器阵列区及垂直下伏于所述存储器阵列区的控制逻辑区。所述存储器阵列区包括堆叠结构、横向接触结构、有源主体结构、数字线结构及单元支柱结构。所述堆叠结构包括导电结构与绝缘结构的垂直交替序列。所述横向接触结构上覆于所述堆叠结构。所述有源主体结构上覆于所述横向接触结构且包括具有大于或等于约4.7电子伏特的功函数的金属材料。所述数字线结构下伏于所述堆叠结构。所述单元支柱结构从所述有源主体结构的所述金属材料垂直延伸,穿过所述横向接触结构及所述堆叠结构,且到所述数字线结构。所述单元支柱结构中的每一者包括与所述有源主体结构的所述金属材料、所述横向接触结构及所述数字线结构中的一者接触的半导电沟道材料。所述控制逻辑区包括与所述有源主体结构、所述横向接触结构、所述数字线结构及所述堆叠结构的所述导电结构电连通的cmos电路系统。

4、在又进一步实施例中,一种电子系统包括:输入装置;输出装置;处理器装置,其可操作地耦合到所述输入装置及所述输出装置;及存储器装置,其可操作地耦合到所述处理器装置。所述存储器装置包括堆叠结构、有源主体结构、横向接触结构、数字线、单元支柱结构及控制逻辑电路系统。所述堆叠结构包括阶层,每一阶层包括导电结构及垂直邻近所述导电结构的绝缘结构。所述有源主体结构上覆于所述堆叠结构且包括具有大于或等于4.7电子伏特的功函数的导电材料。所述横向接触结构包括插置于所述堆叠结构与所述有源主体结构之间的额外导电材料。所述数字线下伏于所述堆叠结构。所述单元支柱结构延伸穿过堆叠结构且与所述有源主体结构、所述横向接触结构及所述数字线接触。所述单元支柱结构中的每一者包括接触所述有源主体结构的所述导电材料的半导电材料以在所述半导电材料与所述导电材料之间的结处形成肖特基接触件。所述控制逻辑电路系统下伏于所述数字线且电连接到所述数字线、所述横向接触结构及所述有源主体结构。

技术特征:

1.一种微电子装置,其包括:

2.根据权利要求1所述的微电子装置,其进一步包括垂直插置于所述有源主体结构与所述堆叠结构之间的横向接触结构,所述横向接触结构与所述单元支柱结构的所述沟道材料接触。

3.根据权利要求2所述的微电子装置,其中所述横向接触结构包括与所述单元支柱结构的所述沟道材料的外侧表面直接物理接触的导电材料。

4.根据权利要求2所述的微电子装置,其进一步包括深接触结构,所述深接触结构包括从所述横向接触结构垂直延伸且完全穿过所述堆叠结构的导电材料。

5.根据权利要求2所述的微电子装置,其进一步包括垂直插置于所述源极结构与所述横向接触结构之间的介电材料,所述介电材料与所述单元支柱结构的所述外材料堆叠接触。

6.根据权利要求2所述的微电子装置,其中所述有源主体结构进一步包括垂直插置于所述金属材料与所述横向接触结构之间的掺杂半导电材料。

7.根据权利要求6所述的微电子装置,其中所述有源主体结构的所述金属材料的部分从所述掺杂半导电材料的侧表面及所述单元支柱结构的所述沟道材料的侧表面且在其之间水平延伸。

8.根据权利要求1至7中任一权利要求所述的微电子装置,其中所述单元支柱结构的所述沟道材料包括半导电材料,所述单元支柱结构的所述沟道材料与所述有源主体结构的所述金属材料之间的结形成肖特基接触件。

9.根据权利要求1至7中任一权利要求所述的微电子装置,其中所述有源主体结构的所述金属材料物理接触所述单元支柱结构的所述沟道材料的上表面及外侧表面。

10.一种形成微电子装置的方法,其包括:

11.根据权利要求10所述的方法,其中形成所述第二微电子装置结构包括:形成所述第二微电子装置结构以进一步包括垂直位于所述堆叠结构与所述掺杂半导电材料之间的导电横向接触结构,所述导电横向接触结构水平延伸穿过所述单元支柱结构中的每一者的所述外材料堆叠且接触所述单元支柱结构中的每一者的所述半导电沟道材料。

12.根据权利要求10所述的方法,其中将所述第二微电子装置结构附接到所述第一微电子装置结构包括:

13.根据权利要求10至12中任一权利要求所述的方法,其中移除所述基底结构以及所述掺杂半导电材料及所述单元支柱结构的所述外材料堆叠的部分包括:

14.根据权利要求13所述的方法,其中蚀刻所述单元支柱结构的所述外材料堆叠的经暴露部分包括:暴露所述单元支柱结构的所述半导电沟道材料的上表面及侧表面的上部分。

15.根据权利要求10至12中任一权利要求所述的方法,其进一步包括形成所述单元支柱结构中的每一者的所述外材料堆叠以包括:

16.根据权利要求10至12中任一权利要求所述的方法,其中形成包括控制逻辑装置的第一微电子装置结构包括:形成所述控制逻辑装置以包括互补金属氧化物半导体(cmos)电路系统。

17.根据权利要求10至12中任一权利要求所述的方法,其中形成第二微电子装置结构包括:选择所述掺杂半导电材料以在相互暴露于湿式蚀刻剂期间具有相对低于所述基底结构的蚀刻速率。

18.一种存储器装置,其包括:

19.根据权利要求18所述的存储器装置,其中:

20.根据权利要求18及19中一个权利要求所述的存储器装置,其中所述有源主体结构进一步包括下伏于所述金属材料的导电掺杂半导电材料。

21.根据权利要求20所述的存储器装置,其中:

22.根据权利要求18及19中一个权利要求所述的存储器装置,其中所述单元支柱结构的所述半导电沟道材料包括具有小于或等于约1e17个掺杂剂原子/立方厘米的掺杂剂浓度的至少一种导电掺杂半导电材料。

23.根据权利要求18及19中一个权利要求所述的存储器装置,其中所述单元支柱结构的所述半导电沟道材料包括具有大于约1e17个掺杂剂原子/立方厘米的掺杂剂浓度的至少一种导电掺杂半导电材料。

24.一种电子系统,其包括:

25.根据权利要求24所述的电子系统,其中所述存储器装置包括3d nand快闪存储器装置。

技术总结

一种微电子装置包括堆叠结构、单元支柱结构、有源主体结构、数字线结构及控制逻辑装置。所述堆叠结构包括垂直邻近阶层,所述垂直邻近阶层中的每一者包括导电结构及垂直邻近所述导电结构的绝缘结构。所述单元支柱结构垂直延伸穿过所述堆叠结构且各自包括沟道材料及水平插置于所述沟道材料与所述堆叠结构之间的外材料堆叠。所述有源主体结构垂直上覆于所述堆叠结构且与所述单元支柱结构的所述沟道材料接触。所述有源主体结构包括具有大于或等于约4.7电子伏特的功函数的金属材料。所述数字线结构垂直下伏于所述堆叠结构且经耦合到所述单元支柱结构。还描述存储器装置、电子系统及形成微电子装置的方法。

技术研发人员:刘海涛,K·R·帕雷克

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!