包括可变形层和压电层的用于MEMS应用的复合结构及相关制造方法与流程

本发明涉及微电子和微系统领域。本发明尤其涉及一种复合结构,该复合结构包括压电层和具有弹性特性的单晶半导体层,该单晶半导体层能够在至少一个空腔上方变形。本发明还涉及制造复合结构的方法。

背景技术:

1、在微机电系统(mems)和致动器领域中,衬底和部件通常包括置于可变形层上的薄压电层;后者具有允许其以空腔上方的可移动膜的形式移动或变形的弹性特性。应当注意,术语膜在这里是广义使用的,并且包括密封或有孔的膜、梁(beam)或能够弯曲和/或变形的任何其它形式的膜。可变形层为膜提供机械强度,而压电层引起或检测膜的变形。这个概念也扩展到声波滤波器领域。

2、薄膜压电材料-特别是pzt(锆钛酸铅)-通常对侵蚀性外部环境敏感,因此如果长时间暴露于侵蚀性外部环境,则易于降解。例如,这可以是诸如麦克风、扬声器或压电微加工超声换能器(pmut)的传感器或致动器的情况。因此,在制造方法中有必要提供在压电层上沉积保护膜的附加步骤,以便将该压电层与外部环境隔离,但不影响其性能。

3、此外,再次考虑由pzt制成的压电层的示例,如果要实现良好的质量水平,则这种易于沉积的材料需要在约700℃的温度下的再结晶步骤。对于某些应用,包括必须在其上沉积压电层的可变形层的衬底可以证明与这样的温度不兼容:例如,如果该衬底包括玻璃或塑料载体,或者即使该衬底包括诸如晶体管的部件。

4、发明目的

5、本发明涉及现有技术的替代解决方案,并且旨在补救上述缺点中的全部或一些。本发明尤其涉及一种复合结构,该复合结构包括压电层和具有弹性特性的单晶半导体层,该单晶半导体层能够在至少一个空腔上方变形。本发明还涉及制造该复合结构的方法。

技术实现思路

1、本发明涉及一种复合结构,该复合结构包括:

2、-受体衬底,所述受体衬底包括限定在所述受体衬底中并且没有固体材料或填充有牺牲固体材料的至少一个空腔,

3、-置于所述受体衬底上的单晶半导体层,所述单晶半导体层在所述结构的整个范围上具有自由表面以及介于0.1微米至100微米之间的厚度,

4、-压电层,所述压电层被牢固地固定到所述单晶半导体层并置于所述单晶半导体层与所述受体衬底之间。

5、在根据本发明的符合结构中,所述单晶半导体层的至少一部分用于当所述空腔没有固体材料时或在所述牺牲固体材料已经被去除之后在所述空腔(31)上方形成可移动膜,并且所述压电层用于引起或检测所述可移动膜的变形。

6、根据本发明的其他有利和非限制性特征,其可以单独实施或以任何技术上可行的组合实施:

7、·所述压电层包括选自以下的材料:铌酸锂(linbo3)、钽酸锂(litao3)、铌酸钾钠(kxna1-xnbo3或knn)、钛酸钡(batio3)、石英、锆钛酸铅(pzt)、铌酸铅镁和钛酸铅的化合物(pmn-pt)、氧化锌(zno)、氮化铝(aln)和铝钪氮化物(alscn);

8、·压电层的厚度小于10微米,优选地小于5微米;

9、·所述单晶半导体层由硅或碳化硅制成;

10、·所述压电层被放置成仅面向所述受体衬底的所述至少一个空腔;

11、·所述压电层被放置成面向所述受体衬底的至少一个空腔,并且在所述至少一个空腔之外牢固地固定到所述受体衬底。

12、本发明还涉及一种基于空腔上方的可移动膜的器件,所述器件由前述复合结构形成,并且包括与压电层接触的至少两个电极,其中:

13、-所述空腔没有固体材料,

14、-并且所述单晶半导体层的至少一部分在所述空腔上方形成所述可动膜。

15、本发明最后涉及一种用于制造复合结构的方法,该方法包括以下步骤:

16、a)提供包括单晶半导体层的供体衬底,所述单晶半导体层被限制在所述供体衬底的正面与所述供体衬底中的掩埋的弱化平面之间,所述单晶半导体层具有介于0.1微米至100微米之间的厚度,

17、b)提供受体衬底,所述受体衬底包括限定在所述受体衬底中并且开口到所述受体衬底的正面上的至少一个空腔,所述至少一个空腔没有固体材料或填充有牺牲固体材料,

18、c)形成压电层,使得所述压电层被放置在所述供体衬底的正面上和/或受体衬底的正面上,

19、d)经由所述供体衬底和所述受体衬底各自的正面接合所述供体衬底和所述受体衬底,

20、e)使单晶半导体层沿着所述掩埋的弱化平面从所述供体衬底的剩余部分断裂,以便形成包括所述单晶半导体层、所述压电层和所述受体衬底的复合结构。

21、根据本发明的其他有利和非限制性特征,其可以单独实施或以任何技术上可行的组合实施:

22、·通过将轻物质植入所述供体衬底中来形成所述掩埋的弱化平面,并且经由热处理和/或经由施加机械应力获得沿着所述掩埋的弱化平面的断裂;

23、·所述掩埋的弱化平面由接合能低于0.7j/m2的界面形成;

24、·所述制造方法包括在步骤c)之前和/或之后形成金属电极的步骤,使得所述电极与压电层接触;

25、·步骤c)包括:当在所述供体衬底的所述正面上形成所述压电层时,对所述压电层进行局部蚀刻,以便在步骤d)的接合步骤结束时保持所述压电层仅面向所述至少一个空腔。

技术特征:

1.一种复合结构(100),所述复合结构(100)包括:

2.根据权利要求1所述的复合结构(100),其中,所述压电层(2)包括选自以下的材料:铌酸锂(linbo3)、钽酸锂(litao3)、铌酸钾钠(kxna1-xnbo3或knn)、钛酸钡(batio3)、石英、锆钛酸铅(pzt)、铌酸铅镁和钛酸铅的化合物(pmn-pt)、氧化锌(zno)、氮化铝(aln)和铝钪氮化物(alscn)。

3.根据前述权利要求中任一项所述的复合结构(100),其中,所述压电层(2)的厚度小于10微米,并且优选地小于5微米。

4.根据前述权利要求中任一项所述的复合结构(100),其中,所述单晶半导体层(1)由硅或碳化硅制成。

5.根据前述权利要求中任一项所述的复合结构(100),其中,所述压电层(2)被放置成仅面向所述受体衬底(3)的所述至少一个空腔(31)。

6.根据权利要求1至4中任一项所述的复合结构(100),其中,所述压电层(2)被放置成面向所述受体衬底(3)的所述至少一个空腔(31),并且在所述至少一个空腔(31)之外牢固地固定到所述受体衬底(3)。

7.一种基于空腔(31)上方的可移动膜(50)的器件(150),所述器件由根据前述权利要求中任一项所述的复合结构(100)形成,并且包括与所述压电层(2)接触的至少两个电极(21,22),其中:

8.一种根据权利要求1至6中任一项所述的复合结构(100)的制造方法,所述制造方法包括以下步骤:

9.根据权利要求8所述的制造方法,其中,通过将轻物质植入所述供体衬底(10)中来形成所述掩埋的弱化平面(11),并且经由热处理和/或经由施加机械应力获得沿着所述掩埋的弱化平面(11)的断裂。

10.根据权利要求8所述的制造方法,其中,所述掩埋的弱化平面(11)由接合能低于0.7j/m2的界面形成。

11.根据权利要求8至10中任一项所述的制造方法,所述制造方法包括在步骤c)之前和/或之后形成金属电极(21,22)的步骤,使得所述电极与所述压电层(2)接触。

12.根据权利要求8至11中任一项所述的制造方法,其中,步骤c)包括:当在所述供体衬底(10)的所述正面(10a)上形成所述压电层(2)时,对所述压电层(2)进行局部蚀刻,以便在步骤d)的接合步骤结束时保持所述压电层(2)仅面向所述至少一个空腔(31)。

技术总结

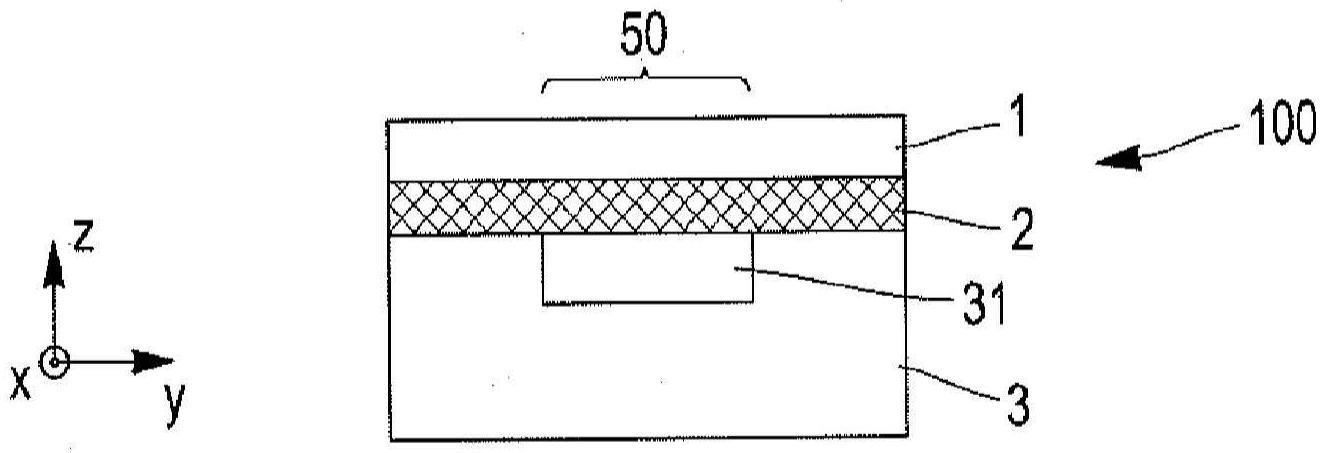

本公开涉及一种复合结构(100),该复合结构包括:-受体衬底(3),其具有限定在所述衬底中并且没有固体材料或填充有牺牲固体材料的至少一个空腔(31);-置于所述受体衬底(3)上的单晶半导体层(1),所述层在所述结构的整个范围上具有自由表面以及介于0.1微米至100微米之间的厚度,-压电层(2),其固定到所述单晶半导体层(1)并置于所述单晶半导体层(1)与所述受体衬底(3)之间。本公开还涉及一种基于能够在空腔(31)上方移动的膜(50)并由复合结构(100)形成的器件。本公开最后涉及制造所述复合结构的方法。

技术研发人员:布鲁诺·吉瑟兰,F-X·达尔拉斯

受保护的技术使用者:索泰克公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!