半导体电路的制作方法

本公开涉及一种半导体电路。

背景技术:

1、从生态学的观点来看,期望电子设备具有低电力消耗。例如,对于半导体电路,所谓的功率门控技术通常被使用,其中通过选择性地停止对一些电路的电力供应来降低电力消耗。期望以这种方式停止电力供应的电路紧接在电力供应重新启动之后返回到电力供应尚未停止的操作状态。实现这样的短时间返回操作的一种方法是在电路中并入非易失性存储器。非易失性存储器的示例包括mtj(磁隧道结)元件。

2、要注意,例如在专利文献1和2中公开了非易失性存储器被并入的半导体电路。

3、引文列表

4、专利文献

5、ptl 1:日本未审查专利申请公开no.2019-50068

6、ptl 2:日本未审查专利申请公开no.2017-197486

技术实现思路

1、顺便提及,在并入了非易失性存储器的半导体电路中,由于某种原因,在休眠时间期间保持的数据可能被反转,在一些情况下导致错误数据。因此,期望提供高度容错的半导体电路。

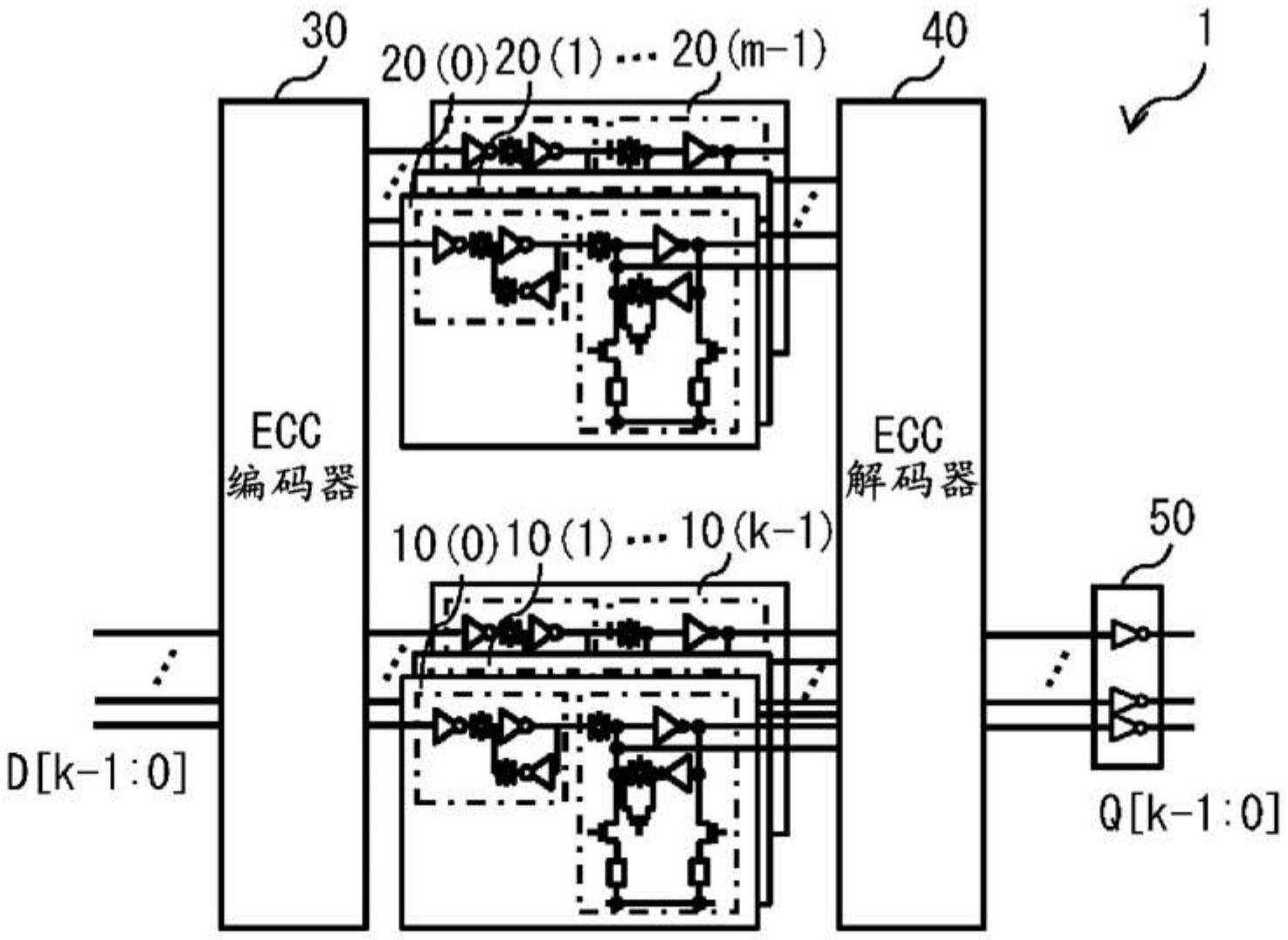

2、根据本公开的实施例的半导体电路包括存储k位数据和针对k位数据的m位纠错数据的非易失性的锁存电路。

3、根据本公开的实施例的半导体电路包括存储k位数据和针对k位数据的m位纠错数据的非易失性的锁存电路。这使得在电力供应停止之后、当电力供应重新启动时可以返回到电力供应尚未停止的操作状态。此外,即使在电力供应停止期间(在休眠时间期间)由于某种原因保持的数据变为错误数据的情况下,也可以通过纠错以正确的数据返回到电力供应尚未停止的操作状态。

技术特征:

1.一种半导体电路,包括

2.根据权利要求1所述的半导体电路,其中

3.根据权利要求2所述的半导体电路,还包括

4.根据权利要求3所述的半导体电路,还包括

5.根据权利要求1所述的半导体电路,其中

6.根据权利要求5所述的半导体电路,还包括

7.根据权利要求6所述的半导体电路,还包括

8.根据权利要求2所述的半导体电路,还包括

9.根据权利要求8所述的半导体电路,还包括

10.根据权利要求9所述的半导体电路,其中所述k个主锁存电路各自包括选择器,所述选择器向所述k个主锁存电路反馈通过由所述ecc解码器执行的解码而生成的k位解码数据或所述k位数据中的任一个。

11.根据权利要求9所述的半导体电路,还包括

12.根据权利要求2所述的半导体电路,其中第一非易失性的从锁存电路中的每一个和第二非易失性的从锁存电路中的每一个各自包括保持1位数据的非易失性的存储器。

13.根据权利要求5所述的半导体电路,其中第一非易失性的从锁存电路中的每一个和第二非易失性的从锁存电路中的每一个各自包括保持1位数据的非易失性的存储器。

14.根据权利要求8所述的半导体电路,其中第一非易失性的从锁存电路中的每一个和第二非易失性的从锁存电路中的每一个各自包括保持1位数据的非易失性的存储器。

15.根据权利要求8所述的半导体电路,其中当从ff操作经由存储操作、休眠操作和恢复操作返回到所述ff操作时,所述ecc解码器通过使用从设置在所述k个第一非易失性的从锁存电路中的每一个中的非易失性的存储器读取的所述k位数据、以及从设置在所述m个第二非易失性的从锁存电路中的每一个中的非易失性的存储器读取的所述m位纠错数据,在所述存储操作、所述休眠操作和所述恢复操作中的任一个中执行ecc检查。

技术总结

根据本公开的一方面的半导体电路包括存储k位数据和针对k位数据的m位纠错数据的非易失性的锁存电路。

技术研发人员:阪井垒,神田泰夫,濑上雅博,平贺启三

受保护的技术使用者:索尼半导体解决方案公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!