一种自校准比较器电路、工作方法、集成电路和电子设备与流程

本申请涉及集成电路,具体而言,涉及一种自校准比较器电路、工作方法、集成电路和电子设备。

背景技术:

1、比较器使用广泛,是最常见的电路之一。在很多应用中,如信号识别、电机控制等,对比较器的延迟特性有着较为严格的要求,尤其是比较器的上升延迟和下降延迟,希望尽可能的保持一致。但由于受到工艺偏差等因素的影响,而比较器输出级的上拉能力和下拉能力会出现差异,这样的差异,会导致其输出信号与输入信号相比,上升延迟和下降延迟有所不同。

2、例如,用比较器去比较某一输入信号,理想比较器的上升延迟和下降延迟一致,因此理想输出信号的高电平时间和低电平时间不会发生改变。

3、如果比较器输出级的上拉能力强于下拉能力,上升延迟就会小于下降延迟,导致输出信号的高电平时间被扩大。在一些应用中,该现象会导致问题的出现,比如,在使用比较器进行信号识别时,如果比较器的上升延迟和下降延迟有较大差异,就有可能导致识别出的信号占宽比发生较大的变化,从而无法满足信号的时序要求。

技术实现思路

1、本申请提供一种自校准比较器电路、工作方法、集成电路和电子设备,可自动校准比较器的上升延迟和下降延迟,使它们保持一致,并选择上升延迟和下降延迟中最小的延迟作为校准值。

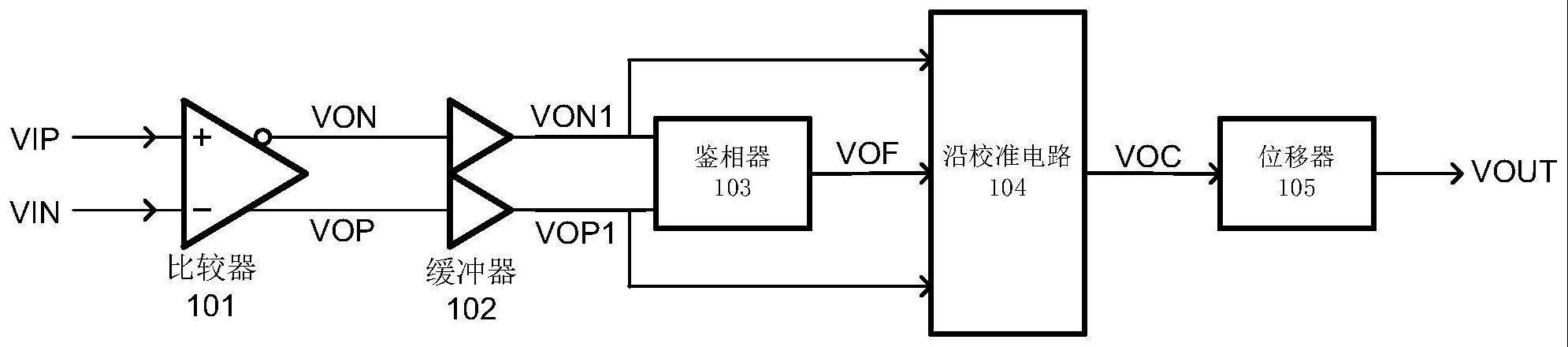

2、根据本申请的一方面,提供一种自校准比较器电路,包括:比较器,将输入信号差分输出为第一信号和第二信号;缓冲器,将所述第一信号和所述第二信号整形输出为第三信号和第四信号;鉴相器,检测所述第三信号和所述第四信号的相位差,并根据所述相位差输出校准信号;沿校准电路,将所述第三信号和所述第四信号转换为第五信号,并且使所述第五信号的上升沿或下降沿对准所述校准信号的下降沿。

3、根据一些实施例,所述第一信号和所述第二信号振幅相同、相位相反。

4、根据一些实施例,所述第一信号和所述第二信号存在上升延迟和下降延迟,且所述第一信号和所述第二信号的上升延迟和下降延迟存在差异。

5、根据一些实施例,所述第三信号和所述第四信号的上升延迟和下降延迟与所述第一信号和所述第二信号的上升延迟和下降延迟相同,且存在所述相位差。

6、根据一些实施例,所述校准信号的高电平或低电平为所述相位差。

7、根据一些实施例,所述校准信号的脉冲宽度为所述第一信号和所述第二信号的上升延迟和下降延迟的时间差。

8、根据一些实施例,所述沿校准电路,在所述校准信号处于低电平时工作;在所述校准信号处于高电平时保持之前的状态。

9、根据一些实施例,所述第五信号为单端信号且所述第五信号的上升延迟和下降延迟相等。

10、根据一些实施例,所述第五信号的上升延迟和下降延迟均为所述第一信号和所述第二信号的上升延迟和下降延迟中的较大值。

11、根据一些实施例,所述比较器电路还包括:位移器,对所述第五信号的周期进行校准,并输出为输出信号。

12、根据一些实施例,所述位移器将所述第一信号和所述第二信号的上升延迟和下降延迟中的较小值为所述输出信号相对于所述输入信号的校准值。

13、根据本申请的一方面,提供一种自校准比较器电路的工作方法,包括:将输入信号差分输出为第一信号和第二信号;将所述第一信号和所述第二信号整形输出为第三信号和第四信号;检测所述第三信号和所述第四信号的相位差,并根据所述相位差输出校准信号;将所述第三信号和所述第四信号转换为第五信号,并校准所述第五信号的上升延迟和下降延迟;调整所述第五信号的周期并输出为输出信号。

14、根据一些实施例,调整所述第五信号的周期并输出为输出信号,包括:将所述第五信号的上升沿和下降沿提前一个所述校准信号的脉冲宽度,生成所述输出信号。

15、根据本申请的一方面,提供一种集成电路,包括如前所述的比较器电路。

16、根据本申请的一方面,提供一种电子设备,包括如前所述的比较器电路或前述的集成电路。

17、根据本申请的实施例,可通过沿校准电路将比较器输出的上升延迟和下降延迟自动校准并且保持一致,并通过位移器选择最小延迟作为校准值,使得输出信号可满足相应的时序要求。

18、应当理解的是,以上的一般描述和后文的细节描述仅是示例性的,并不能限制本申请。

技术特征:

1.一种自校准比较器电路,其特征在于,包括:

2.根据权利要求1所述的电路,其特征在于,所述第一信号和所述第二信号振幅相同、相位相反。

3.根据权利要求1所述的电路,其特征在于,所述第一信号和所述第二信号存在上升延迟和下降延迟,且所述第一信号和所述第二信号的上升延迟和下降延迟存在差异。

4.根据权利要求1所述的电路,其特征在于,所述第三信号和所述第四信号的上升延迟和下降延迟与所述第一信号和所述第二信号的上升延迟和下降延迟相同,且存在所述相位差。

5.根据权利要求1所述的电路,其特征在于,所述校准信号的高电平或低电平为所述相位差。

6.根据权利要求1所述的电路,其特征在于,所述校准信号的脉冲宽度为所述第一信号和所述第二信号的上升延迟和下降延迟的时间差。

7.根据权利要求1所述的电路,其特征在于,所述沿校准电路,

8.根据权利要求1所述的电路,其特征在于,所述第五信号为单端信号且所述第五信号的上升延迟和下降延迟相等。

9.根据权利要求8所述的电路,其特征在于,所述第五信号的上升延迟和下降延迟均为所述第一信号和所述第二信号的上升延迟和下降延迟中的较大值。

10.根据权利要求1所述的电路,其特征在于,还包括:

11.根据权利要求10所述的电路,其特征在于,所述位移器将所述第一信号和所述第二信号的上升延迟和下降延迟中的较小值作为所述输出信号相对于所述输入信号的校准值。

12.一种自校准比较器电路的工作方法,其特征在于,包括:

13.根据权利要求12所述的方法,其特征在于,调整所述第五信号的周期并输出为输出信号,包括:

14.一种集成电路,其特征在于,包括如权利要求1-11中任一项所述的比较器电路。

15.一种电子设备,其特征在于,包括如权利要求1-11中任一项所述的比较器电路或如权利要求14所述的集成电路。

技术总结

本申请提供一种自校准比较器电路、工作方法、集成电路和电子设备,涉及集成电路技术领域。一种自校准比较器电路,包括:比较器,将输入信号差分输出为第一信号和第二信号;缓冲器,将所述第一信号和所述第二信号整形输出为第三信号和第四信号;鉴相器,检测所述第三信号和所述第四信号的相位差,并根据所述相位差输出校准信号;沿校准电路,将所述第三信号和所述第四信号转换为第五信号,并且使所述第五信号的上升沿和下降沿分别对准所述校准信号的下降沿。根据本申请实施例的比较器电路,可自动校准上升延迟和下降延迟,并使上升延迟和下降延迟保持一致。

技术研发人员:张弛,赵辉

受保护的技术使用者:国民技术股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!