小面积侧边电容只读存储器元件及其阵列与操作方法与流程

本发明有关一种存储器阵列,特别是关于一种小面积侧边电容只读存储器元件及其阵列与操作方法。

背景技术:

1、互补式金属氧化半导体制程技术已成为特殊应用集成电路的常用制造方法。在计算机信息产品发达的今天,闪存与电子式可清除程序化只读存储器由于皆具备有电性编写和抹除数据的非挥发性存储器功能,且在电源关掉后数据不会消失,所以被广泛使用于电子产品上。

2、非挥发性存储器为可程序化的,其用以储存电荷以改变存储器的晶体管的闸极电压,或不储存电荷以留下原存储器的晶体管的闸极电压。抹除操作则是将储存在非挥发性存储器中的电荷移除,使得非挥发性存储器回到原存储器的晶体管之闸极电压。对于目前的非挥发存储器,其电路图与电路布局图分别如图1与图2所示,非挥发性存储器是由许多记忆晶胞所组成的一种存储器,图中每一个记忆晶胞包含了晶体管10与电容12,每两个相邻的位元组的记忆晶胞间会设有两条位元线,如此便会增加面积成本。而图3为每一个记忆晶胞的结构剖视图,由图可知,电容12设于晶体管10的一侧,由于这样的结构,同样会造成大面积,进而提高成本需求。

3、因此,本案针对上述现有技术的缺失,特别研发一种小面积侧边电容只读存储器元件及其阵列,并进而提出基于此架构的低电流低电压的操作方法,可同时复写大量记忆晶胞。

技术实现思路

1、本发明的主要目的在于提供一种小面积侧边电容只读存储器元件及其阵列与操作方法,使用导电闸极与介电层重叠的边缘产生电容效应,并通过多指状布局方式,可以有效缩小电路布局的面积,来达到最高的电容值,从而减少只读存储器的整体面积,以及实现高效率的读写。

2、本发明的另一目的在于提供一种小面积侧边电容只读存储器元件及其阵列与操作方法,于具有小面积的只读存储器架构下,利用特殊的偏压方式,达成大量记忆晶胞写入及抹除的功能。

3、为达上述目的,本发明提供一种小面积侧边电容只读存储器元件,其是在半导体基底中设置有场效晶体管和电容。场效晶体管包括第一介电层、第一导电闸极及多个第一离子掺杂区,第一介电层位于半导体基底表面,第一导电闸极叠设于第一介电层上,第一离子掺杂区位于第一导电闸极的两侧下方的半导体基底内,分别作为汲极和源极。电容包括第二介电层、第二导电闸极及第二离子掺杂区,第二介电层位于半导体基底表面,第二导电闸极与第一导电闸极连接并叠设于第二介电层上,第二离子掺杂区与第一离子掺杂区掺杂有同型的离子,并位于第二介电层一侧,且第二导电闸极具有一条状部和数个相互平行的指状部,每一指状部的一端连接于条状部且由条状部朝外延伸。

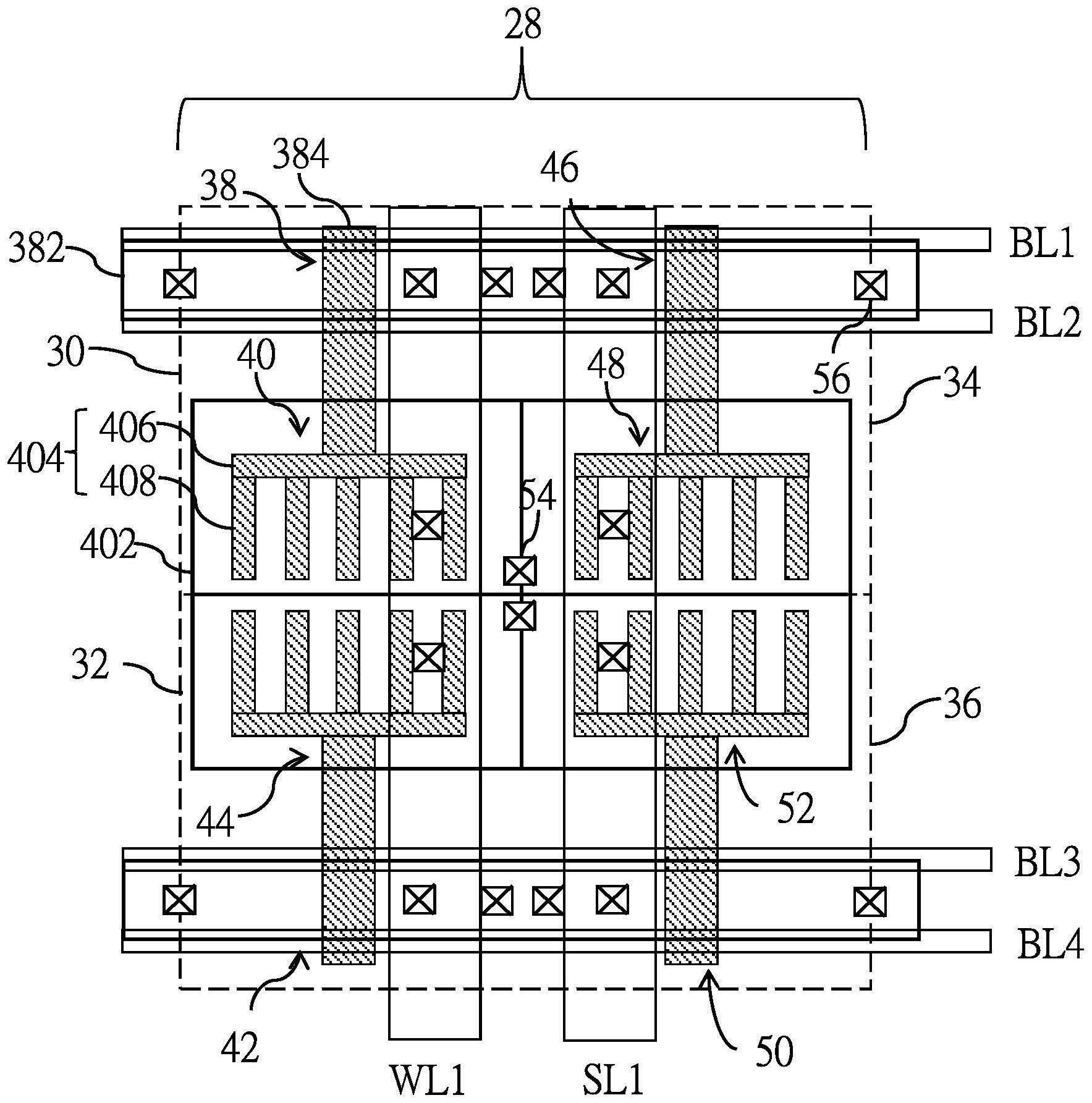

4、本发明也提供一种小面积侧边电容只读存储器阵列,其包含复数条平行的位元线、字线与共源线,此些位元线区分为复数组位元线,其包含第一组位元线与第二组位元线,且字线与位元线互相垂直,并包含第一字线,共源线与字线互相平行,并包含第一共源线。另有复数子存储器阵列,每一子存储器阵列连接两组位元线、一字线与一共源线,每一子存储器阵列包含一第一、第二、第三、第四记忆晶胞。第一记忆晶胞连接第一组位元线、第一共源线与第一字线,第二记忆晶胞连接第二组位元线、第一共源线与第一字线,第一、第二记忆晶胞互相对称配置,并位于第一共源线的同一侧。第三记忆晶胞连接第一组位元线、第一共源线与第一字线,并以第一共源线为轴与第一记忆晶胞对称配置。第四记忆晶胞连接第二组位元线、第一共源线与第一字线,并以第一共源线为轴与第二记忆晶胞对称配置,又第三、第四记忆晶胞互相对称配置,且与第一、第二记忆晶胞位于第一共源线的相异两侧。其中,第一、第二、第三、第四记忆晶胞皆包含上述的小面积侧边电容只读存储器元件。

5、且基于上述的小面积侧边电容只读存储器阵列,当第一、第二、第三、第四记忆晶胞皆包含n型场效晶体管时,本发明提供一种小面积侧边电容只读存储器阵列的操作方法,其中第一、第二、第三、第四记忆晶胞皆作为操作记忆晶胞,在选取所有操作记忆晶胞进行操作时,通过于所有操作记忆晶胞连接的半导体基底施加基底电压vsub,且于所有操作记忆晶胞连接的位元线、字线、共源线分别施加位电压vb、字电压vw、共源电压vs,来进行写入或抹除。其中,于写入时,使满足vsub=接地,vs=vb=0,且vw=高压(hv)的条件;于抹除时,使满足vsub=接地,vs=vb=高压,且vw=浮接的条件。

6、另外,当第一、第二、第三、第四记忆晶胞皆包含p型场效晶体管时,本发明也提供另一种小面积侧边电容只读存储器阵列的操作方法,在选取所有操作记忆晶胞进行操作时,通过于所有操作记忆晶胞连接的半导体基底施加基底电压vsub,且于所有操作记忆晶胞连接的位元线、字线、共源线分别施加位电压vb、字电压vw、共源电压vs,来进行写入或抹除。其中,于写入时,使满足vsub=高压,vw=0,且vs=vb=高压的条件;于抹除时,使满足vsub=高压,vw=浮接,且vs=vb=0的条件。

7、以下通过具体实施例配合所附的图式详加说明,当更容易了解本发明的目的、技术内容、特点及其所达成的功效。

技术特征:

1.一种小面积侧边电容只读存储器元件,其特征在于,包含:

2.如权利要求1所述的小面积侧边电容只读存储器元件,其特征在于,该场效晶体管为n型晶体管,该复数个第一离子掺杂区及该第二离子掺杂区为n型掺杂区,且该半导体基底为p型半导体基底或是具有p型井的半导体基底。

3.如权利要求1所述的小面积侧边电容只读存储器元件,其特征在于,该场效晶体管为p型晶体管,该复数个第一离子掺杂区及该第二离子掺杂区为p型掺杂区,且该半导体基底为n型半导体基底或是具有n型井的半导体基底。

4.一种小面积侧边电容只读存储器阵列,其特征在于,包含:

5.如权利要求4所述的小面积侧边电容只读存储器阵列,其特征在于,每一该子存储器阵列位于相邻的两组该位元线之间。

6.如权利要求4所述的小面积侧边电容只读存储器阵列,其特征在于,该第一记忆晶胞、该第二记忆晶胞、该第三记忆晶胞及该第四记忆晶胞皆连接该第一字线,以共用同一接点。

7.如权利要求4所述的小面积侧边电容只读存储器阵列,其特征在于,该第一组位元线包含两条该位元线,其分别连接该第一记忆晶胞及该第三记忆晶胞,且该第二组位元线亦包含两条该位元线,其分别连接该第二记忆晶胞及该第四记忆晶胞。

8.如权利要求7所述的小面积侧边电容只读存储器阵列,其特征在于,相邻的两个该子存储器阵列中,两个该第三记忆晶胞彼此相邻且连接同一位元线,以共用同一接点,两个该第四记忆晶胞彼此相邻且连接同一位元线,以共用同一接点。

9.如权利要求4所述的小面积侧边电容只读存储器阵列,其特征在于,该场效晶体管为n型晶体管,该复数个第一离子掺杂区及该第二离子掺杂区为n型掺杂区,且该半导体基底为p型半导体基底或是具有p型井的半导体基底。

10.如权利要求4所述的小面积侧边电容只读存储器阵列,其特征在于,该场效晶体管为p型晶体管,该复数个第一离子掺杂区及该第二离子掺杂区为p型掺杂区,且该半导体基底为n型半导体基底或是具有n型井的半导体基底。

11.一种小面积侧边电容只读存储器阵列的操作方法,该小面积侧边电容只读存储器阵列包含:复数条平行的位元线,区分为复数组位元线,该复数组位元线包含一第一组位元线与一第二组位元线;复数条平行的字线,与该复数条位元线互相垂直,并包含一第一字线;复数条平行的共源线,与该复数条字线互相平行,并包含一第一共源线;及复数子存储器阵列,每一该子存储器阵列连接两组该位元线、一该字线与一该共源线,每一该子存储器阵列包含:一第一记忆晶胞,连接该第一组位元线、该第一共源线与该第一字线;一第二记忆晶胞,连接该第二组位元线、该第一共源线与该第一字线,该第一记忆晶胞与该第二记忆晶胞互相对称配置,并位于该第一共源线的同一侧;一第三记忆晶胞,连接该第一组位元线、该第一共源线与该第一字线,并以该第一共源线为轴与该第一记忆晶胞对称配置;及一第四记忆晶胞,连接该第二组位元线、该第一共源线与该第一字线,并以该第一共源线为轴与该第二记忆晶胞对称配置,又该第三记忆晶胞与该第四记忆晶胞互相对称配置,且与该第一记忆晶胞、该第二记忆晶胞位于该第一共源线的相异两侧,其中,该第一记忆晶胞、该第二记忆晶胞、该第三记忆晶胞及该第四记忆晶胞皆包含位于一半导体基底中的一n型场效晶体管与一电容;

12.如权利要求11所述的小面积侧边电容只读存储器阵列的操作方法,其特征在于,每一该子存储器阵列位于相邻的两组该位元线之间。

13.如权利要求11所述的小面积侧边电容只读存储器阵列的操作方法,其特征在于,该第一记忆晶胞、该第二记忆晶胞、该第三记忆晶胞及该第四记忆晶胞皆连接该第一字线,以共用同一接点。

14.如权利要求11所述的小面积侧边电容只读存储器阵列的操作方法,其特征在于,该第一组位元线包含两条该位元线,其分别连接该第一记忆晶胞及该第三记忆晶胞,且该第二组位元线亦包含两条该位元线,其分别连接该第二记忆晶胞及该第四记忆晶胞。

15.如权利要求14所述的小面积侧边电容只读存储器阵列的操作方法,其特征在于,相邻的两个该子存储器阵列中,两个该第三记忆晶胞彼此相邻且连接同一位元线,以共用同一接点,两个该第四记忆晶胞彼此相邻且连接同一该位元线,以共用同一接点。

16.一种小面积侧边电容只读存储器阵列的操作方法,该小面积侧边电容只读存储器阵列包含:复数条平行的位元线,区分为复数组位元线,该复数组位元线包含一第一组位元线与一第二组位元线;复数条平行的字线,与该复数条位元线互相垂直,并包含一第一字线;复数条平行的共源线,与该复数条字线互相平行,并包含一第一共源线;及复数子存储器阵列,每一该子存储器阵列连接两组该位元线、一该字线与一该共源线,每一该子存储器阵列包含:一第一记忆晶胞,连接该第一组位元线、该第一共源线与该第一字线;一第二记忆晶胞,连接该第二组位元线、该第一共源线与该第一字线,该第一记忆晶胞与该第二记忆晶胞互相对称配置,并位于该第一共源线的同一侧;一第三记忆晶胞,连接该第一组位元线、该第一共源线与该第一字线,并以该第一共源线为轴与该第一记忆晶胞对称配置;及一第四记忆晶胞,连接该第二组位元线、该第一共源线与该第一字线,并以该第一共源线为轴与该第二记忆晶胞对称配置,又该第三记忆晶胞与该第四记忆晶胞互相对称配置,且与该第一记忆晶胞、该第二记忆晶胞位于该第一共源线的相异两侧,其中,该第一记忆晶胞、该第二记忆晶胞、该第三记忆晶胞及该第四记忆晶胞皆包含位于一半导体基底中的一p型场效晶体管与一电容;

17.如权利要求16所述的小面积侧边电容只读存储器阵列的操作方法,其特征在于,每一该子存储器阵列位于相邻的两组该位元线之间。

18.如权利要求16所述的小面积侧边电容只读存储器阵列的操作方法,其特征在于,该第一记忆晶胞、该第二记忆晶胞、该第三记忆晶胞及该第四记忆晶胞皆连接该第一字线,以共用同一接点。

19.如权利要求16所述的小面积侧边电容只读存储器阵列的操作方法,其特征在于,该第一组位元线包含两条该位元线,其分别连接该第一记忆晶胞及该第三记忆晶胞,且该第二组位元线亦包含两条该位元线,其分别连接该第二记忆晶胞及该第四记忆晶胞。

20.如权利要求19所述的小面积侧边电容只读存储器阵列的操作方法,其特征在于,相邻的两个该子存储器阵列中,两个该第三记忆晶胞彼此相邻且连接同一该位元线,以共用同一接点,两个该第四记忆晶胞彼此相邻且连接同一该位元线,以共用同一接点。

技术总结

本发明公开一种小面积侧边电容只读存储器元件及其阵列与操作方法,此小面积侧边电容只读存储器元件是在半导体基底内嵌有场效晶体管,场效晶体管包括第一介电层与叠设于第一介电层上方的第一导电闸极,第一导电闸极的侧边延伸至第二介电层上方与第二导电闸极连接而产生电容效应,此第二导电闸极具有以条状部连接的多个指状部。以此,本发明可以最小的布局面积产生最高的电容值,从而可缩小只读存储器整体面积,并达到高效率的读写。

技术研发人员:黄郁婷,吴其沛

受保护的技术使用者:亿而得微电子股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!