半导体结构和其制造方法与流程

本公开内容是关于半导体结构和其制造方法,且特别是关于动态随机存取存储器的半导体结构。

背景技术:

1、随着半导体技术的进展,半导体存储器装置的尺寸逐渐缩小,造成半导体存储器装置的集成密度增加。换而言之,在相同的晶片上可以整合更多的功能性装置。在这样的情况下,半导体存储器装置的临界尺寸也随之减少,使得电子产品可以更紧密整合。然而,当装置的临界尺寸缩小时,半导体工艺技术会面临许多困境。例如,由于半导体装置的元件缩小,装置的不同层元件之间的对准也变得更困难。

技术实现思路

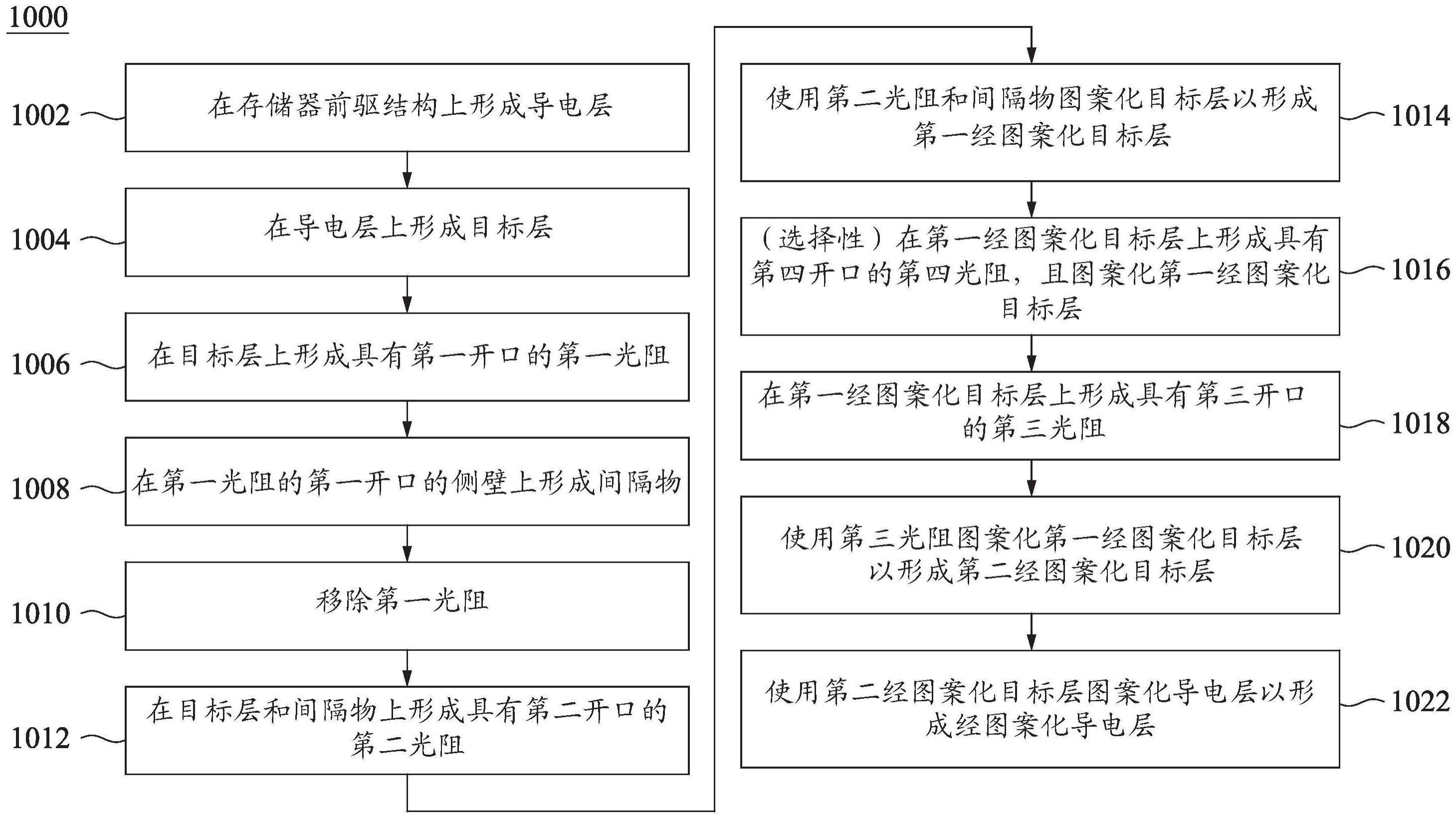

1、根据本公开的一实施方式,一种制造半导体结构的方法包括以下步骤。在存储器前驱结构上形成导电层,其中存储器前驱结构包括多个电晶体和设置在电晶体上且连接至电晶体的多个接触插塞。在导电层上形成目标层。在目标层上形成具有第一开口的第一光阻,其中第一开口包括接触插塞之中的第一接触插塞上方的沟槽。在第一光阻的第一开口的侧壁上形成间隔物。移除第一光阻,以及保留间隔物在目标层上。在目标层和间隔物上形成具有第二开口的第二光阻,其中第二开口暴露阵列电路区域中的一部分的间隔物和一部分的目标层。使用第二光阻和间隔物图案化目标层以形成第一经图案化目标层。在第一经图案化目标层上形成具有第三开口的第三光阻,其中第三开口暴露周边电路区域中的第一经图案化目标层。使用第三光阻图案化第一经图案化目标层以形成第二经图案化目标层。使用第二经图案化目标层图案化导电层以形成存储器前驱结构上的经图案化导电层,其中经图案化导电层包括第一接触插塞上方的环形结构,且环形结构对齐第一接触插塞下方的第一源极/漏极区域。

2、在一些实施方式中,在第一开口的侧壁上形成间隔物包括在第一开口的沟槽中形成间隔物,且形成在沟槽的相对侧上的间隔物免于彼此接触。

3、在一些实施方式中,在第一开口的侧壁上形成间隔物包括形成宽度在26nm至30nm之间的间隔物。

4、在一些实施方式中,第二开口所暴露的部分的间隔物包括形成在第一开口的沟槽中的间隔物。

5、在一些实施方式中,在目标层和间隔物上形成第二光阻包括形成覆盖另一部分的间隔物的第二光阻,第二光阻的侧壁和第二光阻所覆盖的另一部分的间隔物的侧壁之间的距离在50nm至100nm之间。

6、在一些实施方式中,在目标层和间隔物上形成第二光阻包括形成覆盖周边电路区域中的目标层的第二光阻。

7、在一些实施方式中,第一经图案化目标层包括第一接触插塞上方的环形部分,且环形部分对齐第一接触插塞下方的第一源极/漏极区域。

8、在一些实施方式中,方法进一步包括在形成第三光阻之前,在第一经图案化目标层上形成具有第四开口的第四光阻,其中第四开口暴露阵列电路区域中的一部分的第一经图案化目标层,且第四光阻覆盖第一经图案化目标层的环形部分。使用第四光阻图案化第一经图案化目标层,但免于图案化环形部分。

9、在一些实施方式中,在第一经图案化目标层上形成第三光阻包括形成覆盖第一经图案化目标层的环形部分的第三光阻。

10、在一些实施方式中,在第一经图案化目标层上形成第三光阻包括形成覆盖阵列电路区域中的第一经图案化目标层的第三光阻。

11、在一些实施方式中,目标层包括氮化物,且间隔物包括氧化物。

12、根据本公开的一实施方式,提供一种半导体结构。半导体结构包括多个电晶体、层间介电层、多个接触插塞和经图案化导电层。电晶体设置在基板中,其中各个电晶体包括栅极结构和设置在栅极结构的相对侧上的源极/漏极区域。层间介电层设置在基板上方。接触插塞设置在层间介电层中,其中各个接触插塞电性连接至源极/漏极区域之中的一者。经图案化导电层设置在层间介电层上且通过接触插塞电性连接至电晶体,其中经图案化导电层包括接触插塞之中的第一接触插塞上方的环形结构,且环形结构对齐第一接触插塞下方的第一源极/漏极区域。

13、在一些实施方式中,环形结构暴露第一接触插塞。

14、在一些实施方式中,环形结构落在基板上的投影环绕第一源极/漏极区域。

15、在一些实施方式中,环形结构与第一接触插塞部分重叠。

16、在一些实施方式中,环形结构的宽度在26nm至30nm之间。

17、在一些实施方式中,半导体结构进一步包括设置在基板上方的多个位元线,以及设置在基板和位元线之间的多个位元线接触插塞,其中位元线通过位元线接触插塞而电性连接至设置在两个接触插塞之间的源极/漏极区域。

18、在一些实施方式中,经图案化导电层与位元线接触插塞重叠。

19、在一些实施方式中,经图案化导电层通过接触插塞电性连接至源极/漏极区域。

20、在一些实施方式中,经图案化导电层连接至电源供应器。

技术特征:

1.一种制造半导体结构的方法,其特征在于,包括:

2.根据权利要求1所述的方法,其中在所述第一开口的所述侧壁上形成所述间隔物包括在所述第一开口的所述沟槽中形成所述间隔物,且形成在所述沟槽的相对侧上的所述间隔物免于接触彼此。

3.根据权利要求1所述的方法,其中在所述第一开口的所述侧壁上形成所述间隔物包括形成宽度在26nm至30nm之间的所述间隔物。

4.根据权利要求1所述的方法,其中所述第二开口所暴露的所述部分的所述间隔物包括形成在所述第一开口的所述沟槽中的所述间隔物。

5.根据权利要求1所述的方法,其中在所述目标层和所述间隔物上形成所述第二光阻包括形成覆盖另一部分的所述间隔物的所述第二光阻,所述第二光阻的侧壁和所述第二光阻所覆盖的所述另一部分的所述间隔物的侧壁之间的距离在50nm至100nm之间。

6.根据权利要求1所述的方法,其中在所述目标层和所述间隔物上形成所述第二光阻包括形成覆盖所述周边电路区域中的所述目标层的所述第二光阻。

7.根据权利要求1所述的方法,其中所述第一经图案化目标层包括所述第一接触插塞上方的环形部分,且所述环形部分对齐所述第一接触插塞下方的所述第一源极/漏极区域。

8.根据权利要求7所述的方法,其中,进一步包括:

9.根据权利要求7所述的方法,其中在所述第一经图案化目标层上形成所述第三光阻包括形成覆盖所述第一经图案化目标层的所述环形部分的所述第三光阻。

10.根据权利要求1所述的方法,其中在所述第一经图案化目标层上形成所述第三光阻包括形成覆盖所述阵列电路区域中的所述第一经图案化目标层的所述第三光阻。

11.根据权利要求1所述的方法,其中所述目标层包括氮化物,且所述间隔物包括氧化物。

12.一种半导体结构,其特征在于,包括:

13.根据权利要求12所述的半导体结构,其中所述环形结构暴露所述第一接触插塞。

14.根据权利要求12所述得半导体结构,其中所述环形结构落在所述基板上的投影环绕所述第一源极/漏极区域。

15.根据权利要求12所述的半导体结构,其中所述环形结构与所述第一接触插塞部分重叠。

16.根据权利要求12所述的半导体结构,其中所述环形结构的宽度在26nm至30nm之间。

17.根据权利要求12所述的半导体结构,其中,进一步包括:

18.根据权利要求17所述的半导体结构,其中所述经图案化导电层与所述多个位元线接触插塞重叠。

19.根据权利要求12所述的半导体结构,其中所述经图案化导电层通过所述多个接触插塞电性连接至所述多个源极/漏极区域。

20.根据权利要求12所述的半导体结构,其中所述经图案化导电层连接至电源供应器。

技术总结

本公开提供一种制造半导体结构的方法。在存储器前驱结构上形成导电层。在导电层上形成目标层。在目标层上形成具有第一开口的第一光阻。在第一开口的侧壁上形成间隔物。在目标层和间隔物上形成第二光阻。使用第二光阻和间隔物图案化目标层以形成第一经图案化目标层。在第一经图案化目标层上形成第三光阻。使用第三光阻图案化第一经图案化目标层以形成第二经图案化目标层。使用第二经图案化目标层图案化导电层以形成经图案化导电层,经图案化导电层包括对齐源极/漏极区域的环形结构。环形结构对齐存储器前驱结构的源极/漏极区域,使经图案化导电层的其他部分对齐存储器前驱结构的其他元件,因此改善元件之间的对准、减少结构中漏电流。

技术研发人员:施江林,吕学翰,林育廷

受保护的技术使用者:南亚科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!