一种半导体器件及其制造方法

本发明涉及半导体器件,尤其涉及一种半导体器件及其制造方法。

背景技术:

1、电容器是一种存储电量和电能的元件。可以通过在电容器上施加不同的电压,使得电容器内存储不同数量的电荷。在此基础上,可以通过电容器来实现对不同数据的存储。由此可见,电容器的品质直接影响半导体器件的数据存储性能。

2、但是,现有的半导体器件所包括的金属互连层限制了电容器电容量的增加,导致电容器的数据存储性能较差。

技术实现思路

1、本发明的目的在于提供一种半导体器件及其制造方法,用于在确保半导体器件具有较高良率的情况下,增大电容器的电容量,提升电容器的数据存储性能。

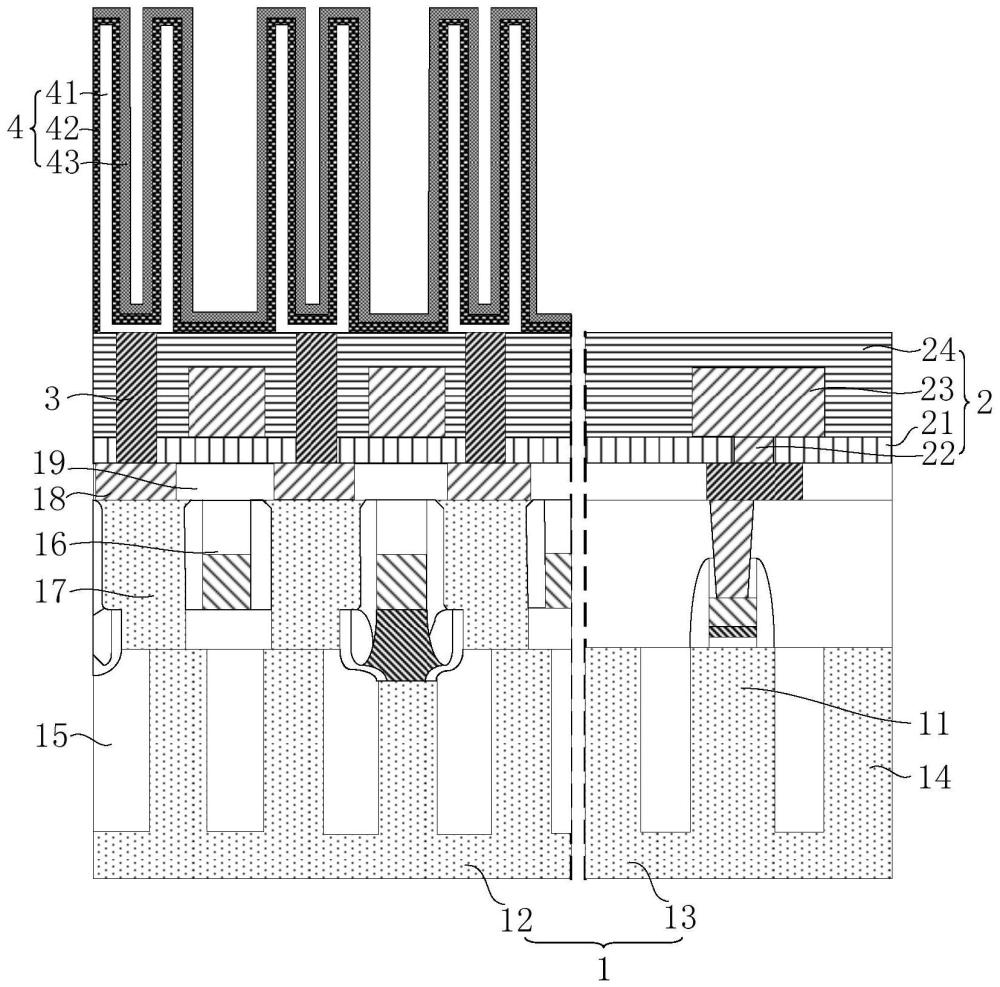

2、为了实现上述目的,本发明提供了一种半导体器件,该半导体器件包括:

3、具有有源区的基底;

4、形成在基底上的金属互连层;

5、贯穿金属互连层的连接结构;

6、形成在金属互连层上的电容器;电容器所包括的下电极通过连接结构与有源区电连接。

7、与现有技术相比,本发明提供的半导体器件中,金属互连层形成在基底上。并且,电容器形成在金属互连层上,电容器所包括的下电极可以通过贯穿金属互连层的连接结构与基底具有的有源区电连接。基于此,形成在基底表面、且待引出的相应结构可以通过金属互连层与外部器件电连接。在实际应用中,在外部器件的控制下,与有源区电连接的电容器内可以存储不同数量的电荷,实现对不同数据的存储。同时,因金属互连层设置在电容器的下方,故即使通过增大电容器所包括的下电极高度的方式,或者通过更改电容器结构设计的方式来增加电容器具有的电容量,也不会影响金属互连层与基底之间的垂直距离,从而能够解决现有技术中因金属互连层形成在电容器上、以及增大下电极的高度或更改电容器的结构设计而导致金属互连层的制造难度较大的技术问题,防止因金属互连层而限制了电容器电容量的增加,提升电容器的数据存储性能。

8、此外,在制造本发明提供的半导体器件的过程中,因金属互连层形成在电容器的下方,即在制造金属互连层时,还未形成电容器。基于此,即使形成金属互连层所需要的工艺温度较高,也不会因金属互连层和电容器所包括的上电极内的金属离子向下扩散至下电极内而使得下电极变形,从而可以降低电容器的漏电损耗,改善电容器的运行速度,进一步提升电容器的数据存储性能。

9、本发明还提供了一种半导体器件的制造方法,该半导体器件的制造方法包括:

10、提供一具有有源区的基底;

11、在基底上形成金属互连层;

12、形成贯穿金属互连层的连接结构;

13、在金属互连层上形成电容器;电容器所包括的下电极通过连接结构与有源区电连接。

14、与现有技术相比,本发明提供的半导体器件的制造方法的有益效果与上述技术方案所提供的半导体器件的有益效果,此处不再赘述。

技术特征:

1.一种半导体器件,其特征在于,包括:

2.根据权利要求1所述的半导体器件,其特征在于,所述基底包括存储单元区域和外围电路区域;所述金属互连层覆盖所述存储单元区域和所述外围电路区域;所述连接结构形成在所述金属互连层位于存储单元区域上的部分内;所述电容器形成在所述存储单元区域的上方。

3.根据权利要求1所述的半导体器件,其特征在于,所述金属互连层包括第一绝缘层、接触结构、金属互连线和第二绝缘层;

4.根据权利要求1所述的半导体器件,其特征在于,所述下电极的径向截面积大于所述连接结构的径向截面积;和/或,

5.根据权利要求1所述的半导体器件,其特征在于,所述基底还具有位于有源区上的位线结构、以及位于相邻位线结构之间的存储接触部和隔离部;所述隔离部用于隔离相邻两个所述存储接触部;所述下电极通过所述连接结构和所述存储接触部与所述有源区电连接。

6.根据权利要求1~4任一项所述的半导体器件,其特征在于,所述电容器还包括覆盖在下电极表面的介质层、以及形成在所述介质层上的上电极。

7.一种半导体器件的制造方法,其特征在于,包括:

8.根据权利要求7所述的半导体器件的制造方法,其特征在于,所述在所述基底上形成金属互连层,包括:

9.根据权利要求8所述的半导体器件的制造方法,其特征在于,所述形成贯穿所述金属互连层的连接结构,包括:

10.根据权利要求7所述的半导体器件的制造方法,其特征在于,所述基底包括存储单元区域和外围电路区域;所述金属互连层覆盖所述存储单元区域和所述外围电路区域;

技术总结

本发明公开了一种半导体器件及其制造方法,涉及半导体器件技术领域,用于在确保半导体器件具有较高良率的情况下,增大电容器的电容量,提升电容器的数据存储性能。所述半导体器件包括:基底、金属互连层、连接结构和电容器。基底具有有源区。金属互连层形成在基底上。连接结构贯穿金属互连层。电容器形成在金属互连层上。电容器所包括的下电极通过连接结构与有源区电连接。所述半导体器件的制造方法用于制造所述半导体器件。

技术研发人员:安重镒,李相遇,李俊杰,周娜,李琳,王佳

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!