一种热插拔IO口保护电路的制作方法

本发明涉及热插拔i/o,尤其涉及一种热插拔i/o口保护电路。

背景技术:

1、热插拔(hot-swap)即“带电插拔”,是指能够在不关闭系统,不切断电源的情况下插入或拔除支持热插拔的周边设备,不会导致主机或周边设备烧毁。传统电路采用5v输入忍耐的方法实现热插拔如图1所示,当外界信号或电压高于内部io电压时,与外界输入信号相接的pmos的衬底电压等于外部输入电压或信号;当外部电压或信号小于内部io电压时,与外界输入信号相接的pmos的衬底电压等于内部电压vdd,这样能确保外界输入信号在插拔的瞬间,和内部芯片之间没有电流通道。

2、图2是当前市面上的io口保护电路中pmos管寄生二极管的等效电路原理图,需要说明,图2及上述记载为便于理解,仅记载了io驱动电路包含pmos晶体管pm7和nmos晶体管nm6,但实际的io驱动电路中可以包括一组并联的pmos管和一组并联的nmos管。

3、当电压power上电时,无论pad端口电压pad为高电平或低电平,该io发送端驱动电路中的电流方向始终为pm7的源极至漏极,nm6的漏极至源极。然而,当电压vdd没有正常上电,而pad端口插入的外接设备已经有信号或电压,即pm7的源极为低电平,pm7的漏极为高电平时,pad端口的信号或电压通过寄生二极管会导通到电源上,即pmos管可看作寄生二极管正向导通,产生不期望的漏电通路,导致主机或周边设备烧毁。

技术实现思路

1、本发明的目的在于,针对于上述缺陷,提供一种热插拔保护电路,在芯片需要热插、热拔的时候,防止主机或周边设备烧毁。

2、为解决上述问题,本发明实施例公开了如下技术方案:

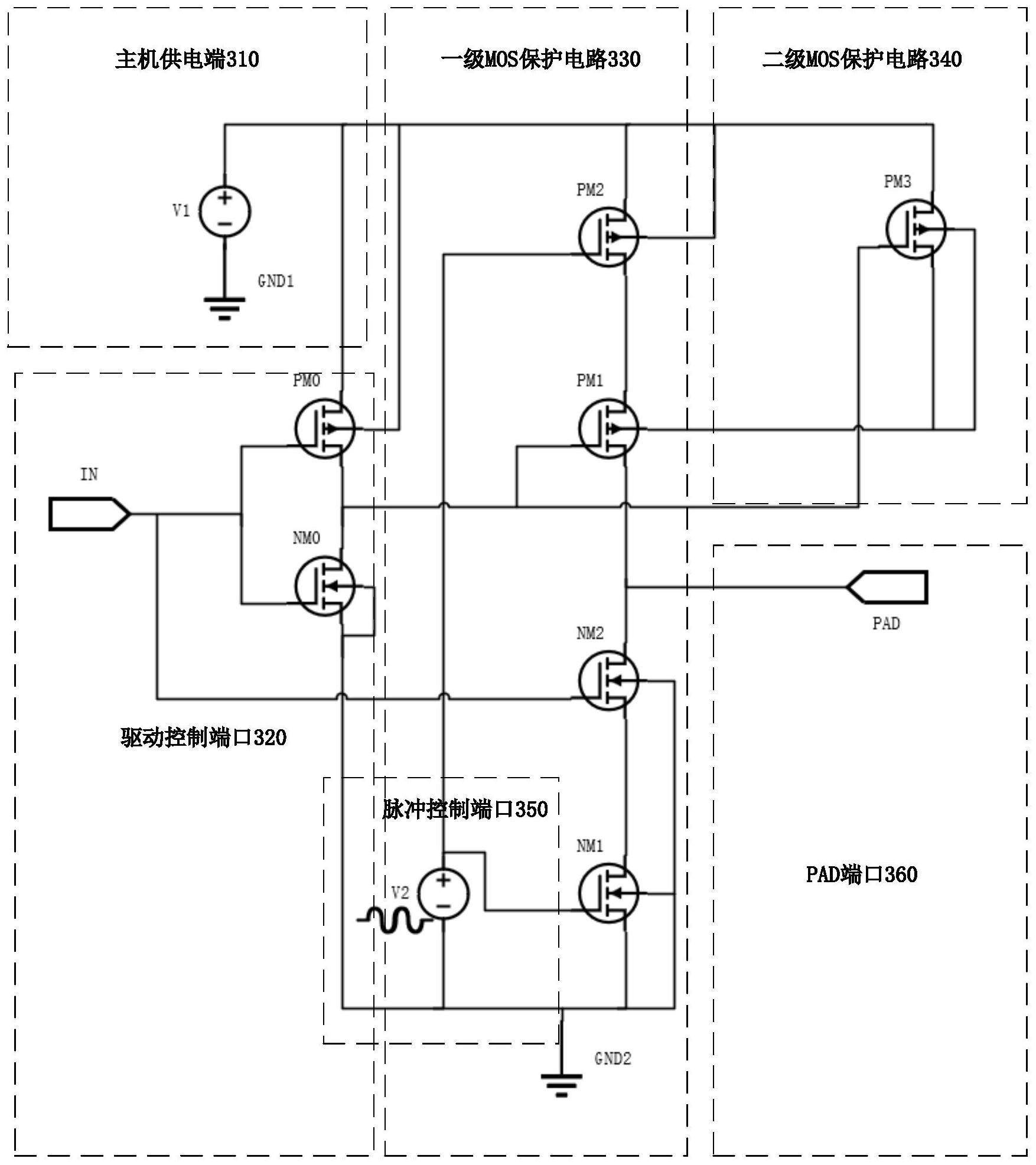

3、一种热插拔io口保护电路,拥有正常工作和热插拔两种工作状态,电路包括:

4、由主机连接的主机供电端经第三pmos管(pm2)、第二pmos管(pm1)到连接周边设备的pad端口形成的第一放电通路;

5、由周边设备连接的pad端口经第三nmos管(nm2)、第二nmos(nm1)到地形成的第二放电通路;

6、由驱动控制端口到第二pmos管(pm1)以及驱动控制端口到第四pmos(pm3)管形成的第一控制通路,第一控制通路输出第一控制信号和第五控制信号;

7、由驱动控制端口到第三nmos管(nm2)形成的第二控制通路,第二控制通路输出第二控制信号;

8、由脉冲控制端口到第二nmos(nm1)以及脉冲控制端口到第三pmos管(pm2)形成的第三控制通路,第三控制通路输出第三控制信号和第四控制信号;

9、正常工作状态,若发生正向放电,第一控制通路输出第一控制信号,第二控制通路输出第二控制信号,第三控制通路输出第三控制信号,第一放电通路导通、第二放电通路截止;若发生负向放电,第三控制通路输出第四控制信号,第二放电通路导通、第一放电通路截止;

10、热插拔状态,第一控制通路输出第五控制信号,pm3通过关断驱动控制端口与pad端口、主机供电端与pad端口之间的电流通道实现对主机和周边设备的保护。

11、优选地,所述驱动控制端口包括一个由pm0和nm0组成的反相器接入电路,pm0和nm0的栅极接入热插拔使能脚,漏极输出端接入pm1和pm3的漏极,其中pm0的衬底和源极接入第一放电通路,nm0的源极与衬底相连接地。

12、优选地,pm1栅极与输入电路反相器的输出端相连,衬底接入pm3的衬底,源极与pm1的源极连接,漏极与pad相连形成第一放电通路;nm2栅极与输入电路反相器的输出端相连,漏极与pm1和pad相连,衬底和源极分别和nm2的衬底和源极相连接形成第二放电通路。

13、优选地,脉冲控制电源的输出端与nm1、pm2的栅极相连接。

14、优选地,pm3的栅极与反相器输出相连,漏极和衬底与pm1衬底相连,pm3的源极与所述pm0、pm2的衬底和源极相连接入直流电源供电的第一放电通道,当发生负向放电时pm3可以关闭pm0、pm1以及pm2衬底间的寄生二极管的截止pad端到直流电源和驱动控制电路间的电流通道。

15、进一步地,主机供电端口包括一个直流电源,该电源为整个电路和pad端口供电;pad端口为连接周边设备信号与电压的接口;正常工作状态下主机供电端口和驱动控制端口为输入端,热插拔状态下pad端口为输入端。

16、进一步地,正常工作状态下驱动控制端口输出第一控制信号为高电平,第一控制信号经反相器反向后置为低电平输出第二控制信号,nm2接收第一控制信号,打开nm2;pm1接收第二控制信号打开pm1,形成第一放电通道和第二放电通道。

17、进一步地,在工作状态下,脉冲控制电源输出第三控制信号,输出为低电平,打开pm2,关闭nm1,第一放电通道导通,第二放电通道截止。

18、进一步地,在工作状态下,脉冲控制电源输出第四控制信号,输出为高电平,关闭pm2打开nm1,第一放电通道截止,第二放电通道导通。

19、进一步地,在热插拔状态下,热插拔使能脚为高电平,输出第五控制信号,pm1、pm3接收第五控制信号关闭mos管,pm3截止pm0、pm1以及pm2衬底寄生二极管的电流通道,pad端到驱动控制电路和直流电源间没有漏电流。

20、本发明通过热插拔时关断in端和pm1之间电路、以及pad和pm1衬底之间的电流通道,实现了主机在热插拔时不会产生漏电流导致主机或周边设备烧毁。

技术特征:

1.一种热插拔io口保护电路,拥有正常工作和热插拔两种工作状态,电路包括:

2.根据权利要求1所述的保护电路,其特征在于:所述驱动控制端口包括一个由pm0和nm0组成的反相器接入电路,pm0和nm0的栅极接入热插拔使能脚,漏极输出端接入pm1和pm3的漏极,其中pm0的衬底和源极接入第一放电通路,nm0的源极与衬底相连接地。

3.根据权利要求2所述的保护电路,其特征在于:pm1栅极与输入电路反相器的输出端相连,衬底接入pm3的衬底,源极与pm1的源极连接,漏极与pad相连形成第一放电通路;nm2栅极与输入电路反相器的输出端相连,漏极与pm1和pad相连,衬底和源极分别和nm2的衬底和源极相连接形成第二放电通路。

4.根据权利要求1所述的保护电路,其特征在于:脉冲控制电源的输出端与nm1、pm2的栅极相连接。

5.根据权利要求1所述的保护电路,其特征在于:pm3的栅极与反相器输出相连,漏极和衬底与pm1衬底相连,pm3的源极与所述pm0、pm2的衬底和源极相连接入直流电源供电的第一放电通道,当发生负向放电时pm3可以关闭pm0、pm1以及pm2衬底间的寄生二极管的截止pad端到直流电源和驱动控制电路间的电流通道。

6.根据权利要求1所述的保护电路,其特征在于:主机供电端口包括一个直流电源,该电源为整个电路和pad端口供电;pad端口为连接周边设备信号与电压的接口;正常工作状态下主机供电端口和驱动控制端口为输入端,热插拔状态下pad端口为输入端。

7.根据权利要求1所述的保护电路,其特征在于:正常工作状态下驱动控制端口输出第一控制信号为高电平,第一控制信号经反相器反向后置为低电平输出第二控制信号,nm2接收第一控制信号,打开nm2;pm1接收第二控制信号打开pm1,形成第一放电通道和第二放电通道。

8.根据权利要求6或7所述电路,其特征在于:在工作状态下,脉冲控制电源输出第三控制信号,输出为低电平,打开pm2,关闭nm1,第一放电通道导通,第二放电通道截止。

9.根据权利要求6或7所述电路,其特征在于:在工作状态下,脉冲控制电源输出第四控制信号,输出为高电平,关闭pm2打开nm1,第一放电通道截止,第二放电通道导通。

10.根据权利要求1所述的保护电路,其特征在于:热插拔状态下,热插拔使能脚为高电平,输出第五控制信号,pm1、pm3接收第五控制信号关闭mos管,pm3截止pm0、pm1以及pm2衬底寄生二极管的电流通道,pad端到驱动控制电路和直流电源间没有漏电流。

技术总结

本发明实施例公开了一种热插拔IO口保护电路,所述电路拥有正常工作和热插拔两种工作状态,电路包括:主机供电端、驱动控制端口、一级MOS保护电路、二级MOS保护电路、脉冲控制端口和PAD端口,在工作状态下驱动控制电路通过打开一级MOS保护电路形成第一放电通道和第二放电通道,再由脉冲控制电源控制第一放电通路、第二放电通路的导通和截止,并在热插拔时通过二级MOS保护电路关断主机供电端、驱动控制端口与一级MOS保护电路之间,以及PAD端和一级MOS保护电路之间的电流通道实现了主机在热插拔时不会产生漏电流导致主机或周边设备烧毁。

技术研发人员:刘成立,王泽

受保护的技术使用者:京微齐力(上海)信息科技有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!