全数字工作周期校正器及校正输出时钟的工作周期的方法与流程

本发明是关于工作周期校正,尤指一种全数字工作周期校正器以及用来校正一输出时钟的一工作周期的方法。

背景技术:

1、当使用一模拟工作周期校正器对一输出时钟的工作周期进行校正时,该模拟工作周期校正器典型地利用其内的电阻-电容低通滤波器对该输出时钟进行低通滤波处理。由于该电阻-电容低通滤波器的3-分贝带宽典型地是远低于该输出时钟的频率,等效上可达到将该输出时钟的电压取平均的效果,以产生一平均后电压。另外,该模拟工作周期校正器可利用一运算放大器接收该平均后电压以及一参考电压,并且据以产生一控制电压以控制该输出时钟的工作周期,以形成一回路操作。在上述回路操作达到一锁定状态时,该平均后电压可收敛为具有与该参考电压相同的电压位准,而该输出时钟的工作周期可被校正至一目标比例。

2、然而,在半导体工艺越来越先进而供应电压的位准也逐渐下降的情况下,上述架构会遭遇到几个瓶颈而无法达成校正工作周期的目的。例如,该运算放大器的电压余量(headroom)会被压迫,使得该运算放大器内的晶体管在工艺-电压-温度(process-voltage-temperature,pvt)变异下较容易进入线性操作区而造成回路锁定失效。此外,上述模拟工作周期校正器包含了许多模拟信号控制电路,因此为了满足增益、组件匹配性、带宽等效能,这些模拟信号控制电路较难以随着半导体制程的发展得到缩小电路面积的好处。

3、因此,需要一种新颖的架构以及方法,解决上述利用模拟电路来实施所造成的问题。

技术实现思路

1、本发明的目的在于提供一种全数字工作周期校正器以及用来校正一输出时钟的一工作周期的方法,以通过全数字的电路及控制来实施工作周期的校正。

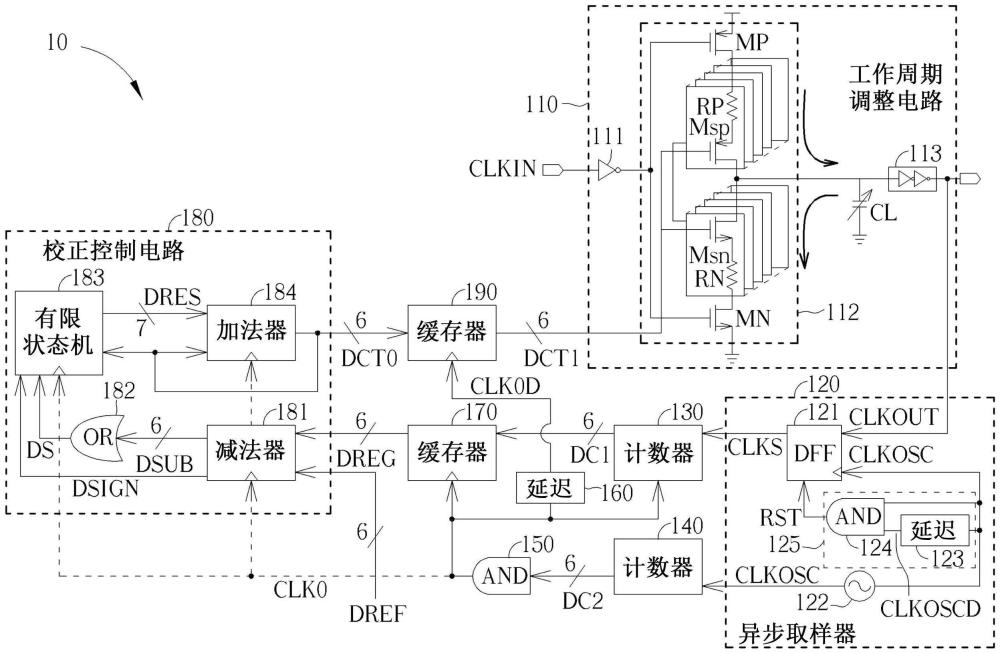

2、本发明至少一实施例提供一种全数字工作周期校正器。该全数字工作周期校正器包含一工作周期调整电路、一异步取样器、一计数器以及一校正控制电路。具体来说,该工作周期调整电路是用来依据一数字控制码对一输入时钟进行工作周期调整以产生一输出时钟。该异步取样器是用来对该输出时钟进行异步取样,以分别在n个时间点产生n个取样结果,其中n为正整数。该计数器是用来计数在该n个取样结果中的第一逻辑值的数量以产生一计数结果。该校正控制电路是用来比较该计数结果与一参考数值作以产生一比较结果,并且依据该比较结果选择性地调整该数字控制码以校正该输出时钟的一工作周期。

3、本发明至少一实施例提供一种用来校正一输出时钟的一工作周期的方法,其中该方法是可应用于(applicable to)一全数字工作周期校正器。该方法包含:利用该全数字工作周期校正器的一工作周期调整电路依据一数字控制码对一输入时钟进行工作周期调整以产生该输出时钟;利用该全数字工作周期校正器的一异步取样器对该输出时钟进行异步取样,以分别在n个时间点产生n个取样结果,其中n为正整数;利用该全数字工作周期校正器的一计数器计数在该n个取样结果中的第一逻辑值的数量以产生一计数结果;以及利用该全数字工作周期校正器的一校正控制电路比较该计数结果与一参考数值以产生一比较结果,并且依据该比较结果选择性地调整一数字控制码,以校正该输出时钟的该工作周期。

4、本发明的实施例提供的全数字工作周期校正器以及相关方法通过对该输出时钟进行异步取样,以利用数字的检测方式来判断该输出时钟的工作周期是偏高或偏低,并且据以进行对应的调整。由于本发明的实施例能以全数字的电路来实施,因此整体电路面积可随着半导体工艺的进展逐渐被缩小。此外,本发明的实施例不需要使用运算放大器等难以设计或优化的模拟电路,因此,相关技术的问题可被有效地解决。

技术特征:

1.一种全数字工作周期校正器,包含:

2.如权利要求1所述的全数字工作周期校正器,其中该工作周期调整电路包含:

3.如权利要求2所述的全数字工作周期校正器,其中该输入级电路还包含:

4.如权利要求1所述的全数字工作周期校正器,其中该异步取样器包含:

5.如权利要求1所述的全数字工作周期校正器,其中该校正控制电路包含:

6.如权利要求1所述的全数字工作周期校正器,其中当该比较结果指出该计数结果大于该参考数值且该数字控制码尚未达到一最大可允许值时,该校正控制电路增加该数字控制码以使该工作周期调整电路减少该输出时钟的该工作周期。

7.如权利要求1所述的全数字工作周期校正器,其中当该比较结果指出该计数结果大于该参考数值且该数字控制码已达到一最大可允许值时,该校正控制电路维持该数字控制码以使该工作周期调整电路维持该输出时钟的该工作周期。

8.如权利要求1所述的全数字工作周期校正器,其中当该比较结果指出该计数结果小于该参考数值且该数字控制码尚未达到一最小可允许值时,该校正控制电路减少该数字控制码以使该工作周期调整电路增加该输出时钟的该工作周期。

9.如权利要求1所述的全数字工作周期校正器,其中当该比较结果指出该计数结果小于该参考数值且该数字控制码已达到一最小可允许值时,该校正控制电路维持该数字控制码以使该工作周期调整电路维持该输出时钟的该工作周期。

10.一种用来校正一输出时钟的一工作周期的方法,可应用于一全数字工作周期校正器,该方法包含:

技术总结

本发明提供一种全数字工作周期校正器及校正输出时钟的工作周期的方法。该全数字工作周期校正器包含工作周期调整电路、异步取样器、计数器以及校正控制电路。该工作周期调整电路依据数字控制码对输入时钟进行工作周期调整以产生该输出时钟。该异步取样器对该输出时钟进行异步取样,以分别在N个时间点产生N个取样结果。该计数器计数在该N个取样结果中的第一逻辑值的数量以产生计数结果。该校正控制电路将该计数结果与参考数值作比较以产生比较结果,并且依据该比较结果选择性地调整该数字控制码以校正该输出时钟的工作周期。

技术研发人员:陈则宏

受保护的技术使用者:瑞昱半导体股份有限公司

技术研发日:

技术公布日:2024/4/29

- 还没有人留言评论。精彩留言会获得点赞!