一种FPGA通用IO动态配置上下拉电阻的方法与流程

一种fpga通用io动态配置上下拉电阻的方法

技术领域

1.本发明涉及电子信息技术领域,尤其涉及一种fpga通用io动态配置上下拉电阻的方法。

背景技术:

2.在fpga的开发环境下,可以静态配置通用io的上拉,下拉或高阻态属性,而若需要通用io动态配置内置上下拉电阻,还需要嵌入式微控制的通用io,才能支持内置上下拉电阻可配。

3.其中,fpga通用io静态配置上下拉电阻,无法满足部分开发方案的需求。静态配置文件是在fpga开发阶段,以配置文件的形式固化在fpga的初始化程序内的,无法动态修改。而部分开发方案需要灵活配置通用io处于输入悬空时的默认电平状态。

技术实现要素:

4.本发明的目的是为了解决现有技术中存在的缺点,而提出的一种fpga通用io动态配置上下拉电阻的方法。

5.为了实现上述目的,本发明采用了如下技术方案:

6.一种fpga通用io动态配置上下拉电阻的方法,包括以下步骤:

7.s1、添加上下拉驱动io,利用fpga的io资源富裕的特性,为每个需要动态配置上下拉的通用io,增加一个上下拉驱动io,包括io_pue与io_pde,其中io_pue为“上拉使能”控制位,io_pde为“下拉使能”控制位;

8.s2、添加串联电阻,根据开发方案的需求在通用io和上下拉驱动io间串联电阻;

9.s3、添加输出使能端,且上下拉驱动io的输出使能端,由“上拉使能”和“下拉使能”的异或结果驱动;

10.s4、添加输出驱动端,且上下拉驱动io的输出驱动端,由“上拉使能”控制位驱动;

11.优选地,所述步骤s3中,当“上拉使能”或“下拉使能”单独使能时,上下拉驱动io将处于输出状态。

12.优选地,所述步骤s4中,当“上拉使能”和“下拉使能”同时禁止或使能时,上下拉驱动io将处于高阻状态,通用io处于悬空状态。

13.优选地,“上拉使能”有效时输出高电平,通用io被上拉;“下拉使能”有效时输出低电平,通用io被下拉。

14.本发明具有以下有益效果:

15.利用fpga的io资源富裕的特性,为每个需要动态配置上下拉的通用io,增加一个上下拉驱动io,可实现fpga的通用io动态配置上下拉电阻。

附图说明

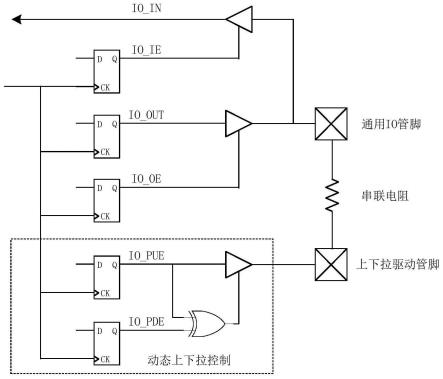

16.图1为本发明提出的一种fpga通用io动态配置上下拉电阻的方法的结构示意图。

具体实施方式

17.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

18.一种fpga通用io动态配置上下拉电阻的方法,包括以下步骤:

19.s1、添加上下拉驱动io,利用fpga的io资源富裕的特性,为每个需要动态配置上下拉的通用io,增加一个上下拉驱动io,包括io_pue与io_pde,其中io_pue为“上拉使能”控制位,io_pde为“下拉使能”控制位;

20.s2、添加串联电阻,根据开发方案的需求在通用io和上下拉驱动io间串联电阻;具体的,阻值由方案决定;

21.s3、添加输出使能端,且上下拉驱动io的输出使能端(oe),由“上拉使能”和“下拉使能”的异或结果驱动;当“上拉使能”或“下拉使能”单独使能时,上下拉驱动io将处于输出状态。上拉使能”有效时输出高电平,通用io被上拉;“下拉使能”有效时输出低电平,通用io被下拉;

22.s4、添加输出驱动端,且上下拉驱动io的输出驱动端(out),由“上拉使能”控制位驱动。

23.当“上拉使能”和“下拉使能”同时禁止或使能时,上下拉驱动io将处于高阻状态,通用io处于悬空状态。

24.本发明中,如图1所示,io_pue与io_pde异或产生上下拉驱动管脚的输出使能,两者任一使能,则上下拉驱动管脚处于输出状态,输出电平由io_pue的0/1状态决定;若两者都使能或禁止,则上下拉驱动管脚将处于高阻状态。

25.在fpga的通用io输出使能(io_oe)禁止,且输入使能(io_ie)使能时,管脚的输入处于悬空状态,会影响内部电路的逻辑状态。具体结果如下表所示:

26.io_ieio_oeio_outio_in通用io00-0高阻态10-x高阻态x100输出00110输出11111输出1

27.表1fpga通用io输入输出真值表

28.在fpga通用io输出使能(io_oe)禁止,且输入使能(io_ie)使能时,分别开启上拉使能(io_pue)和下拉使能(io_pde),上下拉驱动管脚将输出高电平或低电平,通过串联电阻对通用io进行上下拉驱动。若同时使能或同时禁止,则维持上下拉驱动管脚的高阻状态。具体结果如下表所述:

29.io_ieio_oeio_in通用ioio_pueio_pde上下拉驱动管脚10x高阻态00高阻态101上拉10输出1100下拉01输出010x高阻态11高阻态

30.表2fpga通用io输入输出真值表

31.综上,本发明利用fpga的io资源富裕的特性,为每个需要动态配置上下拉的通用io,增加一个上下拉驱动io,可实现fpga的通用io动态配置上下拉电阻。

32.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。

技术特征:

1.一种fpga通用io动态配置上下拉电阻的方法,其特征在于,包括以下步骤:s1、添加上下拉驱动io,利用fpga的io资源富裕的特性,为每个需要动态配置上下拉的通用io,增加一个上下拉驱动io,包括io_pue与io_pde,其中io_pue为“上拉使能”控制位,io_pde为“下拉使能”控制位;s2、添加串联电阻,根据开发方案的需求在通用io和上下拉驱动io间串联电阻;s3、添加输出使能端,且上下拉驱动io的输出使能端,由“上拉使能”和“下拉使能”的异或结果驱动;s4、添加输出驱动端,且上下拉驱动io的输出驱动端,由“上拉使能”控制位驱动。2.根据权利要求1所述的一种fpga通用io动态配置上下拉电阻的方法,其特征在于,所述步骤s3中,当“上拉使能”或“下拉使能”单独使能时,上下拉驱动io将处于输出状态。3.根据权利要求1所述的一种fpga通用io动态配置上下拉电阻的方法,其特征在于,所述步骤s4中,当“上拉使能”和“下拉使能”同时禁止或使能时,上下拉驱动io将处于高阻状态,通用io处于悬空状态。4.根据权利要求2所述的一种fpga通用io动态配置上下拉电阻的方法,其特征在于,“上拉使能”有效时输出高电平,通用io被上拉;“下拉使能”有效时输出低电平,通用io被下拉。

技术总结

本发明公开了一种FPGA通用IO动态配置上下拉电阻的方法,包括以下步骤:S1、添加上下拉驱动IO;S2、添加串联电阻,根据开发方案的需求在通用IO和上下拉驱动IO间串联电阻;S3、添加输出使能端;S4、添加输出驱动端。本发明利用FPGA的IO资源富裕的特性,为每个需要动态配置上下拉的通用IO,增加一个上下拉驱动IO,可实现FPGA的通用IO动态配置上下拉电阻。现FPGA的通用IO动态配置上下拉电阻。现FPGA的通用IO动态配置上下拉电阻。

技术研发人员:崔炳磊 史卫东 吴焜 林茂

受保护的技术使用者:广州中基国威电子科技有限公司

技术研发日:2022.11.02

技术公布日:2023/2/3

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1