半导体装置和多比特触发器电路的制作方法

本发明涉及半导体,尤其涉及一种半导体装置和多比特触发器电路。

背景技术:

1、由于现代高性能集成电路(integrated circuit,ic)设计中芯片密度的快速增长和时钟频率的提高,功耗已成为一个重要问题。在同步(synchronous)ic芯片设计中,总功耗的很大一部分是由时钟网络中的触发器操作(或工作)引起的。在传统的同步设计中,所有一比特(one-bit)(或单位元)触发器都被视为独立部件(independent component)。然而,近年来,随着工艺技术的进步,以及ic的特征尺寸不断缩小,最小尺寸的时钟驱动器可以触发多个触发器。因此,业内创建了多比特(multi-bit)触发器。多个一比特(或单位元)触发器被配置为由单个时钟驱动器提供的时钟信号触发。在多个一比特触发器之间共享时钟驱动器可以降低总时钟动态功耗,并减少多个触发器和时钟驱动器贡献的总面积。因此,与传统的一比特(或单比特)触发器相比,多触发器(多比特触发器)在功率、性能和面积(power,performance and area,ppa)方面的效率更高。

2、除了ppa问题外,连接数量和鲁棒性也是设计触发器电路时要考虑的问题。因此,希望有一种新颖的多比特触发器架构,它不仅具有高效的ppa,而且还减少了连接数量并提高了鲁棒性。

技术实现思路

1、有鉴于此,本发明提供一种半导体装置和多比特触发器电路,以解决上述问题。

2、根据本发明的第一方面,公开一种半导体装置,包括:

3、多个单元行,其中多个单元行至少包括第一单元行和第二单元行;

4、第一功能块,形成在该第一单元行中,用于提供第一预定功能;以及

5、第二功能块,形成在该第二单元行中并且被配置为提供与该第一预定功能相同的第二预定功能,

6、其中该第一单元行和该第二单元行具有至少一个不同的物理特性。

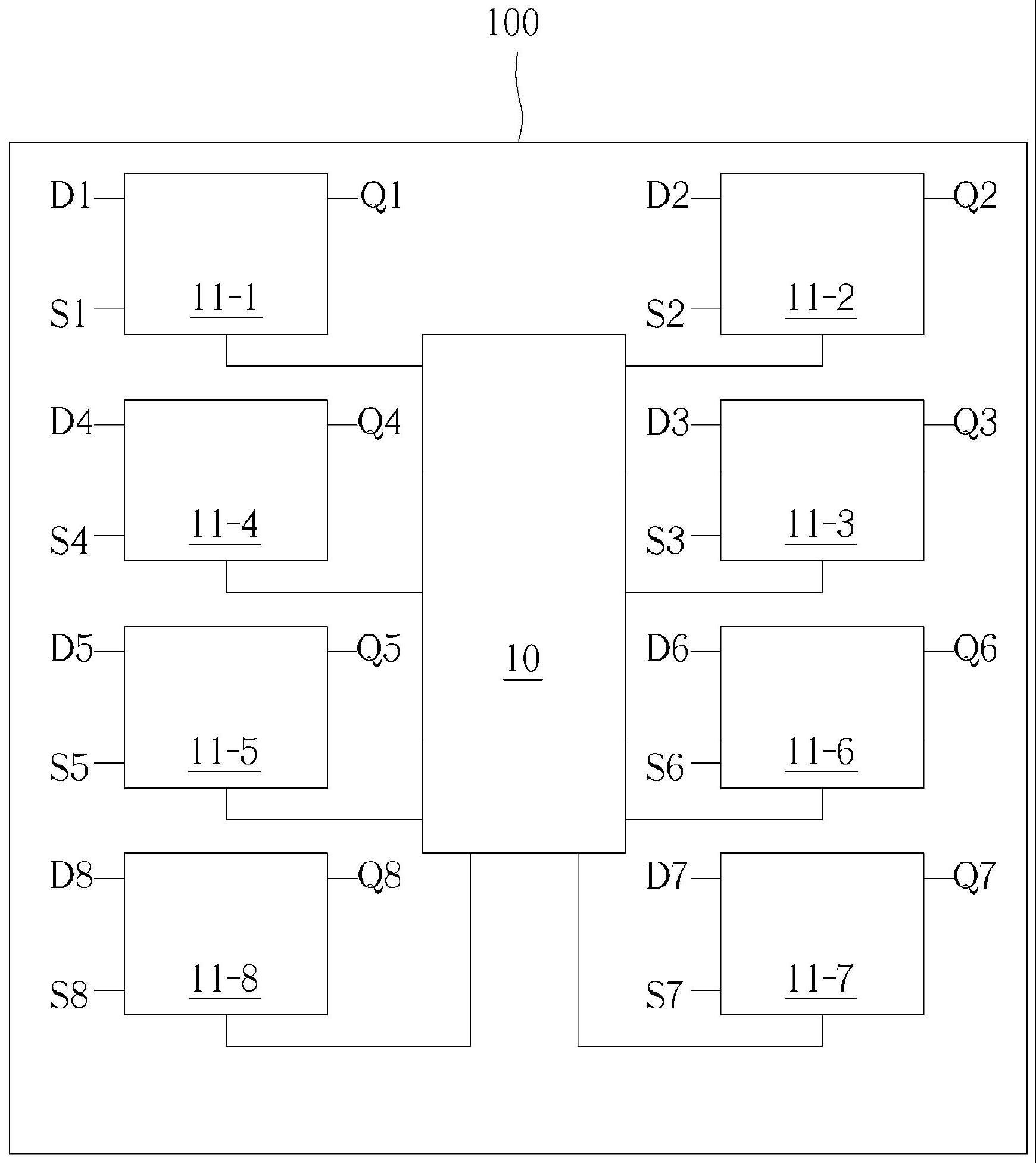

7、根据本发明的第二方面,公开一种多比特触发器电路,包括:

8、多个第一单元行;

9、多个第二单元行;以及

10、多个单位元触发器电路,包括:

11、第一单位元触发器电路,形成在该多个第一单元行中的一个中;以及

12、第二单位元触发器电路,形成在该多个第二单元行中的一个中,

13、其中,该多个第一单元行和该多个第二单元行具有至少一种不同的物理特性。

14、本发明的半导体装置由于包括:多个单元行,其中多个单元行至少包括第一单元行和第二单元行;第一功能块,形成在该第一单元行中,用于提供第一预定功能;以及第二功能块,形成在该第二单元行中并且被配置为提供与该第一预定功能相同的第二预定功能,其中该第一单元行和该第二单元行具有至少一个不同的物理特性。通过上述方案,将具有不同物理特性的单元行进行各种组合,使得半导体装置在功率、性能和面积方面的效率更高,并且连接数量更少和鲁棒性更好;并且本发明实施例的方案可以根据需求自由将不同物理特性的单元行进行组合和搭配,从而提供更多的设计选择,增加设计弹性。

技术特征:

1.一种半导体装置,其特征在于,包括:

2.如权利要求1所述的半导体装置,其特征在于,该第一功能块和该第二功能块均为单位元触发器电路。

3.如权利要求1所述的半导体装置,其特征在于,该第一单元行的高度与该第二单元行的高度不同。

4.如权利要求1所述的半导体装置,其特征在于,该第一单元行的驱动能力与该第二单元行的驱动能力不同,并且其中,该第一/第二单元行的驱动能力由以下中的至少一个确定:第一/第二单元行上对应的晶体管装置的装置宽度、鳍片数量和指状物数量。

5.如权利要求1所述的半导体装置,其特征在于,该多个单元行还包括多个第一单元行和多个第二单元行,该多个第一单元行和该多个第二单元行具有至少一个不同的物理特性,并且该多个第一单元行和该多个第二单元行以交错方式排列。

6.一种多比特触发器电路,其特征在于,包括:

7.如权利要求6所述的多比特触发器电路,其特征在于,该多个单位元触发器电路还包括:

8.如权利要求6所述的多比特触发器电路,其特征在于,该多个单位元触发器电路放置在预定布置中,以使由该多个单位触发器电路顺序生成的多个比特的比特序列具有正弦形状或蛇形形状。

9.如权利要求6所述的多比特触发器电路,其特征在于,该第一单位元触发器电路中的至少一个电路子单元和该第二单位元触发器电路中的至少一个电路子单元具有相同的功能,但具有不同的电路。

10.一种多比特触发器电路,其特征在于,包括:

11.如权利要求10所述的多比特触发器电路,其特征在于,该多个第一单元行至少包括第一个第一单元行和第二个第一单元行,该多个第二单元行至少包括第一个第二单元行以及第二个第二单元行,且该多个第一单元行和该多个第二单元行的布局从上到下的排列是第一个第一单元行、第一个第二单元行、第二个第一单元行和第二个第二单元行;或者,该多个第一单元行和该多个第二单元行的布局从上到下的排列是第一个第一单元行、第一个第二单元行、第二个第二单元行和第二个第一单元行;或者,该多个第一单元行和该多个第二单元行的布局从上到下的排列是第一个第一单元行、第二个第一单元行、第一个第二单元行和第二个第二单元行。

12.如权利要求11所述的多比特触发器电路,其特征在于,该多个单位元触发器电路包括:

13.如权利要求10所述的多比特触发器电路,其特征在于,该多个单位元触发器电路的第一部分和该多个单位元触发器电路的第二部分具有相同的功能但具有不同的电路。

14.如权利要求10所述的多比特触发器电路,其特征在于,该多个单位元触发器电路的第一部分的任一单位元触发器电路中的至少一个电路子单元和至少一个该多个单位元触发器电路的第二部分的任一单位元触发器电路中的电路子单元具有相同的功能但具有不同的电路。

15.一种多比特触发器电路,其特征在于,包括:

16.如权利要求15所述的多比特触发器电路,其特征在于,该第一单元行和该第二单元行具有至少一种不同的物理特性;或者,该第一单元行和该第二单元行具有相同的物理特性。

技术总结

本发明公开一种半导体装置,包括:多个单元行,其中多个单元行至少包括第一单元行和第二单元行;第一功能块,形成在该第一单元行中,用于提供第一预定功能;以及第二功能块,形成在该第二单元行中并且被配置为提供与该第一预定功能相同的第二预定功能,其中该第一单元行和该第二单元行具有至少一个不同的物理特性。通过上述方案,将具有不同物理特性的单元行进行各种组合,使得半导体装置在功率、性能和面积方面的效率更高,并且连接数量更少和鲁棒性更好;并且本发明实施例的方案可以根据需求自由将不同物理特性的单元行进行组合和搭配,从而提供更多的设计选择,增加设计弹性。

技术研发人员:邱怡洪,池其辉

受保护的技术使用者:联发科技股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!