双源跟随器、缓冲电路以及模数转换器的制作方法

本发明涉及源跟随器,尤其涉及一种双源跟随器、缓冲电路以及模数转换器。

背景技术:

1、源跟随器常作为高速高精度模数转换模器中的输入缓冲器,常用于高速高精度模数转换器的最前端,其线性度直接限制了模数转换器整体的线性度。

2、然而,现有的源跟随器因为输入管沟道长度调制效应,使得现有的源跟随器线性度较差。

技术实现思路

1、本发明提供了一种双源跟随器、缓冲电路以及模数转换器,以抑制源跟随器中输入管的沟道长度调制效应。

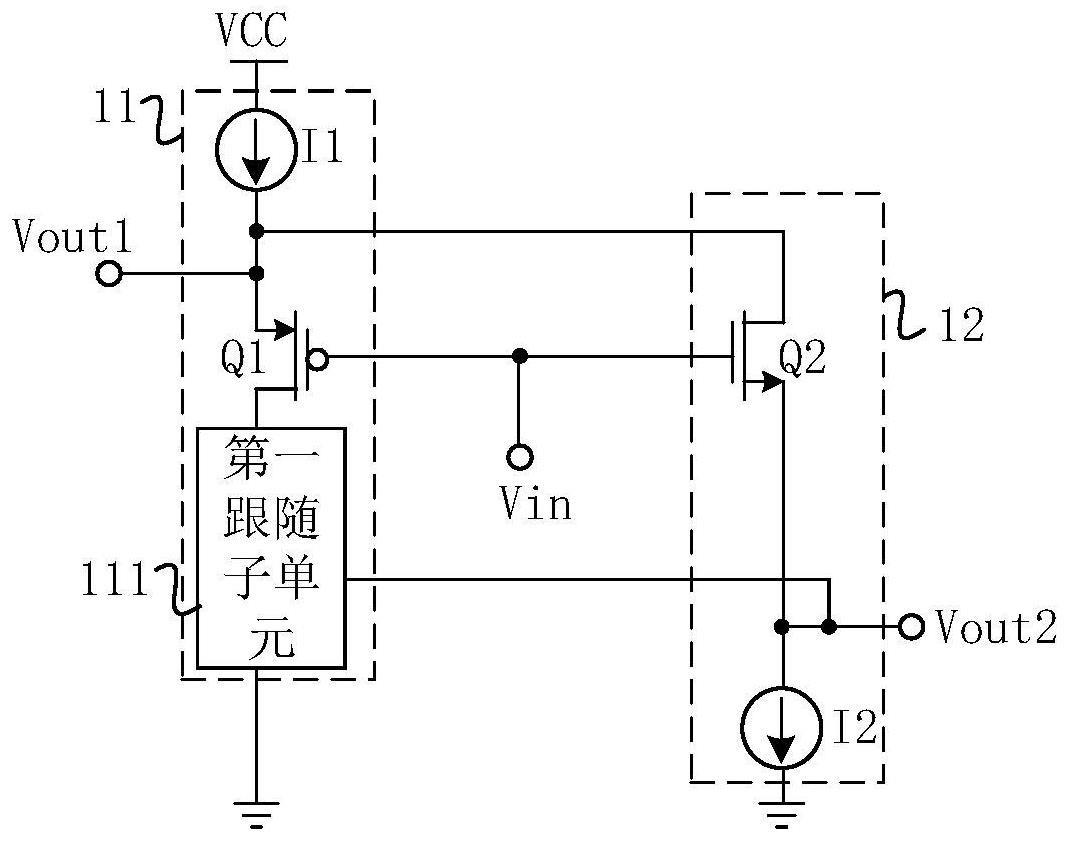

2、根据本发明的一方面,提供了一种双源跟随器,所述双源跟随器包括:第一源跟随器模块和第二源跟随器模块;

3、所述第一源跟随器模块包括串联的第一电流源和第一晶体管,所述第一晶体管的栅极作为所述第一源跟随器模块的输入端,所述第一晶体管的源极作为所述第一源跟随器模块的输出端;所述第二源跟随器模块包括串联的第二电流源和第二晶体管,所述第二晶体管的栅极作为所述第二源跟随器模块的输入端,所述第二晶体管的源极作为所述第二源跟随器模块的输出端;所述第一晶体管与所述第二晶体管的晶体管类型不同;

4、所述第一源跟随器模块还包括第一跟随子单元,所述第一跟随子单元的第一端与所述第一晶体管的漏极电连接,所述第一跟随子单元的第二端与所述双源跟随器的第一电源连接端电连接,所述第一跟随子单元的控制端与所述第二源跟随器模块的输出端电连接,所述第一跟随子单元用于根据其控制端电位调整其第一端电位。

5、可选地,所述第一跟随子单元包括第三晶体管,所述第三晶体管的源极作为所述第一跟随子单元的第一端,所述第三晶体管的漏极作为所述第一跟随子单元的第二端,所述第三晶体管的栅极作为所述第一跟随子单元的控制端;所述第三晶体管的类型与所述第一晶体管的类型相同。

6、可选地,所述第三晶体管的栅长大于所述第一晶体管的栅长。

7、可选地,所述第一源跟随器模块的输出端与所述第二晶体管的漏极电连接。

8、可选地,所述第一晶体管为p型晶体管,所述第二晶体管为n型晶体管;

9、所述第一电流源的第一端与所述双源跟随器的第二电源连接端电连接,所述第一电流源的第二端与所述第一晶体管的源极电连接;

10、所述第二电流源的第一端与所述第一电源连接端电连接,所述第二电流源的第二端与所述第二晶体管的源极电连接,所述第二晶体管的漏极与所述第一晶体管的源极电连接;

11、其中,所述第一电源连接端用于接地,所述第二电源连接端用于连接预设电源。

12、可选地,所述第一晶体管为n型晶体管,所述第二晶体管为p型晶体管;

13、所述第一电流源的第一端与所述双源跟随器的第二电源连接端电连接,所述第一电流源的第二端与所述第一晶体管的源极电连接;

14、所述第二电流源的第一端与所述第一电源连接端电连接,所述第二电流源的第二端与所述第二晶体管的源极电连接,所述第二晶体管的漏极与所述第一晶体管的源极电连接;

15、其中,所述第一电源连接端用于连接预设电源,所述第二电源连接端用于接地。

16、可选地,所述第二源跟随器模块还包括第二跟随子单元;所述第二跟随子单元的第一端与所述第二晶体管的漏极电连接,所述第二跟随子单元的第二端与所述双源跟随器的第二电源连接端电连接,所述第二跟随子单元的控制端与所述第一源跟随器模块的输出端电连接,所述第二跟随子单元用于根据其控制端电位调整其第一端电位。

17、可选地,所述第二跟随子单元包括第四晶体管,所述第四晶体管的源极作为所述第二跟随子单元的第一端,所述第四晶体管的漏极作为所述第二跟随子单元的第二端,所述第四晶体管的栅极作为所述第二跟随子单元的控制端;所述第四晶体管与所述第二晶体管的晶体管类型相同。

18、可选地,所述第一源跟随器模块的输入端与所述第二源跟随器模块的输入端电连接后作为所述双源跟随器的输入端;

19、或者,所述第一源跟随器模块的输入端作为所述双源跟随器的第一输入端,所述第二源跟随器模块的输入端作为所述双源跟随器的第二输入端。

20、根据本发明的另一方面,提供了一种缓冲电路,所述缓冲电路包括上述的双源跟随器。

21、根据本发明的另一方面,提供了一种模数转换器(adc),所述模数转换器包括上述的缓冲电路。

22、本发明实施例的技术方案,采用的双源跟随器包括:第一源跟随器模块和第二源跟随器模块;第一源跟随器模块包括串联的第一电流源和第一晶体管,第一晶体管的栅极作为第一跟随器单元的输入端,第一晶体管的源极作为第一跟随器单元的输出端;第二源跟随器模块包括串联的第二电流源和第二晶体管,第二晶体管的栅极作为第二源跟随器模块的输入端,第二晶体管的源极作为第二源跟随器模块的输出端;第一晶体管与第二晶体管的晶体管类型不同;第一源跟随器模块还包括第一跟随子单元,第一跟随子单元的第一端与第一晶体管的漏极电连接,第一跟随子单元的第二端与双源跟随器的第一电源连接端电连接,第一跟随子单元的控制端与第二源跟随器模块的输出端电连接,第一跟随子单元用于根据其控制端电位调整其第一端电位。通过设置第一源跟随器单元,使得第一晶体管漏极的电位变化趋势与第一晶体管的源极变化趋势相同,从而抑制第一晶体管的沟道长度调制效应,提高第一源跟随器模块的线性度。

23、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种双源跟随器,其特征在于,所述双源跟随器包括:第一源跟随器模块和第二源跟随器模块;

2.根据权利要求1所述的双源跟随器,其特征在于,所述第一跟随子单元包括第三晶体管,所述第三晶体管的源极作为所述第一跟随子单元的第一端,所述第三晶体管的漏极作为所述第一跟随子单元的第二端,所述第三晶体管的栅极作为所述第一跟随子单元的控制端;所述第三晶体管的类型与所述第一晶体管的类型相同。

3.根据权利要求2所述的双源跟随器,其特征在于,所述第三晶体管的栅长大于所述第一晶体管的栅长。

4.根据权利要求1所述的双源跟随器,其特征在于,所述第一源跟随器模块的输出端与所述第二晶体管的漏极电连接。

5.根据权利要求4所述的双源跟随器,其特征在于,所述第一晶体管为p型晶体管,所述第二晶体管为n型晶体管;

6.根据权利要求4所述的双源跟随器,其特征在于,所述第一晶体管为n型晶体管,所述第二晶体管为p型晶体管;

7.根据权利要求1所述的双源跟随器,其特征在于,所述第二源跟随器模块还包括第二跟随子单元;所述第二跟随子单元的第一端与所述第二晶体管的漏极电连接,所述第二跟随子单元的第二端与所述双源跟随器的第二电源连接端电连接,所述第二跟随子单元的控制端与所述第一源跟随器模块的输出端电连接,所述第二跟随子单元用于根据其控制端电位调整其第一端电位。

8.根据权利要求7所述的双源跟随器,其特征在于,所述第二跟随子单元包括第四晶体管,所述第四晶体管的源极作为所述第二跟随子单元的第一端,所述第四晶体管的漏极作为所述第二跟随子单元的第二端,所述第四晶体管的栅极作为所述第二跟随子单元的控制端;所述第四晶体管与所述第二晶体管的晶体管类型相同。

9.一种缓冲电路,其特征在于,所述缓冲电路包括权利要求1-8任一项所述的双源跟随器。

10.一种模数转换器,其特征在于,所述模数转换器包括权利要求9所述的缓冲电路。

技术总结

本发明公开了一种双源跟随器、缓冲电路以及模数转换器。双源跟随器包括:第一源跟随器模块和第二源跟随器模块;第一源跟随器模块包括串联的第一电流源和第一晶体管;第二源跟随器模块包括串联的第二电流源和第二晶体管;第一晶体管与第二晶体管的晶体管类型不同;第一源跟随器模块还包括第一跟随子单元,第一跟随子单元的第一端与第一晶体管的漏极电连接,第一跟随子单元的第二端与双源跟随器的第一电源连接端电连接,第一跟随子单元的控制端与第二源跟随器模块的输出端电连接,第一跟随子单元用于根据其控制端电位调整其第一端电位。本发明能够抑制沟道长度调制效应。

技术研发人员:江帆,周磊,武锦

受保护的技术使用者:苏州迅芯微电子有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!