一种双反馈环路结构的小数分频锁相环电路的制作方法

本申请涉及集成电路,特别是涉及一种双反馈环路结构的小数分频锁相环电路。

背景技术:

1、随着无线通信技术的发展,作为本地振荡器的频率综合器这类集成电路技术应用越来越广泛,其中,小数分频频率综合器(即,小数分频锁相环电路)应用最为广泛。

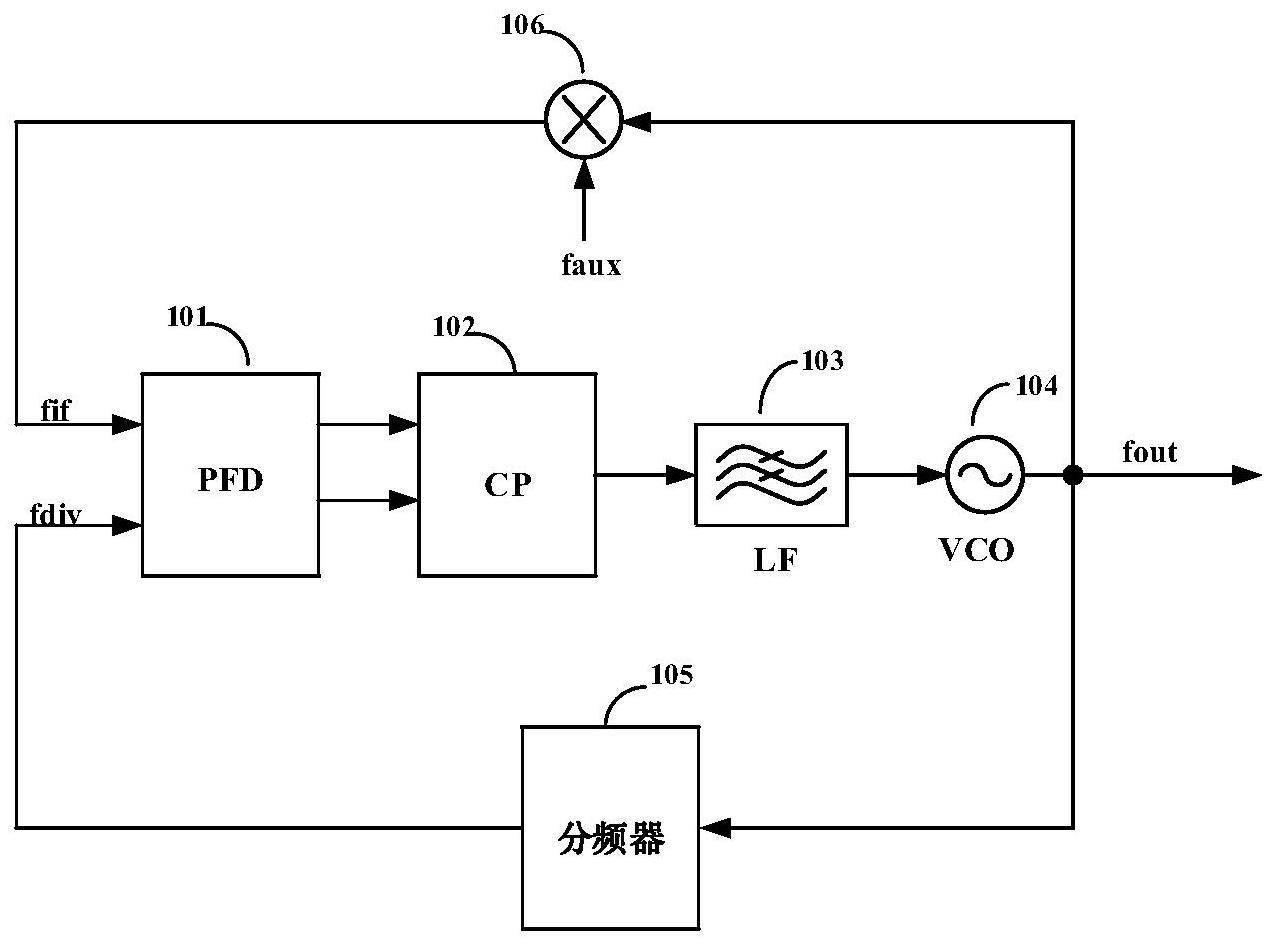

2、图1为本申请所提供的一种小数分频锁相环电路图,如图1所示,当前的小数分频锁相环电路包括鉴频鉴相器(pfd)101,电荷泵(cp)102,环路滤波器(lf)103,压控振荡器(vco)104,以及由差分积分调制器(dsm)和多模分频器(mmd)实现的小数分频器105。其中,小数分频器105的小数分频比为n.f,n为整数部分,f为小数部分。

3、在小数分频锁相环的集成电路系统中,dsm的量化噪声和cp102电流噪声对锁相环输出相位噪声的影响问题,以及与dsm量化噪声、pfd101及cp102非线性相关的带内小数杂散问题,是影响系统性能提高的两大瓶颈。当dsm的量化噪声和cp102电流噪声对锁相环输出的噪声贡献过高,以及带内小数杂散过高时,将会降低锁相环本身输出的频率信号质量,进而也恶化了其应用系统的信噪比,特别是在无线通信应用领域中,甚至会干扰到其他相邻的信道。

4、目前,由于dsm量化噪声和cp102电流噪声在锁相环环路中的传输函数呈低通滤波特性,因此,通常通过减小锁相环的环路带宽,进而抑制小数杂散,以及降低带内噪声贡献,然而,这会导致vco104的相位噪声贡献增加,以及环路锁定时间增加,进而影响了锁相环系统本身输出的频率信号质量,特别是带外噪声性能变差,以及无法满足快速跳频的系统应用需求。

5、由此可见,如何降低dsm量化噪声在锁相环输出端贡献的相位噪声,降低小数杂散,提升系统性能,是本领域技术人员亟待解决的问题。

技术实现思路

1、本申请的目的是提供一种双反馈环路结构的小数分频锁相环电路,降低dsm量化噪声在锁相环输出端贡献的相位噪声,降低杂散,提升系统性能。

2、为解决上述技术问题,本申请提供一种双反馈环路结构的小数分频锁相环电路,包括:鉴频鉴相器,电荷泵,环路滤波器,压控振荡器,分频器和混频器;

3、所述鉴频鉴相器的输出端与所述电荷泵的输入端连接,所述电荷泵的输出端与所述环路滤波器的输入端连接,所述环路滤波器的输出端与所述压控振荡器的输入端连接,所述压控振荡器的输出端作为所述小数分频锁相环电路的输出端;

4、所述压控振荡器的输出端分别与所述混频器的输入端,以及所述分频器的输入端连接,所述混频器的输出端与所述鉴频鉴相器的第一输入端连接,所述分频器的输出端与所述鉴频鉴相器的第二输入端连接,以便构成双反馈环路的锁相环以降低所述小数分频锁相环电路的总反馈系数。

5、优选地,当所述压控振荡器的增益为正数时,所述鉴频鉴相器的第一输入端为正输入端,所述鉴频鉴相器的第二输入端为负输入端;当所述压控振荡器的增益为负数时,所述鉴频鉴相器的第一输入端为负输入端,所述鉴频鉴相器的第二输入端为正输入端,以便于分别基于所述混频器和所述分频器构成两个负反馈环路。

6、优选地,当所述压控振荡器的增益为正数时,所述鉴频鉴相器的第一输入端为负输入端,所述鉴频鉴相器的第二输入端为正输入端,以便于基于所述混频器构成负反馈环路,且基于所述分频器构成正反馈环路。

7、优选地,当所述压控振荡器的增益为负数时,所述鉴频鉴相器的第一输入端为正输入端,所述鉴频鉴相器的第二输入端为负输入端,以便于基于所述混频器构成负反馈环路,且基于所述分频器构成正反馈环路。

8、优选地,电荷泵的输出电流可调节为:

9、

10、其中,所述icp为电荷泵的默认电流,所述n.f为所述分频器的分频比,n为整数部分,f为小数部分。

11、优选地,所述混频器为混频系数大于或等于2的混频器。

12、优选地,所述分频器包括小数分频器和整数分频器。

13、本发明所提供的一种双反馈环路结构的小数分频锁相环电路,包括:鉴频鉴相器,电荷泵,环路滤波器,压控振荡器,分频器和混频器。鉴频鉴相器的输出端与电荷泵的输入端连接,电荷泵的输出端与环路滤波器的输入端连接,环路滤波器的输出端与压控振荡器的输入端连接,压控振荡器的输出端作为小数分频锁相环电路的输出端。压控振荡器的输出端分别与混频器的输入端,以及分频器的输入端连接,且混频器的输出端与鉴频鉴相器的第一输入端连接,分频器的输出端与鉴频鉴相器的第二输入端连接,以便构成双反馈环路的锁相环以降低小数分频锁相环电路的总反馈系数。由此可见,本申请所提供的技术方案,分别基于分频器和混频器构建两条反馈环路,并分别与鉴频鉴相器的第一输入端和第二输入端连接,以便降低小数分频锁相环电路的总反馈系数,进而降低带内噪声贡献,并抑制小数杂散,提升系统的整体性能,并且可避免通过减小锁相环的环路带宽以降低带内噪声贡献和抑制小数杂散,所导致压控振荡器相位噪声贡献和环路锁定时间增加的问题。

技术特征:

1.一种双反馈环路结构的小数分频锁相环电路,其特征在于,包括:鉴频鉴相器,电荷泵,环路滤波器,压控振荡器,分频器和混频器;

2.根据权利要求1所述的双反馈环路结构的小数分频锁相环电路,其特征在于,当所述压控振荡器的增益为正数时,所述鉴频鉴相器的第一输入端为正输入端,所述鉴频鉴相器的第二输入端为负输入端;当所述压控振荡器的增益为负数时,所述鉴频鉴相器的第一输入端为负输入端,所述鉴频鉴相器的第二输入端为正输入端,以便于分别基于所述混频器和所述分频器构成两个负反馈环路。

3.根据权利要求1所述的双反馈环路结构的小数分频锁相环电路,其特征在于,当所述压控振荡器的增益为正数时,所述鉴频鉴相器的第一输入端为负输入端,所述鉴频鉴相器的第二输入端为正输入端,以便于基于所述混频器构成负反馈环路,且基于所述分频器构成正反馈环路。

4.根据权利要求3所述的双反馈环路结构的小数分频锁相环电路,其特征在于,当所述压控振荡器的增益为负数时,所述鉴频鉴相器的第一输入端为正输入端,所述鉴频鉴相器的第二输入端为负输入端,以便于基于所述混频器构成负反馈环路,且基于所述分频器构成正反馈环路。

5.根据权利要求1至4任意一项所述的双反馈环路结构的小数分频锁相环电路,其特征在于,电荷泵的输出电流可调节为:

6.根据权利要求5所述的双反馈环路结构的小数分频锁相环电路,其特征在于,所述混频器为混频系数大于或等于2的混频器。

7.根据权利要求6所述的双反馈环路结构的小数分频锁相环电路,其特征在于,所述分频器包括小数分频器和整数分频器。

技术总结

本申请涉及集成电路技术领域,公开了本发明所提供的一种双反馈环路结构的小数分频锁相环电路,包括:鉴频鉴相器,电荷泵,环路滤波器,压控振荡器,分频器和混频器。鉴频鉴相器的输出端与电荷泵的输入端连接,电荷泵的输出端与环路滤波器的输入端连接,环路滤波器的输出端与压控振荡器的输入端连接,压控振荡器的输出端作为小数分频锁相环电路的输出端。压控振荡器的输出端分别与混频器的输入端,以及分频器的输入端连接,且混频器的输出端与鉴频鉴相器的第一输入端连接,分频器的输出端与鉴频鉴相器的第二输入端连接,构成双反馈环路的锁相环,从而降低锁相环电路的总反馈系数,使得带内噪声得到降低,并抑制小数杂散,提升系统的整体性能。

技术研发人员:唐立田,朱雄辉,李晔

受保护的技术使用者:泛升云微电子(苏州)有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!