半导体存储器底层电路及制备方法与流程

本发明涉及集成电路技术,特别涉及半导体存储器技术。

背景技术:

1、当前3d存储器(例如nand、阻变存储器、相变存储器等)通常采用平面工艺的mos管作为3d存储器垂直位线的选择管。由于平面mos选择管的关键尺寸和占用面积需要与高度紧密的3d存储器阵列适配,因此采用平面mos选择管受平面工艺所限,可导致后续堆叠的3d存储器占用较大芯片面积。因此其缺点是占用芯片面积较大,与高度紧凑的3d存储阵列不兼容。另一种垂直位线选择管则是应用垂直mos选择管,其垂直朝向的mos通道与3d垂直位线处于一条线,由朝向相互正交且交错的水平源极选择线和水平栅极选择线共同控制垂直mos管的导通情况,从而对与垂直mos管漏极相连的位线的进行选择。3d存储器阵列正下方的垂直mos选择管虽与高度紧密的3d存储器阵列适配,但需要将选择管设置在下方衬底的有源区(active area)之内,则其他必需的外围电路(如i/o电路、控制电路等)只能设置于占用芯片绝大部分面积的3d存储器阵列的外围,进一步占用一定芯片面积。一种设置在衬底上而非衬底下的垂直mos选择管(us 9,065,044 b2)避开了上述问题,但是需要复杂难控的高温退火工艺进行重掺杂的源极向不同导电类型的轻掺杂mos通道进行对外扩散(out-diffusion),其工艺成本较高。

技术实现思路

1、本发明所要解决的技术问题是,提供一种占用芯片面积更小的半导体存储器底层电路及制备方法。

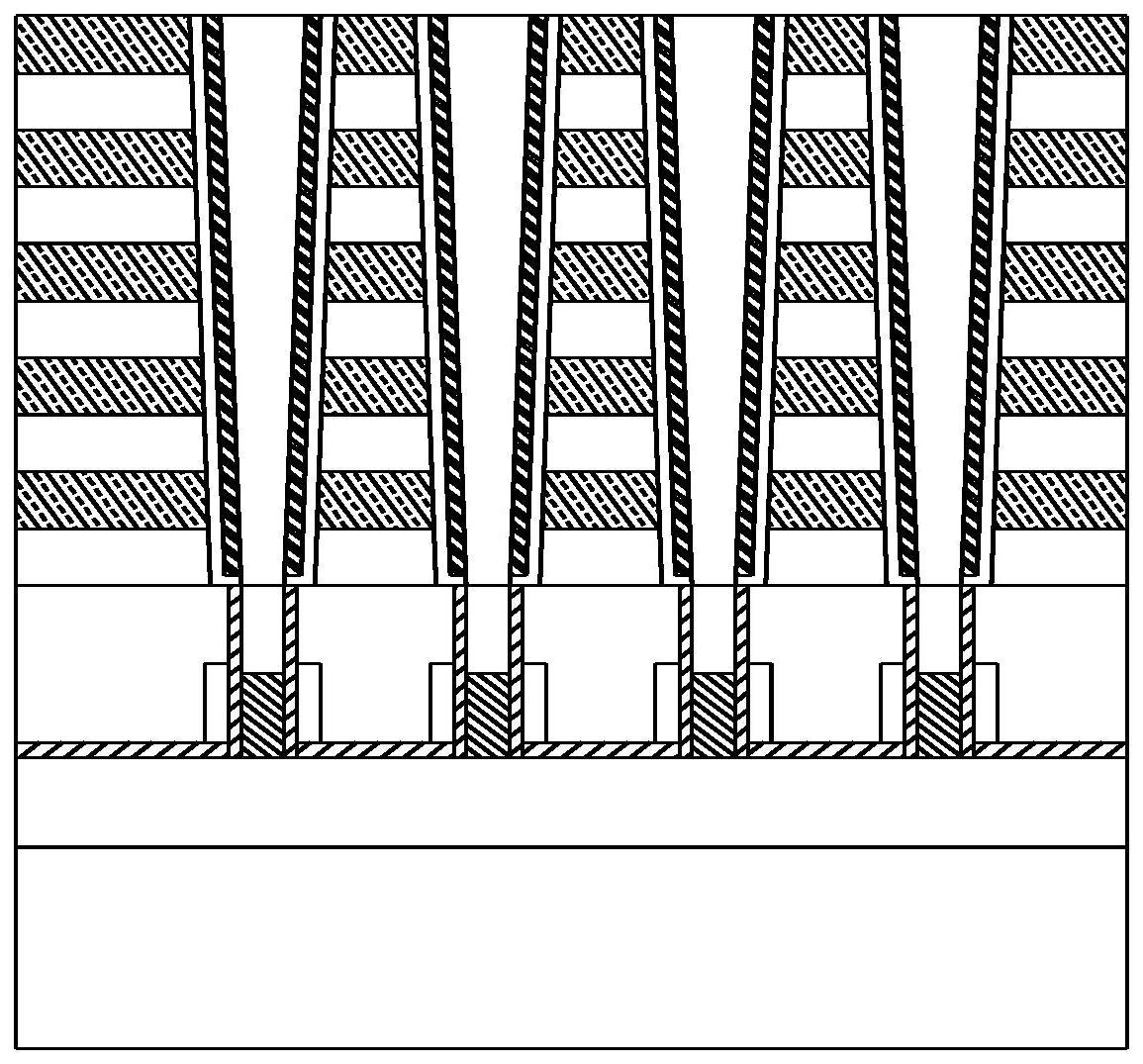

2、本发明解决所述技术问题采用的技术方案是,半导体存储器底层电路,其特征在于,包括设置于行线层上方的列线层,行线层和列线层之间为层间绝缘隔离层,位线接触层位于列线层上方,行线层内设置有预定数量的、由重掺杂半导体的低阻材料构成的行线,列线层内设置有预定数量的、由导电材料构成的列线,行线和列线的方向相互垂直;在行线和列线交叉处设置有贯穿位线接触层、列线层和层间绝缘隔离层的mos孔;位线接触层内对应mos孔位置填充半导体材料,半导体材料掺杂类型与行线相同;

3、所述mos孔内与列线层和层间绝缘隔离层对应位置填充半导体材料,半导体材料的掺杂类型与行线相反并与行线接触,mos孔内上下两段半导体材料直接接触;

4、填充于mos孔内的半导体材料和mos孔的内壁之间通过栅极绝缘层隔离。

5、进一步的,所述mos孔为矩形孔,也可以是椭圆、圆形等。

6、所述列线的材料为掺杂半导体材料、金属、金属硅化物等低阻材料。

7、本发明还提供一种半导体存储器底层电路的制备方法,包括下述步骤:

8、(1)底部基础电路层上设置行线层,所述行线层内具有并列的、预定数量的行线,所述行线由高掺杂的低阻半导体材料构成;

9、(2)在行线层上方覆盖一层层间绝缘隔离层,然后在层间绝缘隔离层上方设置列线层,所述列线层内具有并列的、预定数量的列线,列线垂直于行线,列线由导电材料构成;

10、(3)在列线层上方覆盖绝缘介质材料,作为位线接触层。

11、(4)在行线和列线交叉处开设贯穿位线接触层、列线层和层间绝缘隔离层的孔,行线暴露于孔的底部,孔的开口位于位线接触层的上表面;

12、(5)在孔的内壁覆盖一层栅极绝缘介质材料,然后清除孔底的栅极绝缘介质材料,在孔底暴露出行线;

13、(6)在孔内与列线层和层间绝缘隔离层对应位置,填充掺杂类型与行线相反的半导体材料,然后在孔内余下部分填充掺杂类型与行线相同的半导体材料;或在孔内完全填充掺杂类型与行线相反的半导体材料,然后在对应位线接触层位置通过杂质注入形成与行线导电类型相同的半导体材料。

14、还包括下述步骤:

15、将各行线和各列线连接到底部基础电路层。将位线接触层的mos孔上端连接到上方三维存储器件的垂直位线。

16、本发明的有益效果是,能够很好地控制和选择由三维存储器阵列的多个分离堆叠层中的一组存储器单元共享的垂直位线。本发明并不占用可用于其他存储电路的下方区域,从而得以减小3d存储芯片的尺寸。本发明制备工艺简单,成本低。

技术特征:

1.半导体存储器底层电路,其特征在于,包括设置于行线层上方的列线层,行线层和列线层之间为绝缘隔离层,行线层内设置有预定数量的、由掺杂半导体材料构成的行线,列线层内设置有预定数量的、由导电材料构成的列线,行线和列线的方向相互垂直;在行线和列线交叉处设置有贯穿列线层和绝缘隔离层的mos孔;

2.如权利要求1所述的半导体存储器底层电路,其特征在于,所述mos孔为矩形孔。

3.如权利要求1所述的半导体存储器底层电路,其特征在于,所述列线的材料为掺杂半导体材料。

4.半导体存储器底层电路的制备方法,其特征在于,包括下述步骤:

5.如权利要求4所述的半导体存储器底层电路的制备方法,其特征在于,还包括下述步骤:

技术总结

半导体存储器底层电路及制备方法,涉及集成电路技术。本发明的半导体存储器底层电路,其特征在于,包括设置于行线层上方的列线层,行线层和列线层之间为绝缘隔离层,行线层内设置有预定数量的、由掺杂半导体材料构成的行线,列线层内设置有预定数量的、由导电材料构成的列线,行线和列线的方向相互垂直;在行线和列线交叉处设置有贯穿列线层和绝缘隔离层的MOS孔;所述MOS孔内填充有上下两段半导体材料,位于MOS孔上段的半导体材料的掺杂类型与行线相同,位于MOS孔下段的半导体材料的掺杂类型与行线相反并与行线接触,上下两段半导体材料直接接触;填充于MOS孔内的半导体材料和MOS孔的内壁之间通过绝缘层隔离。本发明能够很好地控制和选择由三维存储器阵列的多个分离堆叠层中的一组存储器单元共享的垂直位线。

技术研发人员:彭泽忠,王苛

受保护的技术使用者:成都皮兆永存科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!