多层电路板及其制作方法与流程

【】本发明涉及印刷电路板,尤其涉及一种多层电路板及其制作方法。

背景技术

0、

背景技术:

1、随着通信技术及设备朝着高频高速、集成化以及小型化的路线发展,对用于承载电子元器件的印刷线路板(printed circuit board,pcb)的线路层数及其之间的连接提出了更高的要求,总是期待能够提供集成密度更高的多层任意阶互连线路板。

2、但是,传统的任意阶互连线路板的层数一般不超过20层。而且,传统的多层线路板采用的是逐层堆叠增层的制作工序,其需要经过多次的压合、钻孔、电镀、线路制作等工序。这使得线路板的生产工序流程长,存在诸如良率低,成本高以及对材料的耐热性要求较高等的缺陷。

技术实现思路

0、

技术实现要素:

1、本申请实施例提供一种多层电路板及其制作方法,旨在解决现有多层线路板制作工序中存在的至少一部分问题。

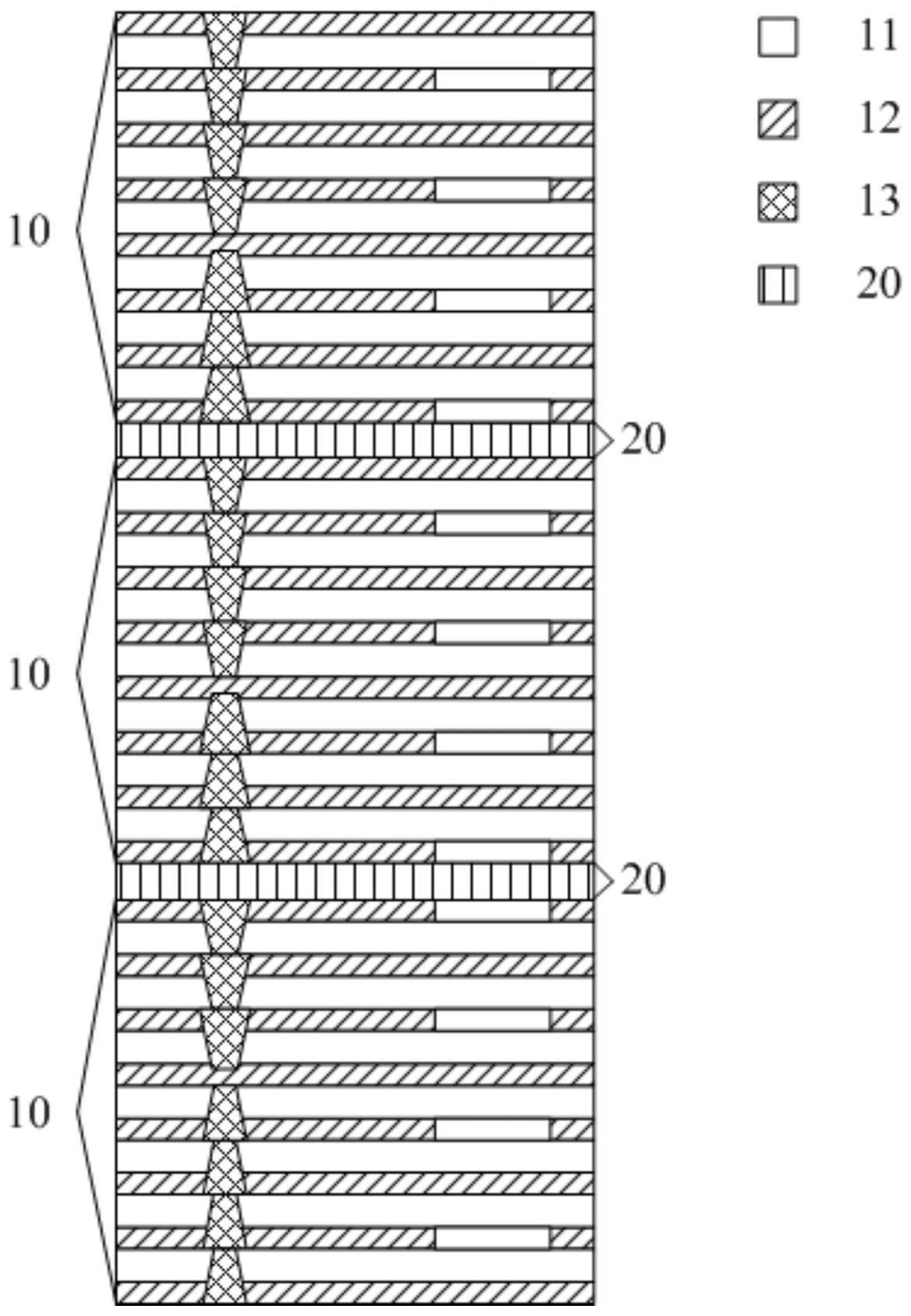

2、第一方面,本申请实施例提供了一种多层电路板的制作方法。该方法包括:制作n个电路板单元;每个所述电路板单元具有若干层线路;制作m个异方性导电胶层;其中,n为大于等于2的正整数,m与n之间的差值为1;堆叠所述电路板单元和所述异方性导电胶层,形成交替的层叠结构;其中,在所述层叠结构中,相邻的两个所述电路板单元之间具有一个异方性导电胶层;压合所述层叠结构,以使所述异方性导电胶层与相邻的两个所述电路板单元粘合固定。

3、可选地,所述制作m个异方性导电胶层,具体包括:根据所述电路板单元的尺寸,裁切异方性导电胶,以获得与所述电路板单元的尺寸相同的异方性导电胶层。

4、可选地,所述堆叠所述电路板单元和所述异方性导电胶层,形成交替的层叠结构,具体包括:通过具有电荷耦合器件检测部件的堆叠设备,依次堆叠所述电路板单元和所述异方性导电胶层,以使所述电路板单元与所述异方性导电胶层在高度方向上对齐。

5、可选地,所述压合所述层叠结构,以使所述异方性导电胶层与相邻的两个所述电路板单元粘合固定,具体包括:以预设的压合温度和压合压力,通过预设的压合时间,压合所述层叠结构。

6、可选地,所述预设的压合温度为100-200℃。

7、可选地,所述预设的压合压力为10-20kg/cm2。

8、可选地,所述预设的压合时间为10-30秒。

9、第二方面,本申请实施例提供了一种多层电路板。该多层电路板应用如上所述的制作方法制作获得,包括至少两个电路板单元和至少一个异方性导电胶层,所述异方性导电胶层位于两个电路板单元之间。

10、可选地,一个所述电路板单元内的不同层的线路之间通过电镀孔导通;相邻两个所述电路板单元之间的不同层线路之间通过所述异方性导电胶层导通。

11、可选地,每个所述电路板单元具有2至10层线路;所述电路板单元的线路层数为偶数。

12、本申请实施例提供的多层电路板制作方法的其中一个有利方面是:使用异方性导电胶作为连接和粘合固定电路板单元的连接部分,可以将多层高密度电路板拆分为多个层数较少的电路板单元分别制作。

13、由此,相对于逐层堆叠增层的制作方法而言,在制作相同层数的多层电路板时,能够大幅度的降低压合、钻孔、电镀、线路制作等工序的执行次数,从而达到提升产品良率,降低生产制造成本以及对材料的耐热性要求的效果。

14、以下详细描述上述方法、装置和组件的有利方面的更多实施例。在本说明书中所有的公开仅是示例性的,本领域技术人员可以在不脱离所公开和所主张的本申请的发明精神和范围的情况下,容易地做出适当调整。

技术特征:

1.一种多层电路板的制作方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,所述制作m个异方性导电胶层,具体包括:

3.根据权利要求2所述的方法,其特征在于,所述堆叠所述电路板单元和所述异方性导电胶层,形成交替的层叠结构,具体包括:

4.根据权利要求2所述的方法,其特征在于,所述压合所述层叠结构,以使所述异方性导电胶层与相邻的两个所述电路板单元粘合固定,具体包括:

5.根据权利要求4所述的方法,其特征在于,所述预设的压合温度为100-200℃。

6.根据权利要求4所述的方法,其特征在于,所述预设的压合压力为10-20kg/cm2。

7.根据权利要求4所述的方法,其特征在于,所述预设的压合时间为10-30秒。

8.一种多层电路板,其特征在于,应用如权利要求1-7任一项所述的制作方法制作获得,包括至少两个电路板单元和至少一个异方性导电胶层;所述异方性导电胶层位于两个电路板单元之间。

9.根据权利要求8所述的方法,其特征在于,同一个所述电路板单元内的不同层的线路之间通过电镀孔导通;

10.根据权利要求8所述的方法,其特征在于,每个所述电路板单元具有2至10层线路;所述电路板单元的线路层数为偶数。

技术总结

本申请实施例提供了一种多层电路板及其制作方法。该制作方法包括:制作N个电路板单元;每个所述电路板单元具有若干层线路;制作M个异方性导电胶层;其中,N为大于等于2的正整数,M与N之间的差值为1;交替堆叠N个所述电路板单元和M个所述异方性导电胶层,形成层叠结构;其中,在所述层叠结构中,相邻的两个所述电路板单元之间具有一个异方性导电胶层;压合所述层叠结构,以使所述异方性导电胶层与相邻的两个所述电路板单元粘合固定。通过额外设置的异方性导电胶层,可以将多层电路板拆分为多个层数较少的电路板单元,从而大幅度的降低了压合、钻孔、电镀、线路制作等工序的执行次数,达到提升产品良率,降低生产制造成本以及对材料的耐热性要求的效果。

技术研发人员:张昕,徐颖龙,虞成城

受保护的技术使用者:深圳市信维通信股份有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!