电容结构的制作方法

本技术涉及半导体制造,尤其涉及一种电容结构。

背景技术:

1、随着半导体集成电路的制造技术的不断进步,也伴随着器件小型化和微型化的进程。电容结构是集成电路的重要组成单元,集成电路芯片中的电容结构多种多样,如:mos(metal-oxide-semiconductorfield金属-氧化物-半导体)场效应管电容;pip(polysilicon-insulator-polysilicon多晶硅-绝缘体-多晶硅)电容,可变结电容以及后段互联中的mim(metal-insulator-metal金属-绝缘体-金属)电容和mom(metal-oxide-metal金属-氧化物-金属)电容。

2、目前最常用的后段互联电容结构有两种:mim电容和mom电容。mim电容和mom电容存在于后段互联层结构不占用器件层的面积,且电容的线性特征要远好于其他类型的电容。mom电容主要利用上下层金属导线和同层金属之间形成的整体电容,该种电容的优点是其可以用现有的互联制造工艺来实现,即可以同时完成mom电容与铜互联结构。

3、mim电容结构简单,可以具有最小的电阻率,并且由于内部耗尽以及相对较大的电容而基本上不会存在寄生电容。因此,在半导体器件中,尤其是在高频器件中,通常会选用mim电容器。虽然为了形成mim电容需要更多的掩模版和更加复杂的制程,但是mim电容能够提供更加稳定的电容,并且能够提供的电容更大。因此,mim电容仍然得到广泛运用。

4、然而,现有技术中的mim电容仍存在诸多问题。

技术实现思路

1、本实用新型解决的技术问题是提供一种电容结构,以提升电容结构的击穿电压和电容结构的可靠性。

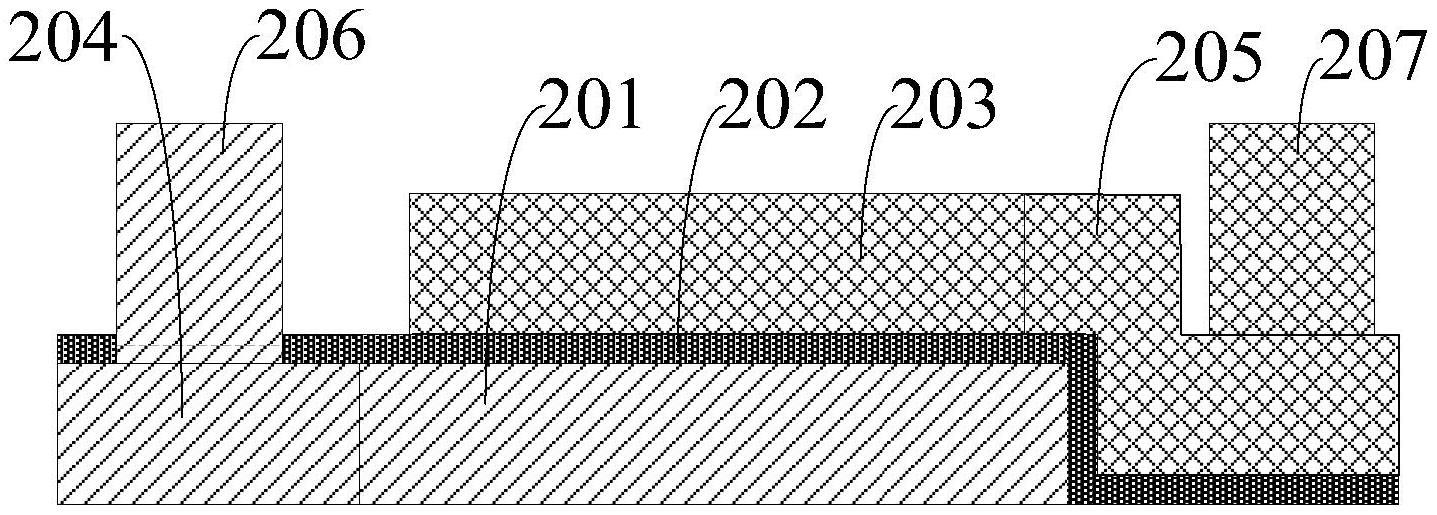

2、为解决上述问题,本实用新型提供一种电容结构,包括:衬底;位于所述衬底上的第一电极层,所述第一电极层在所述衬底上具有第一投影图形;位于所述第一电极层上的第一绝缘层;位于所述第一绝缘层上的第二电极层,所述第二电极层在所述衬底上具有第二投影图形,所述第二投影图形的各边内缩于所述第一投影图形的投影范围内。

3、可选的,所述第二投影图形的各边以固定尺寸内缩于所述第一投影图形的投影范围内。

4、可选的,所述固定尺寸的范围:0.1微米~0.3微米。

5、可选的,还包括:第三电极层,位于所述第二电极层上方;第二绝缘层,位于所述第三电极层与所述第二电极层之间。

6、可选的,所述第三电极层在所述衬底上具有第三投影图形,所述第三投影图形的各边内缩于所述第二投影图形的投影范围内。

7、可选的,所述第三投影图形的各边以固定尺寸内缩于所述第二投影图形的投影范围内。

8、可选的,所述固定尺寸的范围:0.1微米~0.3微米。

9、可选的,还包括:与所述第一电极层连接的第一引线层;与所述第二电极层连接的第二引线层,所述第一引线层和所述第二引线层分别位于所述第一电极层相对的两侧,且所述第一绝缘层位于所述第一电极层和所述第二引线层之间;与所述第一引线层连接的第一引线;与所述第二引线层连接的第二引线。

10、可选的,所述第一投影图形包括:矩形。

11、可选的,所述第二投影图形包括:矩形。

12、与现有技术相比,本实用新型的技术方案具有以下优点:

13、在本实用新型技术方案的电容结构中,由于所述第二电极层的第二投影图形的各边内缩于所述第一电极层的第一投影图形的投影范围内,因此所述第一电极层和所述第二电极层的相对应的各边沿在垂直于所述衬底表面的方向上相互错开,避免所述第一电极层和所述第二电极层的边沿放电在垂直于所述衬底表面方向上形成正对,进而减少由于正对的放电而击穿所述第一绝缘层的问题,以此提升所述电容结构的击穿电压和电容结构的可靠性。

14、进一步,所述第三电极层在所述衬底上具有第三投影图形,所述第三投影图形的各边内缩于所述第二投影图形的投影范围内。通过将所述第二电极层和所述第三电极层之间的相对应的各边沿在垂直于所述衬底表面的方向上相互错开,避免所述第二电极层和所述第三电极层之间的边沿放电在垂直于所述衬底表面方向上形成正对,进而减少由于正对的放电而击穿所述第二绝缘层的问题,以此提升所述电容结构的击穿电压和电容结构的可靠性。

技术特征:

1.一种电容结构,其特征在于,包括:

2.如权利要求1所述的电容结构,其特征在于,所述第二投影图形的各边以固定尺寸内缩于所述第一投影图形的投影范围内。

3.如权利要求2所述的电容结构,其特征在于,所述固定尺寸的范围:0.1微米~0.3微米。

4.如权利要求1所述的电容结构,其特征在于,还包括:第三电极层,位于所述第二电极层上方;第二绝缘层,位于所述第三电极层与所述第二电极层之间。

5.如权利要求4所述的电容结构,其特征在于,所述第三电极层在所述衬底上具有第三投影图形,所述第三投影图形的各边内缩于所述第二投影图形的投影范围内。

6.如权利要求5所述的电容结构,其特征在于,所述第三投影图形的各边以固定尺寸内缩于所述第二投影图形的投影范围内。

7.如权利要求6所述的电容结构,其特征在于,所述固定尺寸的范围:0.1微米~0.3微米。

8.如权利要求1所述的电容结构,其特征在于,还包括:与所述第一电极层连接的第一引线层;与所述第二电极层连接的第二引线层,所述第一引线层和所述第二引线层分别位于所述第一电极层相对的两侧,且所述第一绝缘层位于所述第一电极层和所述第二引线层之间;与所述第一引线层连接的第一引线;与所述第二引线层连接的第二引线。

9.如权利要求1所述的电容结构,其特征在于,所述第一投影图形包括:矩形。

10.如权利要求1所述的电容结构,其特征在于,所述第二投影图形包括:矩形。

技术总结

一种电容结构,包括:衬底;位于所述衬底上的第一电极层,所述第一电极层在所述衬底上具有第一投影图形;位于所述第一电极层上的第一绝缘层;位于所述第一绝缘层上的第二电极层,所述第二电极层在所述衬底上具有第二投影图形,所述第二投影图形的各边内缩于所述第一投影图形的投影范围内。由于第二电极层的第二投影图形的各边内缩于第一电极层的第一投影图形的投影范围内,因此第一电极层和第二电极层的相对应的各边沿在垂直于所述衬底表面的方向相互错开,避免所述第一电极层和所述第二电极层的边沿放电在垂直于所述衬底表面方向形成正对,减少由于正对的放电击穿所述第一绝缘层的问题,提升所述电容结构的击穿电压和电容结构的可靠性。

技术研发人员:邹道华,高谷信一郎,刘昱玮,黄仁耀

受保护的技术使用者:常州承芯半导体有限公司

技术研发日:20220810

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!