锁相环杂散消减电路及锁相环电路的制作方法

本技术属于电子电路,涉及一种杂散消减电路,尤其涉及一种锁相环杂散消减电路及锁相环电路。

背景技术:

1、通信系统日益复杂,对时钟电路的噪声性能要求逐渐提高。在极低抖动时钟系统中,杂散引入的时钟抖动占比越来越大,因此减小甚至消除杂散变得日益重要。

2、随着制造工艺的进步,数字电路由于其易于实现、移植以及面积小的特点,越来越广泛的被应用于锁相环的设计当中,也就是业界所熟知的adpll(全数字相位锁定环)。然而锁相环本质上还是一个模拟系统,比如pll(锁相环)中必不可少的vco(压控振荡器),其输出的相位信息是模拟量,从而跟随其后的fbdv(反馈分频器)的输出相位也是模拟量,因此adpll中数字电路与模拟电路的通信必然需要相应的接口电路。传统数字与模拟之间的通信依赖于adc(模拟数字转换器)和dac(数字模拟转换器),相应的在adpll系统中tdc(时间到数字信号转换器)负责将模拟域中的相位信息(与时间信息等效)转化成数字信号,dtc(数字时间转换器)负责将数字信号转换成相位信息。

3、图1为现有锁相环系统的组成框图,如图1所示,dtc被用作补偿sdm(积分微分调制器)产生的量化噪声。理想情况下,sdm产生的量化噪声能够被dtc完全抵消掉,从而将分数分频等效为整数分频,因此当完美抵消能够被实现时,分数杂散就能被消除。可惜在电路实现过程中,非理想因素是不可避免的。类似于传统混合信号系统中的dac,对于dtc而言,其dnl(微分非线性)和inl(积分非线性)通常被用来衡量其性能的优劣。而dnl与inl在adpll中具体影响则为带内噪声以及分数杂散能量的大小。从上述讨论来看,改善dtc的dnl与inl似乎是最直接的办法。但是业内人士均可所见的是,模拟电路设计就是在性能,功耗和面积上多方面均衡考量的一门艺术。从dtc电路着手改善,势必增加面积消耗,或者功耗增大等负面影响。

4、在国际顶级论文当中有不少阐述如何改善dtc的线性度以降低分数杂散能量的方法。

5、文献1(isscc2017,yuminghe,‘a673μw1.8-to-2.5ghzdividerlessfractional-ndigitalpllwithaninherentfrequency-capturecapabilityandaphase-ditheringspurmitigationforiotapplications’)中则引入多抽头的lms(最小均方误差算法),将整个dtc量程范围分为若干个子范围,每一段单独做增益补偿,在一定程度能够改善dtc的线性度从而降低分数杂散的能量。多抽头lms实现起来显著增大了数字电路的规模,并且同时需要急剧延长整个adpll的校准时间(多抽头会显著延长lms的收敛时间)。

6、文献2(isscc2020,taehoseong,‘a-58dbc-worst-fractional-spurand-234db-fom jitter5.5ghzring-dco-basedfractional-ndpllusingatime-invariant-probability modulator,generatinganonlinearity-robustdtc-controlword’)中在数字算法中加入tipm(时不变概率调制器)将dtc带分数杂散相关模式的控制字打散为随机控制字从而消除分数杂散。但为此必须加入另一个dtc作为互补,从而增加了电路开销以及功耗。

7、有鉴于此,如今迫切需要设计一种新的杂散消减方式,以便克服现有杂散消减方式存在的上述至少部分缺陷。

技术实现思路

1、本实用新型提供一种锁相环杂散消减电路及锁相环电路,可有效降低dtc非线性导致的杂散能量,并且能够一定程度抵消其他通路的杂散,改善整个pll系统的抖动。

2、为解决上述技术问题,根据本实用新型的一个方面,采用如下技术方案:

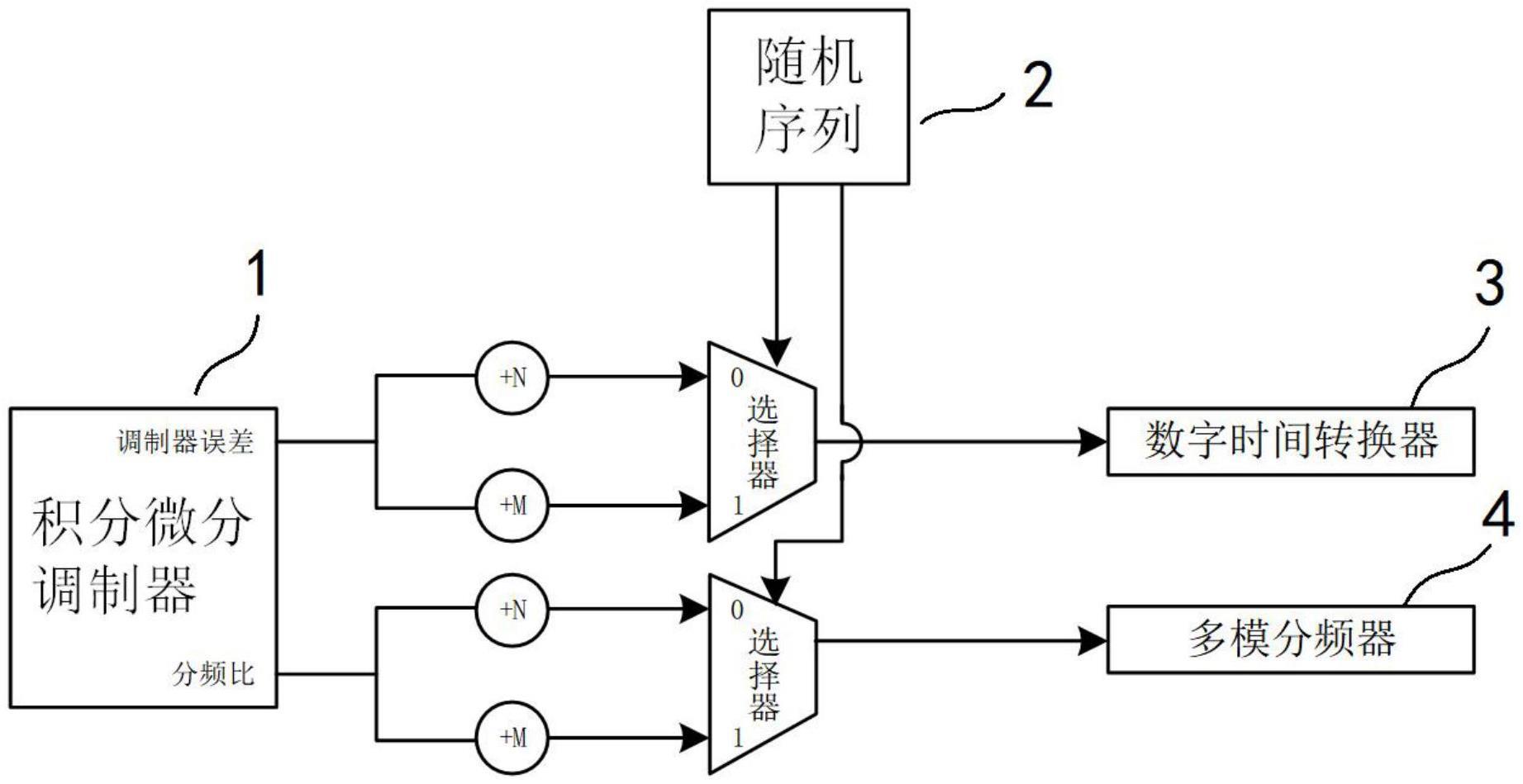

3、一种锁相环杂散消减电路,所述杂散消减电路包括:积分微分调制器sdm、随机序列发生器、第一选择器、第二选择器、数字时间转换器dtc及多模分频器;

4、所述积分微分调制器sdm用以输出调制器误差信号及分频比信号;所述积分微分调制器sdm的第一输出端输出调制器误差信号,所述积分微分调制器sdm的第一输出端连接第一选择器的输入端;

5、所述积分微分调制器sdm的第二输出端输出分频比信号,所述积分微分调制器sdm的第二输出端连接第二选择器的输入端;

6、所述随机序列发生器的输出端分别连接所述第一选择器的输入端及所述第二选择器的输入端;

7、所述第一选择器的输入端分别连接所述积分微分调制器sdm的输出端及所述随机序列发生器的输出端;所述第一选择器的输出端向所述数字时间转换器dtc输出由所述积分微分调制器sdm输出的调制器误差结合第一选择器选择的随机数形成的第一输出数据;

8、所述第二选择器的输入端分别连接所述积分微分调制器sdm的输出端及所述随机序列发生器的输出端;所述第二选择器的输出端向所述多模分频器输出由所述积分微分调制器sdm输出的分频比结合第二选择器选择的随机数形成的第二输出数据。

9、根据本实用新型的另一个方面,采用如下技术方案:一种锁相环电路,所述锁相环电路包括上述的锁相环杂散消减电路。

10、本实用新型的有益效果在于:本实用新型提出的锁相环杂散消减电路及锁相环电路,可有效降低dtc非线性导致的杂散能量,并且能够一定程度抵消其他通路的杂散,改善整个pll系统的抖动。

11、利用本实用新型电路,模拟电路无需任何改动,这意味着不增加面积及能量的消耗。本实用新型不依赖于sdm,dtc以及fbdiv的具体实现方式,其适用范围更广、更全面。

技术特征:

1.一种锁相环杂散消减电路,其特征在于,所述杂散消减电路包括:积分微分调制器sdm、随机序列发生器、第一选择器、第二选择器、数字时间转换器dtc及多模分频器;

2.一种锁相环电路,其特征在于,所述锁相环电路包括权利要求1所述的锁相环杂散消减电路。

技术总结

本技术揭示了一种锁相环杂散消减电路及锁相环电路,所述杂散消减电路包括积分微分调制器SDM、随机序列发生器、第一选择器、第二选择器、数字时间转换器DTC及多模分频器;积分微分调制器SDM输出调制器误差信号及分频比信号;随机序列发生器的输出端分别连接第一选择器及第二选择器;第一选择器的输出端向数字时间转换器DTC输出由积分微分调制器SDM输出的调制器误差结合第一选择器选择的随机数形成的第一输出数据;第二选择器的输出端向多模分频器输出由积分微分调制器SDM输出的分频比结合第二选择器选择的随机数形成的第二输出数据。本技术可有效降低DTC非线性导致的杂散能量,并且能够一定程度抵消其他通路的杂散,改善整个PLL系统的抖动。

技术研发人员:颜文,刘钊,章松,李冬,韩洪征,宋永华

受保护的技术使用者:博流智能科技(南京)有限公司

技术研发日:20221216

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!