功率放大器均衡器的制作方法

背景技术:

1、(1)技术领域

2、本发明涉及电子电路,并且更具体地涉及电子放大器电路。

3、(2)背景技术

4、包括功率放大器(pa)和低噪声放大器(lna)的电子放大器用于多个电子系统特别是射频(rf)系统(例如,无线电、蜂窝电话、wifi等)中。在许多应用中,放大器特别是功率放大器的重要设计参数包括幅度-幅度调制(am-am)变化与输出功率的关系、幅度-相位调制(am-pm)变化与输出功率的关系、功率附加效率(pae)、功率以及线性度。

5、am-am转换是由于不期望的幅度变化而发生的非线性失真的量度。更特别地,am-am失真是作为输入幅度的函数的增益特性的大小的失真。输入幅度调制增益并且因此调制输出幅度。am-am失真的示例是放大器的压缩特性,其中高输入信号使增益特性偏离线性响应。增益的压缩意味着输出幅度的增加小于输入幅度的相关联增加。还可以观察增益扩展。这通常在放大器开始压缩之前发生在ab类放大器中。

6、am-pm转换是由系统的幅度变化(am)引起的一定量的不期望的相位偏差(pm)的非线性失真的量度。am-pm转换通常被定义为针对施加至放大器的输入的功率扫描中的1db增量(例如,在1db增益压缩点处)的输出相位的变化。理想的放大器在其相位响应与输入信号的功率电平之间将没有交互,并且因此具有平坦的转换曲线。

7、pae是用于评价放大器特别是功率放大器的效率的度量,该度量考虑了放大器的增益的影响。更具体地,放大器的pae是所产生的信号功率(输出功率与输入功率之间的差)与放大器的dc输入功率的比率。

8、特别地,在功率放大器中,am-am和am-pm变化与输出功率的关系对线性度和误差矢量幅度(evm)性能具有主要影响。在基于场效应晶体管(fet)的放大器中,am-pm和am-am行为受fet栅极-源极非线性电容(cgs)的影响。线性度和evm性能的劣化可以通过进一步远离1db压缩点(p1db)操作来降低,1db压缩点是放大器的增益从其恒定值降低1db的输出功率电平(一旦放大器到达其p1db点,放大器进入压缩并且变成非线性器件,从而产生失真、谐波以及互调产物)。然而,远低于p1db的操作显著降低了pae性能。

9、在一些集成电路(ic)fet制造技术中,只能在高电流密度下实现良好的am-am度量和am-pm度量,但是以高pae和热性能为代价。在其他ic fet制造技术中,可以在低电流密度下实现良好的功率和pae度量,但是am-am度量和am-pm度量在靠近p1db时显著地变化。

10、还可以使用数字预失真(dpd)来改进放大器的线性度和evm性能。然而,dpd需要反馈回路和复杂的电路,这两者都引起他们自身的设计和性能问题。

11、因此,需要在放大器中实现良好的am-am度量和am-pm度量,同时实现良好的功率、pae、线性度以及evm性能。本发明解决了这种需求。

技术实现思路

1、本发明包括用于在放大器中实现良好的am-am度量和am-pm度量同时实现良好的功率、pae、线性度以及evm性能的电路和方法。本发明的实施方式提供了新的均衡方法,该方法通过控制偏置条件(例如,偏置电压)与输出功率的关系以改变由放大器施加的am-am和am-pm分布来补偿放大器中的am-am和am-pm变化。该新颖方法适用于所有频率、技术以及单端放大器或差分放大器,特别是功率放大器(pa)。

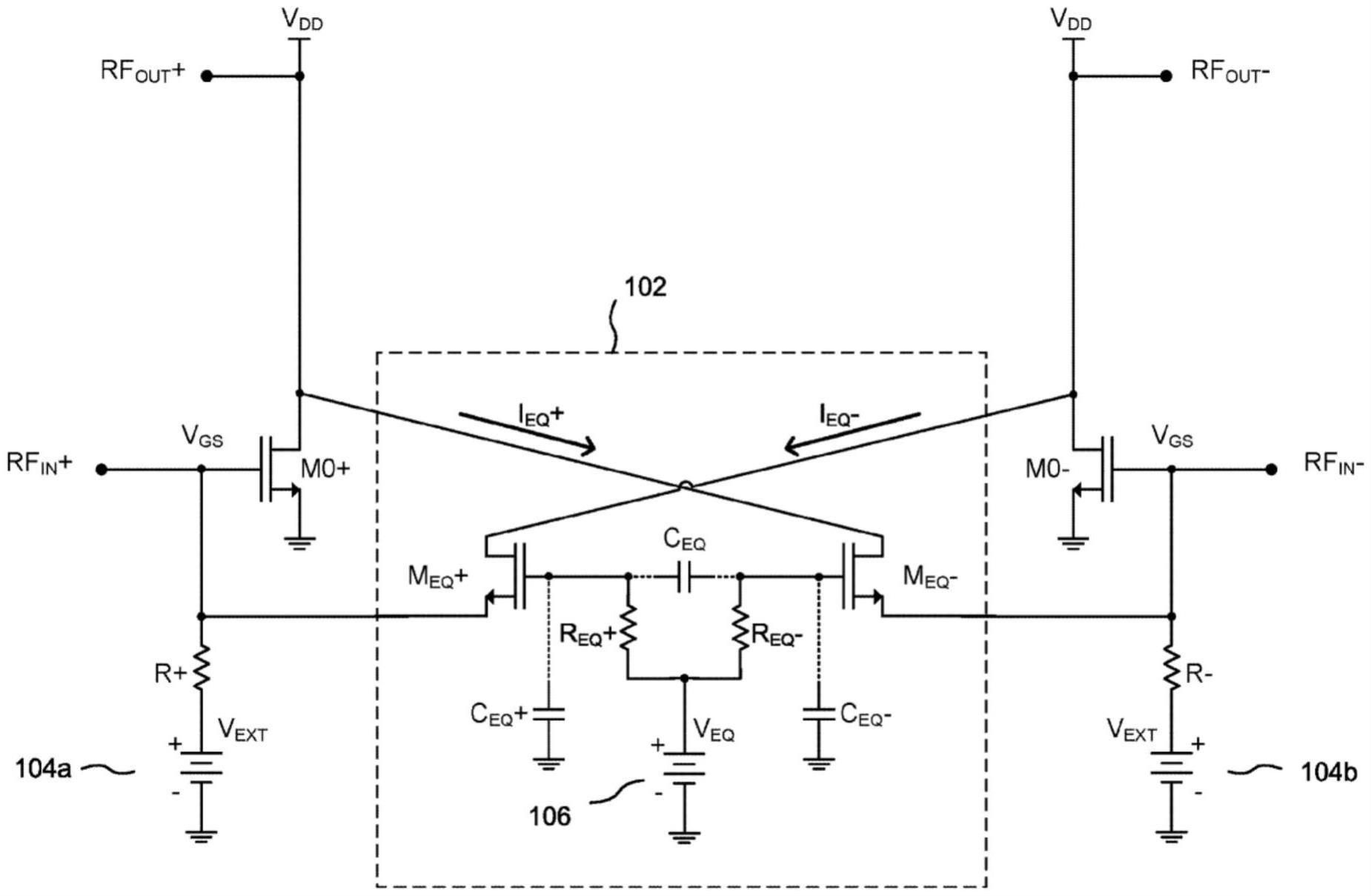

2、差分放大器实施方式包括:第一主场效应晶体管(fet),该第一主fet包括被配置成接收第一输入信号的栅极、提供第一放大输出信号的漏极以及耦接至电路接地的源极;第二主fet,该第二主fet包括被配置成接收第二输入信号的栅极、提供第二放大输出信号的漏极,以及耦接至电路接地的源极;以及均衡电路,该均衡电路耦接至第一fet和第二fet的相应的栅极和漏极并且被配置成生成均衡电压,该均衡电压与第二fet和第一fet的相应的漏极处存在的功率电平成比例地改变到相应的第一fet和第二fet的栅极的偏置电压。均衡电路的实施方式包括:第一均衡晶体管,该第一均衡晶体管包括耦接至第一主fet的漏极的漏极、耦接至第二主fet的栅极的源极以及被配置成耦接至第一偏置电压源的栅极;以及第二均衡晶体管,该第二均衡晶体管包括耦接至第二主fet的漏极的漏极、耦接至第一主fet的栅极的源极以及被配置成耦接至第一偏置电压源的栅极。

3、单端放大器实施方式包括:主fet,该主fet包括被配置成接收输入信号的栅极、提供放大输出信号的漏极、以及耦接至电路接地的源极;以及均衡电路,该均衡电路耦接至主fet的栅极和漏极并且被配置成生成均衡电压,该均衡电压与主fet的漏极处存在的功率电平成比例地改变到主fet的栅极的偏置电压。均衡电路的实施方式包括晶体管,该晶体管包括耦接至主fet的漏极的漏极、耦接至主fet的栅极的源极以及被配置成耦接至偏置电压源的栅极,均衡晶体管被配置成生成均衡电压。

4、本发明的实施方式还可以提供新的线性化方法,该方法通过对输入信号(例如射频信号)进行预处理来改变输入信号的am-pm分布,以补偿(本质上反转)由耦合放大器施加的am-pm分布,从而补偿放大器中的am-pm变化。

5、在包含线性化电路的实施方式中,该线性化电路包括:反射式混合耦合器,该反射式混合耦合器被配置成接收要被线性化的输入信号,该输入信号具有第一am-pm分布;第一反射式调制器件,该第一反射式调制器件耦接至反射式混合耦合器的直通端口;以及第二反射式调制器件,该第二反射式调制器件耦接至反射式混合耦合器的耦合端口,其中,第一反射式调制器件和第二反射式调制器件将输入信号的第一am-pm分布修改为具有第二am-pm分布的经修改的输出信号,该第二am-pm分布被成形为补偿由另一器件(例如,单端放大器或差分放大器)施加在经修改的输出信号上的第三am-pm分布。

6、本发明的一个或更多个实施方式的细节在以下附图和描述中进行阐述。本发明的其他特征、目的以及优点将从描述和附图以及从权利要求书中变得明显。

技术特征:

1.一种差分放大器,包括:

2.根据权利要求1所述的发明,其中,所述均衡电路与所述第二主fet的漏极处存在的功率电平成比例地改变到所述第一主fet的栅极的偏置电压,并且与所述第一主fet的漏极处存在的功率电平成比例地改变到所述第二主fet的栅极的偏置电压。

3.根据权利要求1所述的发明,其中,所述均衡电路包括至少两个交叉耦接的共栅极晶体管。

4.根据权利要求1所述的发明,其中,所述均衡电路包括:

5.根据权利要求4所述的发明,其中,所述第一均衡晶体管与所述第一fet的漏极处存在的功率电平成比例地改变到所述第二fet的栅极的偏置电压,并且所述第二均衡晶体管与所述第二fet的漏极处存在的功率电平成比例地改变到所述第一fet的栅极的偏置电压。

6.根据权利要求4所述的发明,其中,所述第一均衡晶体管的漏极通过串联耦接至所述第一主fet的漏极的至少一个中间fet耦接至所述第一主fet的漏极,并且其中,所述第二均衡晶体管的漏极通过串联耦接至所述第二主fet的漏极的至少一个中间fet耦接至所述第二主fet的漏极。

7.根据权利要求4所述的发明,其中,所述第一偏置电压源和所述第二偏置电压源向相应的所述第一均衡晶体管和所述第二均衡晶体管提供可调整的偏置电平。

8.根据权利要求4所述的发明,其中,所述第一均衡晶体管和所述第二均衡晶体管的尺寸被确定成小于或等于所述第一主fet和所述第二主fet的尺寸的约六分之一。

9.根据权利要求1所述的发明,其中,所述均衡电路包括:

10.根据权利要求1所述的发明,其中,所述均衡电路包括:

11.根据权利要求1所述的发明,还包括:串联耦接至所述第一主fet的漏极的一个或更多个fet的第一堆叠,以及串联耦接至所述第二主fet的漏极的一个或更多个fet的第二堆叠。

12.根据权利要求1所述的发明,还包括线性化电路,所述线性化电路包括:

13.一种放大器,包括:

14.根据权利要求13所述的发明,其中,所述均衡电路包括晶体管,所述晶体管包括耦接至所述主fet的漏极的漏极、耦接至所述主fet的栅极的源极以及被配置成耦接至偏置电压源的栅极,所述均衡晶体管被配置成生成所述均衡电压。

15.根据权利要求14所述的发明,其中,所述均衡晶体管通过串联耦接至所述主fet的漏极的至少一个中间fet耦接至所述主fet的漏极。

16.根据权利要求14所述的发明,其中,所述偏置电压源向所述均衡晶体管提供可调整的偏置电平。

17.根据权利要求14所述的发明,其中,所述均衡晶体管的尺寸被确定成小于或等于所述主fet的尺寸的约六分之一。

18.根据权利要求13所述的发明,其中,所述均衡电路包括耦接至所述主fet的漏极和所述主fet的栅极的n个串联耦接的晶体管的堆叠,其中,n≥1。

19.根据权利要求13所述的发明,其中,所述均衡电路包括n个串联耦接的晶体管的堆叠,所述n个串联耦接的晶体管的堆叠通过串联耦接至所述主fet的漏极的n-1个中间fet耦接在所述主fet的漏极与所述主fet的栅极之间,其中,n≥1。

20.根据权利要求13所述的发明,还包括串联耦接至所述主fet的漏极的一个或更多个fet的堆叠。

21.根据权利要求13所述的发明,还包括线性化电路,所述线性化电路包括:

22.一种使差分放大器均衡的方法,包括:

23.根据权利要求22所述的方法,其中,所述均衡电路与所述第二主fet的漏极处存在的功率电平成比例地改变到所述第一主fet的栅极的偏置电压,并且与所述第一主fet的漏极处存在的功率电平成比例地改变到所述第二主fet的栅极的偏置电压。

24.根据权利要求22所述的方法,其中,所述均衡电路包括至少两个交叉耦接的共栅极晶体管。

25.根据权利要求22所述的方法,其中,所述均衡电路包括:

26.根据权利要求25所述的方法,其中,所述第一均衡晶体管与所述第一fet的漏极处存在的功率电平成比例地改变到所述第二fet的栅极的偏置电压,并且所述第二均衡晶体管与所述第二fet的漏极处存在的功率电平成比例地改变到所述第一fet的栅极的偏置电压。

27.根据权利要求25所述的方法,其中,所述第一均衡晶体管的漏极通过串联耦接至所述第一主fet的漏极的至少一个中间fet耦接至所述第一主fet的漏极,并且其中,所述第二均衡晶体管的漏极通过串联耦接至所述第二主fet的漏极的至少一个中间fet耦接至所述第二主fet的漏极。

28.根据权利要求25所述的方法,其中,所述第一偏置电压源和所述第二偏置电压源向相应的所述第一均衡晶体管和所述第二均衡晶体管提供可调整的偏置电平。

29.根据权利要求25所述的方法,其中,所述第一均衡晶体管和所述第二均衡晶体管的尺寸被确定成小于或等于所述第一主fet和所述第二主fet的尺寸的约六分之一。

30.根据权利要求22所述的方法,其中,所述均衡电路包括:

31.根据权利要求22所述的方法,其中,所述均衡电路包括:

32.根据权利要求22所述的方法,还包括:将串联耦接至所述第一主fet的漏极的一个或更多个fet的第一堆叠进行耦接,以及将串联耦接至所述第二主fet的漏极的一个或更多个fet的第二堆叠进行耦接。

33.根据权利要求22所述的方法,还包括从线性化电路的输出信号得出到所述差分放大器的相应输入信号,所述线性化电路包括:

34.一种使放大器均衡的方法,包括:

35.根据权利要求34所述的方法,其中,所述均衡电路包括晶体管,所述晶体管包括耦接至所述主fet的漏极的漏极、耦接至所述主fet的栅极的源极以及被配置成耦接至偏置电压源的栅极,所述均衡晶体管被配置成改变到所述主fet的栅极的偏置电压。

36.根据权利要求35所述的方法,其中,所述均衡晶体管通过串联耦接至所述主fet的漏极的至少一个中间fet耦接至所述主fet的漏极。

37.根据权利要求35所述的方法,其中,所述偏置电压源向所述均衡晶体管提供可调整的偏置电平。

38.根据权利要求35所述的方法,其中,所述均衡晶体管的尺寸被确定成小于或等于所述主fet的尺寸的约六分之一。

39.根据权利要求34所述的方法,其中,所述均衡电路包括耦接至所述主fet的漏极和所述主fet的栅极的n个串联耦接的晶体管的堆叠,其中,n≥1。

40.根据权利要求34所述的方法,其中,所述均衡电路包括n个串联耦接的晶体管的堆叠,所述n个串联耦接的晶体管的堆叠通过串联耦接至所述主fet的漏极的n-1个中间fet耦接在所述主fet的漏极与所述主fet的栅极之间,其中,n≥1。

41.根据权利要求34所述的方法,还包括将串联耦接至所述主fet的漏极的一个或更多个fet的堆叠进行耦接。

42.根据权利要求34所述的方法,还包括从线性化电路的输出信号得出到所述放大器的输入信号,所述线性化电路包括:

技术总结

用于在放大器中实现良好的AM‑AM度量和AM‑PM度量同时实现良好的功率、PAE、线性度以及EVM性能的电路和方法。差分放大器实施方式包括生成均衡电压的交叉耦接的共栅极晶体管(M<subgt;EQ</subgt;+,M<subgt;EQ.</subgt;),该均衡电压与主FET(M0+,M0‑)的相应的漏极处存在的功率电平成比例地改变相应的主FET(M0+,M0‑)的栅极偏置电压。单端放大器实施方式包括均衡电路,该均衡电路与主FET漏极处存在的功率电平成比例地改变到主FET的栅极的偏置电压。实施方式还可以包括线性化电路,该线性化电路改变输入信号的AM‑PM分布以补偿由耦合放大器施加的AM‑PM分布。

技术研发人员:达乌德·萨拉马

受保护的技术使用者:派赛公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!