具有分段延迟电路的延迟锁定环的制作方法

本公开的各方面总体上涉及延迟电路,并且更具体地涉及分段延迟电路。

背景技术:

1、延迟电路可以被用于将信号延迟可调节的(即,可调谐的)延迟。可调节的延迟可以被用于例如通过将第一信号延迟对应量来调节第一信号相对于第二信号的定时。当被延迟的信号是周期信号时,延迟可以根据信号的相位变化来描述。

技术实现思路

1、以下呈现了一个或多个实现的简化概述,以提供对这样的实现的基本理解。本概述不是所有预期实现的广泛概述,并且既不旨在确定所有实现的关键或基本元素,也不旨在界定任何或所有实现的范围。其唯一目的是以简化的形式呈现一个或多个实现的一些概念,作为被稍后呈现的更详细的描述的前奏。

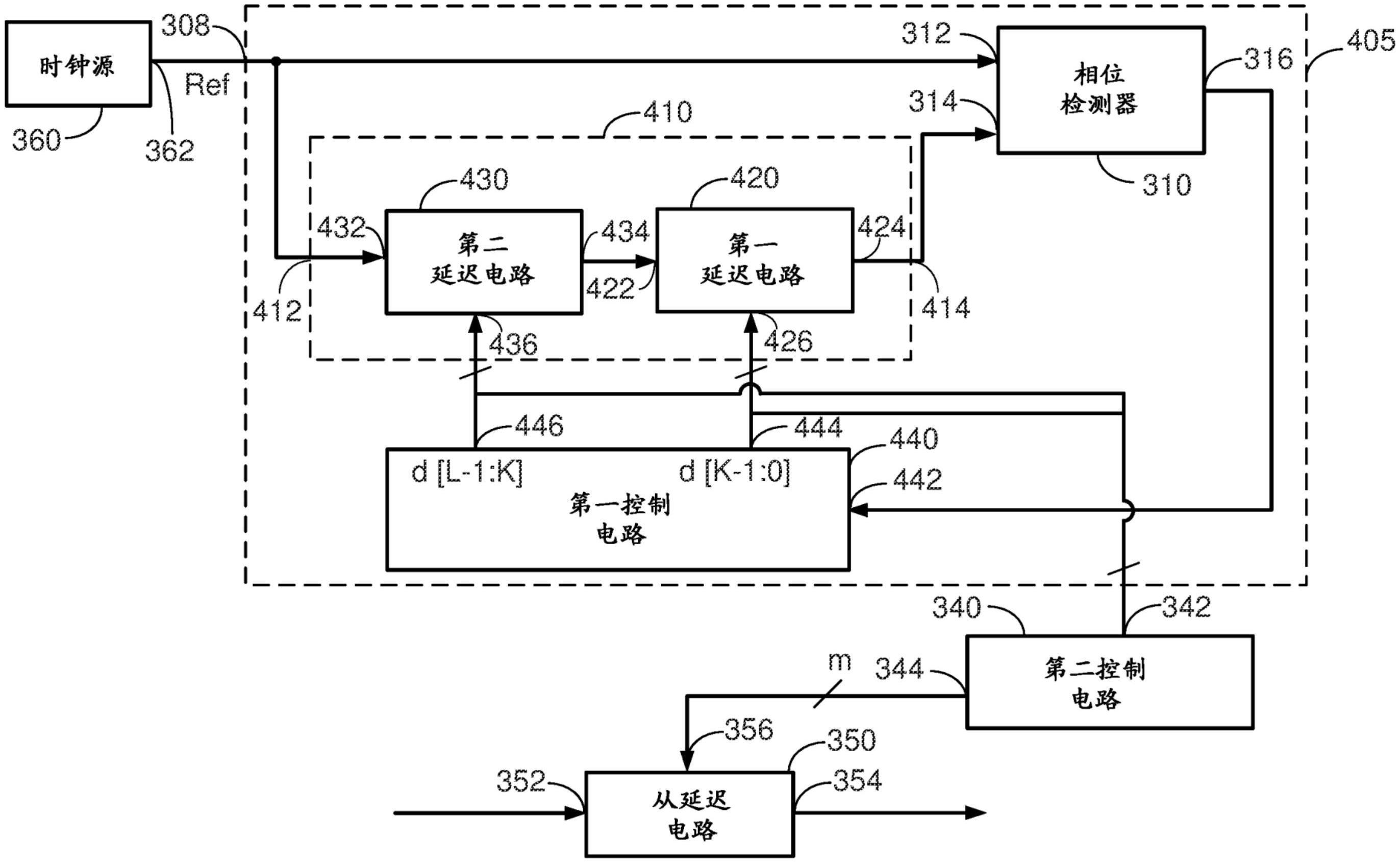

2、第一方面涉及一种系统。该系统包括延迟锁定环(dll),该dll包括具有第一输入端、第二输入端和输出端的相位检测器,其中相位检测器的第一输入端耦合到dll的输入端。该dll还包括第一延迟电路和第二延迟电路,其中第一延迟电路和第二延迟电路串联耦合在dll的输入端与相位检测器的第二输入端之间。该dll还包括具有输入端、第一输出端和第二输出端的第一控制电路,其中第一控制电路的输入端耦合到相位检测器的输出端,第一控制电路的第一输出端耦合到第一延迟电路的控制输入端,并且第一控制电路的第二输出端耦合到第二延迟电路的控制输入端。该系统还包括具有输入端和输出端的第二控制电路,其中第二控制电路的输入端耦合到第一控制电路。该系统还包括从延迟电路,该从延迟电路具有耦合到第二控制电路的输出端的控制输入端。

3、第二方面涉及一种操作系统的方法。该系统包括延迟锁定环(dll)和从延迟电路,该dll包括相位检测器、第一延迟电路和第二延迟电路,其中相位检测器的第一输入端耦合到dll的输入端,并且第一延迟电路和第二延迟电路串联耦合在dll的输入端与相位检测器的第二输入端之间。该方法包括:从相位检测器的输出端接收相位误差信号,基于相位误差信号来调节第一延迟控制信号,将第一延迟控制信号的第一部分输出到第一延迟电路的控制输入端,将第一延迟控制信号的第二部分输出到第二延迟电路的控制输入端,基于第一延迟控制信号来生成第二延迟控制信号,以及将第二延迟控制信号输出到从延迟电路的控制输入端。

技术特征:

1.一种系统,包括:

2.根据权利要求1所述的系统,其中所述第一控制电路包括:

3.根据权利要求1所述的系统,还包括:

4.根据权利要求3所述的系统,还包括时钟源,所述时钟源耦合到所述从延迟电路的输入端。

5.根据权利要求1所述的系统,其中所述从延迟电路包括:

6.根据权利要求1所述的系统,其中所述第一控制电路被配置为:

7.根据权利要求6所述的系统,其中:

8.根据权利要求6所述的系统,其中:

9.根据权利要求6所述的系统,其中所述第二控制电路被配置为:

10.根据权利要求9所述的系统,其中所述第三延迟控制信号包括针对所述从延迟电路的延迟与参考时钟信号的周期的比。

11.根据权利要求6所述的系统,其中所述第一延迟电路包括多个延迟器件,并且所述第一延迟电路被配置为基于所述第一延迟控制信号的所述第一部分,选择性地将所述多个延迟器件中的一定数目的延迟器件放置在所述第一延迟电路的延迟路径中。

12.根据权利要求11所述的系统,其中所述第二延迟电路包括:

13.根据权利要求1所述的系统,其中第二控制电路包括:

14.根据权利要求13所述的系统,其中所述第三延迟控制信号包括针对所述从延迟电路的延迟与参考时钟信号的周期的比。

15.根据权利要求1所述的系统,其中所述dll还包括:

16.根据权利要求15所述的系统,其中所述从延迟电路包括:

17.根据权利要求16所述的系统,其中所述第一控制电路被配置为:

18.根据权利要求16所述的系统,其中所述第二控制电路被配置为:

19.根据权利要求18所述的系统,其中所述第三延迟控制信号包括针对所述从延迟电路的延迟与参考时钟信号的周期的比。

20.根据权利要求16所述的系统,其中所述第四延迟电路包括多个延迟器件,并且所述第四延迟电路被配置为基于所述第二延迟控制信号的所述第二部分,选择性地将所述多个延迟器件中的一定数目的延迟器件放置在所述第四延迟电路的延迟路径中。

21.根据权利要求20所述的系统,其中所述第三延迟器件包括延迟插值器。

22.一种操作包括延迟锁定环(dll)和从延迟电路的系统的方法,所述dll包括相位检测器、第一延迟电路以及第二延迟电路,其中所述相位检测器的第一输入端耦合到所述dll的输入端,并且所述第一延迟电路和所述第二延迟电路串联耦合在所述dll的所述输入端与所述相位检测器的第二输入端之间,所述方法包括:

23.根据权利要求22所述的方法,其中:

24.根据权利要求23所述的方法,其中:

25.根据权利要求22所述的方法,其中:

26.根据权利要求25所述的方法,其中:

27.根据权利要求22所述的方法,其中基于所述第一延迟控制信号来生成所述第二延迟控制信号包括:

28.根据权利要求27所述的方法,其中所述第三延迟控制信号包括针对所述从延迟电路的延迟与参考时钟信号的周期的比。

29.根据权利要求22所述的方法,其中所述从延迟电路包括第三延迟电路以及与所述第三延迟电路串联耦合的第四延迟电路,并且其中输出所述第二延迟控制信号包括:

技术总结

一种系统包括延迟锁定环(DLL),该DLL包括具有耦合到DLL的输入端的第一输入端的相位检测器、以及串联耦合在DLL的输入端与相位检测器的第二输入端之间的第一延迟电路和第二延迟电路。DLL还包括第一控制电路,其中第一控制电路的输入端耦合到相位检测器的输出端,第一控制电路的第一输出端耦合到第一延迟电路的控制输入端,并且第一控制电路的第二输出端耦合到第二延迟电路的控制输入端。该系统还包括具有耦合到第一控制电路的输入端的第二控制电路、以及具有耦合到第二控制电路的输出端的控制输入端的从延迟电路。

技术研发人员:J·M·辛里奇斯

受保护的技术使用者:高通股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!