一种电阻矫正电路、方法及芯片与流程

本申请涉及芯片电阻矫正,具体而言,涉及一种电阻矫正电路、方法及芯片。

背景技术:

1、在芯片生产过程中,由于工艺的偏差,电阻会随机发生变化。而在许多很多模拟电路设计场景中,例如adc(analog to digital converter,模拟数字转换器),dac(数模转换器),serdes(串行器与解串器),等模拟电路中,电阻的精度影响模拟电路的性能。同时,在集成电路的设计中,如果设计不当,会对整个电路有很大的影响。

2、因此,在芯片生产过程中,需要对芯片内部的电阻进行矫正。目前,传统的电阻矫正电路需要在芯片外外接电阻,来矫正电阻阻值由于工艺引起的变化。然而,通过外接电阻方式实现芯片内部电阻矫正,会导致矫正电路的整体成本相对较高。

3、综上,现有技术中存在电阻矫正电路的成本较高的问题。

技术实现思路

1、本申请的目的在于提供一种电阻矫正电路、方法及芯片,以解决现有技术中存在的电阻矫正电路的成本较高的问题。

2、为了实现上述目的,本申请实施例采用的技术方案如下:

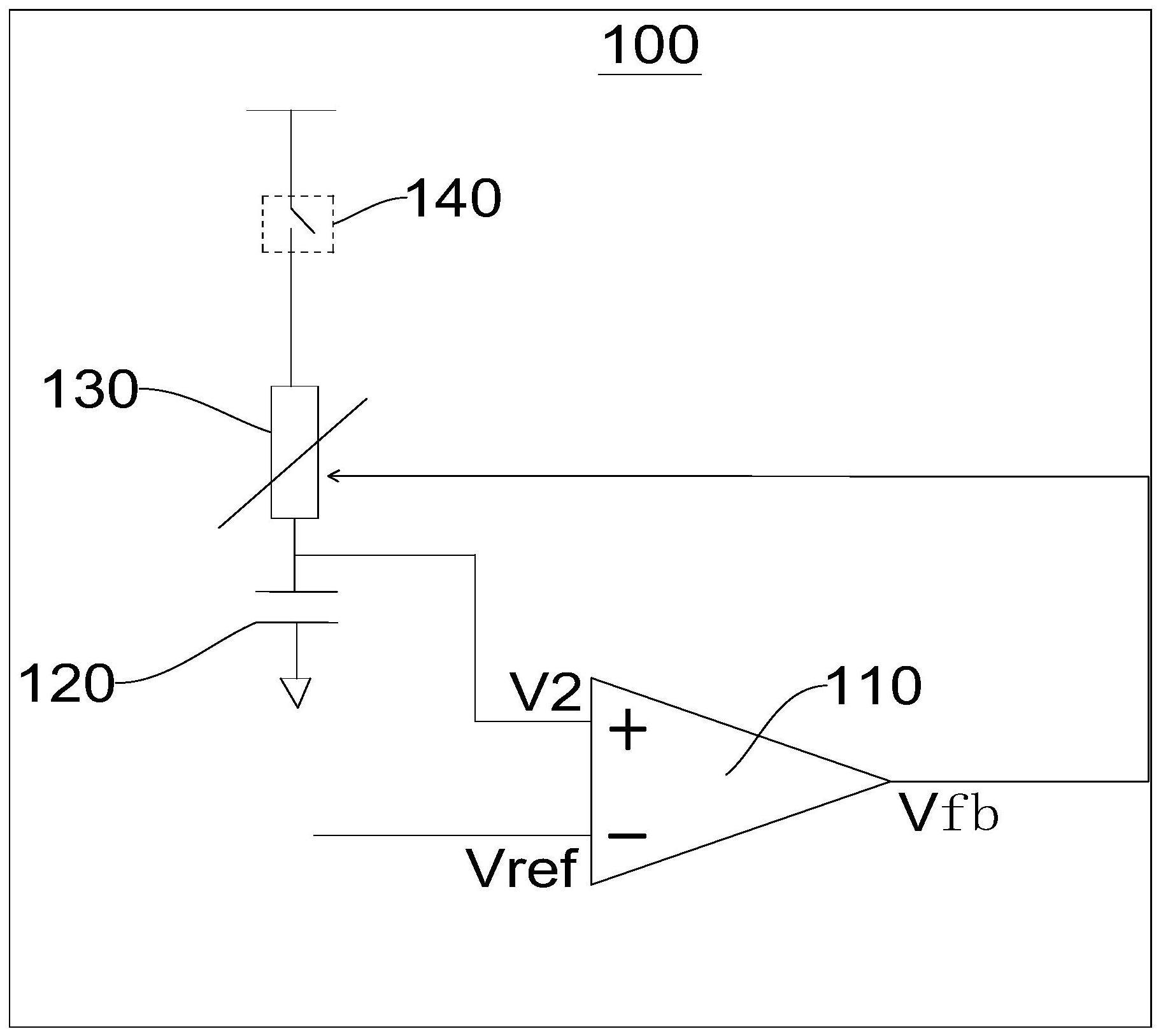

3、第一方面,本申请实施例提供了一种电阻矫正电路,所述电阻矫正电路包括比较器、待矫正电阻以及电容,所述比较器、待矫正电阻以及电容均位于芯片内,所述待矫正电阻与所述电容串联后的一端连接电源,另一端接地,所述比较器的第一输入端连接于所述待矫正电阻与所述电容之间,所述比较器的第二输入端用于输入参考电压,所述比较器的输出端与所述待矫正电阻电连接;其中,

4、所述待矫正电阻用于依据所述比较器的输出端电压进行阻值矫正,以使所述比较器的第一输入端的充电电压与第二输入端的电压相等。

5、可选地,所述第一输入端的充电电压满足于公式:

6、v2=vdd*[1–exp(-t/rc)];

7、其中,v2表示第一输入端的充电电压,vdd表示电源电压,t表示电容充放电的开关时间,c表示电容容值,r表示待矫正电阻的阻值。

8、可选地,所述电阻矫正电路还包括电流开关,所述电流开关分别与所述电源、所述待矫正电阻电连接,所述电流开关用于调节流过所述待矫正电阻的电流。

9、可选地,所述电流开关包括开关管,所述开关管的控制端用于接收驱动信号,所述开关管的第一端、第二端分别与所述电源、所述待矫正电阻电连接,所述开关管用于依据所述驱动信号的占空比调节流过所述待矫正电阻的电流。

10、可选地,所述待矫正电阻包括mos管与芯片电阻,所述mos管与所述芯片电阻串联后的一端连接电源,另一端分别与所述电容、所述比较器的第一输入端电连接,所述mos管的控制端还与所述比较器的输出端电连接。

11、可选地,当所述mos管为p型mos管时,所述mos管与所述芯片电阻串联后的另一端与所述电容、所述比较器的同相输入端电连接,所述比较器的反相输入端用于输入参考电压;

12、当所述mos管为n型mos管时,所述mos管与所述芯片电阻串联后的另一端与所述电容、所述比较器的反相输入端电连接,所述比较器的同相输入端用于输入参考电压。

13、第二方面,本申请实施例还提供了一种电阻矫正方法,应用于上述的电阻矫正电路,所述方法包括:

14、向所述比较器的第二输入端提供参考电压;

15、所述比较器依据第一输入端的充电电压与第二输入端的电压大小输出的驱动电压,以通过所述驱动电压调节所述待矫正电阻的阻值,直至所述第一输入端的充电电压与第二输入端的电压相等。

16、可选地,所述第一输入端的充电电压满足于公式:

17、v2=vdd*[1–exp(-t/rc)];

18、其中,v2表示第一输入端的充电电压,vdd表示电源电压,t表示电容充放电的开关时间,c表示电容容值,r表示待矫正电阻的阻值。

19、可选地,所述电阻矫正电路还包括电流开关,所述电流开关分别与所述电源、所述待矫正电阻电连接;所述方法还包括:

20、依据目标电流调节电流开关的导通频率,以调节流过所述待矫正电阻的电流。

21、第三方面,本申请实施例还提供了一种芯片,包括上述的电阻矫正电路。

22、相对于现有技术,本申请具有以下有益效果:

23、本申请提供了一种电阻矫正电路、方法及芯片,该电阻矫正电路包括比较器、待矫正电阻以及电容,比较器、待矫正电阻以及电容均位于芯片内,待矫正电阻与电容串联后的一端连接电源,另一端接地,比较器的第一输入端连接于待矫正电阻与电容之间,比较器的第二输入端用于输入参考电压,比较器的输出端与待矫正电阻电连接;其中,待矫正电阻用于依据比较器的输出端电压进行阻值矫正,以使比较器的第一输入端的充电电压与第二输入端的电压相等。由于本申请中比较器、待矫正电阻以及电容均位于芯片内,因此无须设置外接电阻与芯片管脚,而是通过芯片内部的rc电路在充电时的电压调节实现待矫正电阻的自矫正,进而节省了成本。

24、为使本申请的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

技术特征:

1.一种电阻矫正电路,其特征在于,所述电阻矫正电路包括比较器、待矫正电阻以及电容,所述比较器、待矫正电阻以及电容均位于芯片内,所述待矫正电阻与所述电容串联后的一端连接电源,另一端接地,所述比较器的第一输入端连接于所述待矫正电阻与所述电容之间,所述比较器的第二输入端用于输入参考电压,所述比较器的输出端与所述待矫正电阻电连接;其中,

2.如权利要求1所述的电阻矫正电路,其特征在于,所述第一输入端的充电电压满足于公式:

3.如权利要求1所述的电阻矫正电路,其特征在于,所述电阻矫正电路还包括电流开关,所述电流开关分别与所述电源、所述待矫正电阻电连接,所述电流开关用于调节流过所述待矫正电阻的电流。

4.如权利要求3所述的电阻矫正电路,其特征在于,所述电流开关包括开关管,所述开关管的控制端用于接收驱动信号,所述开关管的第一端、第二端分别与所述电源、所述待矫正电阻电连接,所述开关管用于依据所述驱动信号的占空比调节流过所述待矫正电阻的电流。

5.如权利要求1所述的电阻矫正电路,其特征在于,所述待矫正电阻包括mos管与芯片电阻,所述mos管与所述芯片电阻串联后的一端连接电源,另一端分别与所述电容、所述比较器的第一输入端电连接,所述mos管的控制端还与所述比较器的输出端电连接。

6.如权利要求5所述的电阻矫正电路,其特征在于,当所述mos管为p型mos管时,所述mos管与所述芯片电阻串联后的另一端与所述电容、所述比较器的同相输入端电连接,所述比较器的反相输入端用于输入参考电压;

7.一种电阻矫正方法,其特征在于,应用于如权利要求1至6任一项所述的电阻矫正电路,所述方法包括:

8.如权利要求7所述的电阻矫正方法,其特征在于,所述第一输入端的充电电压满足于公式:

9.如权利要求7所述的电阻矫正方法,其特征在于,所述电阻矫正电路还包括电流开关,所述电流开关分别与所述电源、所述待矫正电阻电连接;所述方法还包括:

10.一种芯片,其特征在于,包括如权利要求1至6任一项所述的电阻矫正电路。

技术总结

本申请提供了一种电阻矫正电路、方法及芯片,涉及芯片电阻矫正技术领域。该电阻矫正电路包括比较器、待矫正电阻以及电容,比较器、待矫正电阻以及电容均位于芯片内,待矫正电阻与电容串联后的一端连接电源,另一端接地,比较器的第一输入端连接于待矫正电阻与电容之间,比较器的第二输入端用于输入参考电压,比较器的输出端与待矫正电阻电连接;其中,待矫正电阻用于依据比较器的输出端电压进行阻值矫正,以使比较器的第一输入端的充电电压与第二输入端的电压相等。本申请提供的电阻矫正电路、方法及芯片具有节省了成本的优点。

技术研发人员:林云

受保护的技术使用者:中茵微电子(南京)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!