反相器及其控制方法、存储器、电子设备与流程

本申请涉及电子设备,具体而言,本申请涉及一种反相器及其控制方法、存储器、电子设备。

背景技术:

1、cmos(complementary metal oxide semiconductor,互补金属氧化物半导体)反相器由一个p沟道增强型mos(mosfet的缩写,metal-oxide-semiconductor field-effecttransistor,金属-氧化物半导体场效应晶体管)管(即pmos)和一个n沟道增强型mos管(即nmos)构成,两个晶体管的栅极相连,接入电路的输入端,pmos的源极接电源端,nmos的源极接地,pmos与nmos的漏极连接并且接入输出端。

技术实现思路

1、本申请提出一种反相器及其控制方法、存储器、电子设备。

2、第一方面,本申请实施例提供了一种反相器,包括第一晶体管和第二晶体管;第一晶体管和第二晶体管均为n型晶体管或均为p型晶体管;

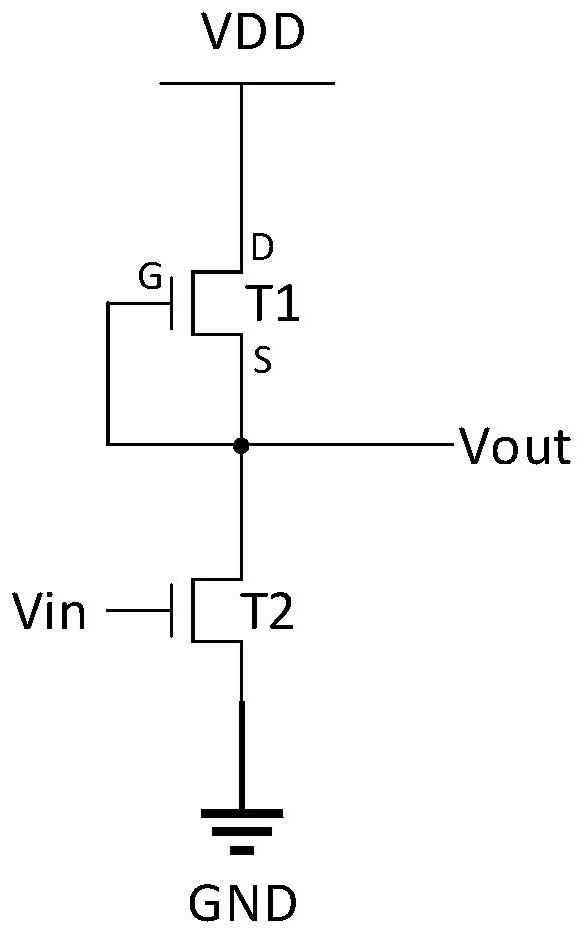

3、第一晶体管和第二晶体管均为n型晶体管,第一晶体管的第一极与第一电压端连接;第一晶体管的第二极分别与第一晶体管的控制栅极、第二晶体管的第一极和输出端连接;第二晶体管的第二极与第二电压端连接;第二晶体管的控制栅极与输入端连接;第一晶体管的阈值电压小于0,第二晶体管的阈值电压大于0;或,

4、第一晶体管和第二晶体管均为p型晶体管,第一晶体管的第一极与第一电压端连接;第一晶体管的控制栅极与输入端连接;第一晶体管的第二极与第二晶体管的第一极连接;第二晶体管的第一极分别与第二晶体管的控制栅极和输出端连接;第二晶体管的第二极与第二电压端连接;第一晶体管的阈值电压小于0,第二晶体管的阈值电压大于0;

5、输入端的信号的逻辑电平与输出端的信号的逻辑电平相反。

6、在一种可能的实现方式中,第一晶体管还包括背栅极,第一晶体管的背栅极与第三电压端连接;

7、和/或,第二晶体管还包括背栅极,第二晶体管的背栅极与第四电压端连接。

8、在一种可能的实现方式中,第一晶体管和第二晶体管均为n型晶体管,第一晶体管的半导体层材料包括氧化物,第二晶体管的半导体层材料包括氧化物或硅。

9、在一种可能的实现方式中,第一晶体管的半导体层材料包括铟。

10、在一种可能的实现方式中,第一晶体管的沟道的宽和第二晶体管的沟道的宽相等,第一晶体管的沟道的长和第二晶体管的沟道的长相等。。

11、在一种可能的实现方式中,第一晶体管还包括背栅极,第一晶体管还包括半导体层;沿第一方向,控制栅极与背栅极分别位于半导体层的两侧,并分别与半导体层绝缘设置;沿第二方向,第一极和第二极分别位于半导体层的两侧,并分别与半导体层连接;

12、和/或,第二晶体管还包括背栅极,第二晶体管还包括半导体层;沿第一方向,控制栅极与背栅极分别位于半导体层的两侧,并分别与半导体层绝缘设置;沿第二方向,第一极和第二极分别位于半导体层的两侧,并分别与半导体层连接;第一方向与第二方向交叉。

13、在一种可能的实现方式中,控制栅极在衬底上的正投影,分别与第一极在衬底上的正投影和第二极在衬底上的正投影无交叠,且与半导体层在衬底上的正投影交叠,且位于背栅极在衬底上的正投影内。

14、在一种可能的实现方式中,第一晶体管还包括背栅极,第一晶体管还包括第一绝缘层和第二绝缘层;第一绝缘层位于控制栅极和半导体层之间,且第一绝缘层在衬底上的正投影与控制栅极在衬底上正投影交叠;第二绝缘层位于半导体层和背栅极之间,且第二绝缘层在衬底上的正投影与背栅极在衬底上正投影交叠;

15、和/或,第二晶体管还包括背栅极,第二晶体管还包括第一绝缘层和第二绝缘层;第一绝缘层位于控制栅极和半导体层之间,且第一绝缘层在衬底上的正投影与控制栅极在衬底上正投影交叠;第二绝缘层位于半导体层和背栅极之间,且第二绝缘层在衬底上的正投影与背栅极在衬底上正投影交叠。

16、第二方面,本申请实施例提供了一种存储器,包括上述的任一实施例所述的反相器。

17、第三方面,本申请实施例提供了一种电子设备,包括上述的任一实施例所述的反相器。

18、第四方面,本申请实施例提供了一种反相器的控制方法,其中,反相器的第一晶体管和第二晶体管均为n型晶体管,控制方法包括:向第一晶体管的背栅极施加第一电压,以控制第一晶体管的阈值电压小于0,使得第一晶体管处于开启状态,第二晶体管基于接收的输入端的信号导通或关断,以使得输入端的信号的逻辑电平与输出端的信号的逻辑电平相反;

19、或,反相器的第一晶体管和第二晶体管均为p型晶体管,控制方法包括:向第二晶体管的背栅极施加第二电压,以控制第二晶体管的阈值电压大于0,使得第二晶体管处于开启状态,第一晶体管基于接收的输入端的信号导通或关断,以使得输入端的信号的逻辑电平与输出端的信号的逻辑电平相反。

20、本申请实施例提供的技术方案,至少具有如下有益效果:

21、本申请实施例提供的反相器包括第一晶体管和第二晶体管;第一晶体管和第二晶体管均为n型晶体管或均为p型晶体管。随着输入端信号的变化,反相器中第一晶体管电阻阻值的变化或第二晶体管电阻阻值的变化对输出端的电位形成了一个正向的反馈,并且由于反相器中采用同一种载流子的n型晶体管或p型晶体管,可实现第一晶体管t1和第二晶体管t2的面积比例为1:1,相比cmos反相器与如图1所示的已知两个nmos反相器,更省面积。而且,由于反相器中第一晶体管电阻阻值的变化或第二晶体管电阻阻值的变化对输出端的电位形成了一个正向的反馈,使得输出端输出的信号较好,从而使得反相器具有优异的放大性能,大摆动范围,可借鉴在其他逻辑门及电路上。本申请实施例提供的反相器可应用于3d-dram(dynamic random access memory,动态随机存取存储器)高层bl/wl(位线/字线)选通开关,还可应用于低功耗类产品,如穿戴消费类电子产品等。

22、本申请附加的方面和优点将在下面的描述中部分给出,这些将从下面的描述中变得明显,或通过本申请的实践了解到。

技术特征:

1.一种反相器,其特征在于,包括第一晶体管和第二晶体管;所述第一晶体管和所述第二晶体管均为n型晶体管或均为p型晶体管;

2.根据权利要求1所述的反相器,其特征在于,所述第一晶体管还包括背栅极,所述第一晶体管的背栅极与第三电压端连接;

3.根据权利要求2所述的反相器,其特征在于,

4.根据权利要求3所述的反相器,其特征在于,

5.根据权利要求1至4任一所述的反相器,其特征在于,

6.根据权利要求2所述的反相器,其特征在于,

7.根据权利要求6所述的反相器,其特征在于,

8.根据权利要求6所述的反相器,其特征在于,

9.一种存储器,其特征在于,包括如权利要求1至8任一所述的反相器。

10.一种电子设备,其特征在于,包括如权利要求1至8任一所述的反相器。

11.一种如权利要求1至8任一所述的反相器的控制方法,其特征在于,

技术总结

本申请实施例提供了一种反相器及其控制方法、存储器、电子设备。该反相器包括第一晶体管和第二晶体管;第一晶体管和第二晶体管均为N型晶体管或均为P型晶体管;当第一晶体管和第二晶体管均为N型晶体管时,第一晶体管的第一极与第一电压端连接;第一晶体管的第二极分别与第一晶体管的控制栅极、第二晶体管的第一极和输出端连接;第二晶体管的第二极与第二电压端连接;第二晶体管的控制栅极与输入端连接;第一晶体管的阈值电压小于0,第二晶体管的阈值电压大于0;本申请实施例提供的反相器,随着输入端信号的变化,是一个正向反馈的过程,不仅能够节省面积,而且还能够使得输出端输出的信号较好,从而使得反相器具有优异的放大性能。

技术研发人员:梁静,余泳,杨楠,戴瑾,康卜文

受保护的技术使用者:北京超弦存储器研究院

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!