电流或电容隔离器的成形金属边缘的制作方法

所公开的技术一般涉及用于集成电路器件的导线,并且更具体地涉及用于集成变压器和隔离器中的导线。

背景技术:

1、导线和金属化结构构成许多电子器件和部件的组成部分。一些导线用作电互连各种有源器件(例如晶体管)的布线,而一些其他金属化结构本身用作无源或有源器件,例如电感器、电阻器或变压器。一些导线可以形成为集成电路(ic)器件的整体部分。例如,导线可用于形成集成电感器和变压器,用于各种应用,例如电隔离、电压或电流转换和其他应用。在某些情况下,集成电路可以是在基板上单片制造的单片电路。单片制造允许在芯片或基板的小体积或小面积中集成通过导线电互连的大量电子器件。

技术实现思路

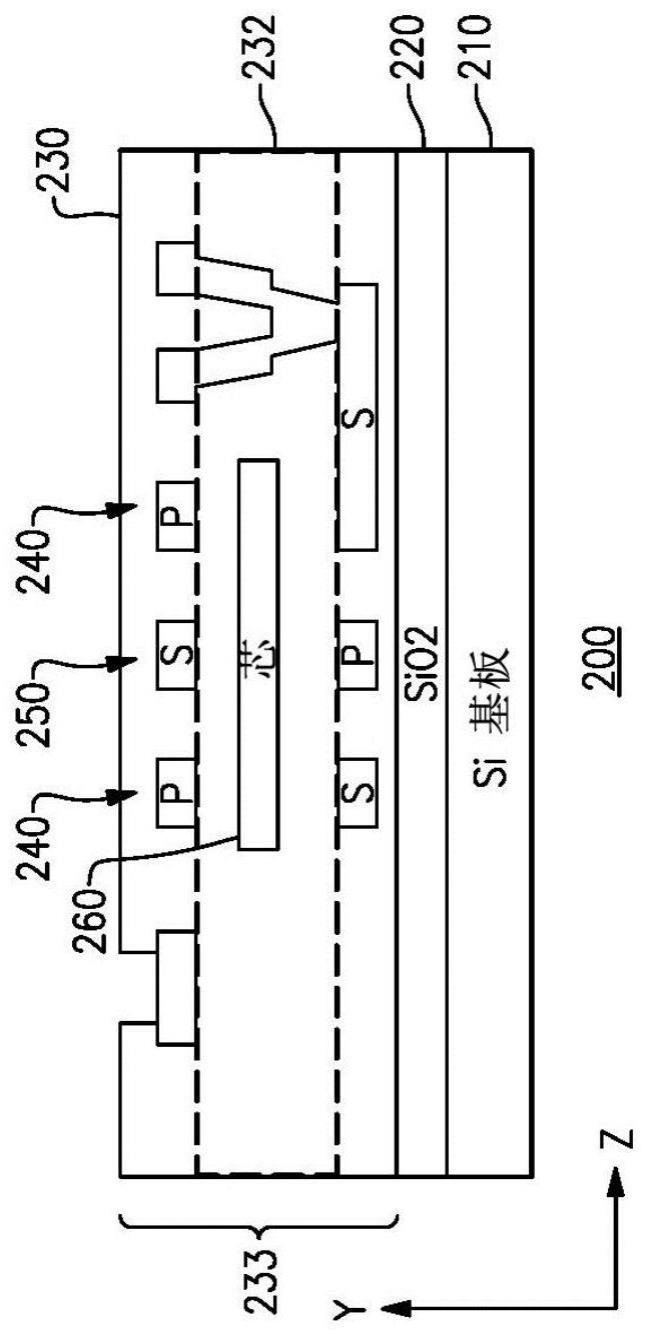

1、在本文描述的一个方面中,集成电路器件包括:具有主表面的基板,设置在所述基板上的芯层;和光刻图案化的初级线圈,其中初级线圈包括围绕平行于所述主表面的绕组轴缠绕的一个或多个绕组。每个绕组包括布置在所述芯层上方的顶部导线,所述顶部导线沿着垂直于所述主表面的垂直轴具有第一厚度,其中所述顶部导线在平行于所述绕组轴且垂直于所述主表面的平面中的横截面包括所述顶部导线的侧表面的圆形凸起部分,其中圆形凸起部分具有大于1微米的曲率半径。每个绕组还包括布置在所述芯层下方的底部导线,所述底部导线沿着所述垂直轴具有第二厚度,其中所述底部导线在所述平面中的横截面包括所述底部导线的侧表面的圆形凸起部分,所述圆形凸起部分具有大于1微米的曲率半径。每个绕组还包括第一导电通孔,沿着所述垂直轴延伸,电连接所述顶部导线和底部导线,和第二导电通孔,沿着所述垂直轴延伸,将所述顶部和底部导线中的一个而不是另一个电连接到所述初级线圈的另一绕组的导线。

2、在本文描述的另一个方面中,集成电路器件包括:具有主表面的基板、设置在所述基板上的芯层和光刻图案化的初级线圈,其中初级线圈包括围绕平行于所述主表面的绕组轴缠绕的一个或多个绕组。每个绕组包括:布置在所述芯层上方的顶部导线,其中所述顶部导线的负倾斜侧表面和顶表面之间的锐角小于75度,布置在所述芯层下方的底部导线,其中所述底部导线的正倾斜侧表面和底表面之间的锐角小于75度。每个绕组包括第一导电通孔,沿着垂直于所述主表面的垂直轴延伸并电连接所述顶部导线和所述底部导线,和第二导电通孔,沿着所述垂直轴延伸并且将所述顶部或底部导线电连接到所述初级线圈的另一绕组的导线。

3、在本文描述的另一个方面中,集成电路器件包括具有主表面的基板、设置在所述基板上的芯层和光刻图案化的初级线圈,所述初级线圈包括围绕平行于所述主表面的绕组轴缠绕的一个或多个绕组。每个绕组包括:布置在所述芯层上方的顶部导线,其中所述顶部导线的侧表面包括具有一个或多个侧表面部分的阶梯部分,和其中所述侧表面部分的单个侧表面部分包括基本上垂直于所述主表面的平坦表面。每个绕组还包括:布置在所述芯层下方的底部导线,第一导电通孔,沿着垂直于所述主表面的垂直轴延伸并电连接所述顶部导线和所述底部导线;和第二导电通孔,沿着所述垂直轴延伸,并将所述顶部和底部导线中的一个而不是另一个电连接到所述初级线圈的另一绕组的导线。

4、在本文描述的另一个方面中,集成电路器件包括半导体基板,所述半导体基板具有主表面、初级线圈和次级线圈,每个初级线圈和次级线圈绕平行于所述主表面的绕组轴缠绕,其中初级线圈和次级线圈的绕组彼此交错,使得初级线圈的绕组沿着所述绕组轴与次级线圈的绕组交替。初级线圈和次级线圈的每个绕组包括通过连接顶部和底部导线的垂直导电通孔连接的光刻图案化和电镀的顶部和底部导线,其中初级线圈和次级线圈的横向相邻的顶部导线具有彼此面对的侧表面,并且其中初级线圈和次级线圈的横向相邻的底部导线具有彼此相对的侧表面,其中所述侧表面中的至少一些包括选自圆形侧表面、倾斜侧表面和阶梯侧表面的电场减小结构。

5、在本文描述的另一个方面中,一种制造导线的方法,包括在所述基板的顶表面上形成掩模层,所述掩模层具有沿着垂直于所述基板的顶表面的垂直方向的厚度,形成穿过所述掩模层的开口,从而暴露所述基板的顶表面上的区域,其中所述开口的侧壁的至少一部分包括曲率半径大于1微米的凹曲面,并且在所述基板的顶表面的暴露区域上电镀金属。

6、在本文描述的另一个方面中,一种制造导线的方法包括:在基板的顶表面上形成第一掩模层,其中第一掩模层沿着垂直于基板的顶表面的垂直方向具有第一厚度,形成穿过第一掩模层的第一开口以暴露基板的顶表面上的区域,其中所述开口具有沿着平行于所述基板的主表面的横向方向的宽度,并且在所述第一掩模层和所述基板的顶表面的暴露区域上电镀第一金属。该方法还包括:在第一掩模层上形成第二掩模层,其中第二掩膜层沿着垂直于基板的主表面的垂直方向具有第二厚度;形成穿过第二掩模层的第二开口,以暴露第一金属和第一掩模层上的区域,第二开口沿平行于基板的主表面的横向方向具有最大宽度,其中第二开口的至少一个侧壁包括曲率半径大于1微米的凹曲面,以及在所述第二掩模层、和所述第一金属、和所述第一掩模层的暴露区域上电镀第二金属。

技术特征:

1.一种集成电路器件,包括:

2.根据权利要求1所述的集成电路器件,其中所述顶部导线的侧表面的圆形凸起部分具有超过所述第一厚度的15%的曲率半径。

3.根据权利要求1所述的集成电路器件,其中所述底部导线和所述顶部导线分别形成在底部金属化层和上部金属化层处,其中所述顶部金属化层和所述底部金属化层是所述集成电路的不同金属化层,均至少包括通过电镀形成的金属化部分和嵌入所述金属化部分的金属间电介质部分。

4.根据权利要求3所述的集成电路器件,其中所述第一导电通孔至少包括电镀在所述底部导线上的下段和电镀在所述顶部导线上的上段。

5.根据权利要求1所述的集成电路器件,其中所述顶部导线的侧表面还包括具有一个或多个侧表面部分的阶梯部分,并且其中单个侧表面部分是基本上垂直于所述主表面的平坦表面。

6.根据权利要求5所述的集成电路器件,其中所述顶部导线还包括沿所述垂直轴具有第一厚度的顶部垂直部分和沿所述垂直轴具有第二厚度的底部垂直部分,所述顶部垂直部分包括所述侧表面的圆形部分,并且所述底部垂直部分包括所述侧表面的阶梯部分,并且其中所述顶部垂直部分的平均宽度大于所述底部垂直部分的宽度。

7.根据权利要求6所述的集成电路器件,其中所述底部垂直部分的第二厚度等于在所述顶部垂直部分与所述底部垂直部分之间的界面处所述底部垂直部分的宽度与所述顶部垂直部分的宽度之间的差值的一半。

8.根据权利要求1所述的集成电路器件,其中所述顶部导线和底部导线中的一个或两个的侧表面的圆形凸起部分的曲率半径大于3微米。

9.根据权利要求1所述的集成电路器件,还包括光刻图案化的次级线圈,所述次级线圈包括:

10.根据权利要求9所述的集成电路器件,其中所述第二顶部导线的侧表面的圆形凸起部分具有超过所述第一厚度的15%的曲率半径。

11.根据权利要求9所述的集成电路器件,其中所述初级线圈和所述次级线圈彼此交错并围绕所述绕组轴缠绕,使得所述初级绕组的绕组与所述次级绕组的绕组沿着所述绕组轴交替。

12.根据权利要求9所述的集成电路器件,其中所述顶部导线和所述第二顶部导线在顶部金属化水平光刻共图案化。

13.根据权利要求9所述的集成电路器件,其中所述底部和第二底部导线的圆形凸起部分形成在所述底部导线和所述第二底部导线的彼此直接面对的侧表面的顶部和底部角部中的一个或两个上。

14.一种集成电路器件,包括:

15.根据权利要求14所述的集成电路器件,其中所述顶部导线的负倾斜侧表面和顶表面以及所述底部导线的正倾斜侧表面和底表面之间的锐角小于70度。

16.根据权利要求14所述的集成电路器件,其中所述顶部导线沿着平行于所述主表面的横向轴的宽度沿着垂直于所述主表面的垂直轴从所述顶部导线的顶表面到底表面减小。

17.根据权利要求16所述的集成电路器件,其中所述底部导线沿着平行于所述主表面的横向轴的宽度沿着所述垂直轴从所述底部导线的顶表面到底表面增加。

18.根据权利要求14所述的集成电路器件,其中所述底部导线和所述顶部导线分别形成在底部金属化层和上部金属化层处,其中所述顶部金属化层和所述底部金属化层是所述集成电路的不同金属化层,均至少包括通过电镀形成的金属化部分和嵌入所述金属化部分的金属间电介质部分。

19.一种集成电路器件,包括:

20.根据权利要求19所述的集成电路器件,其中所述底部导线的侧表面包括具有一个或多个侧表面部分的阶梯部分,并且其中单个侧表面部分是基本上垂直于所述主表面的平坦表面。

技术总结

本公开涉及电流或电容隔离器的成形金属边缘。所公开的技术一般涉及用于通过电镀形成的集成电路器件的光刻限定的导线,更具体地,涉及成形为减小集成和单片变压器和隔离器的导线周围的电场分布中的电场大小的导线。

技术研发人员:M·T·坎蒂,S·迪亚哈姆,J·库比克,P·M·拉姆伯金,陈宝兴,Y·原,J·G·沙纳汉

受保护的技术使用者:亚德诺半导体国际无限责任公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!