多通道模数转换器高效控制采样及中断系统的制作方法

本申请涉及数据采集,特别涉及现场可编程的系统级芯片(fieldprogrammable soc,简称fpsoc)中的数据采集技术。

背景技术:

1、fpsoc是一种现场可编程的系统级芯片解决方案。它是一种把多个现场可编程逻辑单元(fpgas)和其他系统组件(如处理器、存储器、i/o接口等)集成在一起的芯片。fpsoc的优点是能够提供高速、高效和可扩展的处理能力,并且在设计时可以根据需求进行定制。同时,fpsoc还具有更低的能耗和更小的封装尺寸,这使得它成为高密度、紧凑型的设计的理想选择。因此,近年来,fpsoc的应用领域十分广泛,如通信、计算机、消费电子、医疗、军事和航空航天等。它们可以用于解决复杂的系统级问题,如高速数据处理、实时图像处理、高速通信和信号处理等。

2、然而,现有的技术中,fpsoc中模拟数字转换器(analog to digital converter,简称adc)数据采样操作效率较低,如果需要外挂阈值判断电路的话,会需要消耗额外的时钟周期来进行数据的读取与搬移,会极大增加单笔数据采集判断的时间,降低adc的使用效率。

3、另一方面,现有技术中,fpsoc中adc数据采集的中断模式单一,在fpga中的内置adc常用于模拟量的监测如电压检测和环境温度检测。如果想要对模数转换后的监测数据进行阈值判断,需要外置判断逻辑,由于是多通道的adc数据,会消耗大量fpga的lut资源。

4、因此,fpsoc中adc数据采集的效率还有待进一步提高。

技术实现思路

1、本申请的目的在于提供一种多通道模数转换器高效控制采样及中断系统,能够显著提高fpsoc中adc数据采集效率。

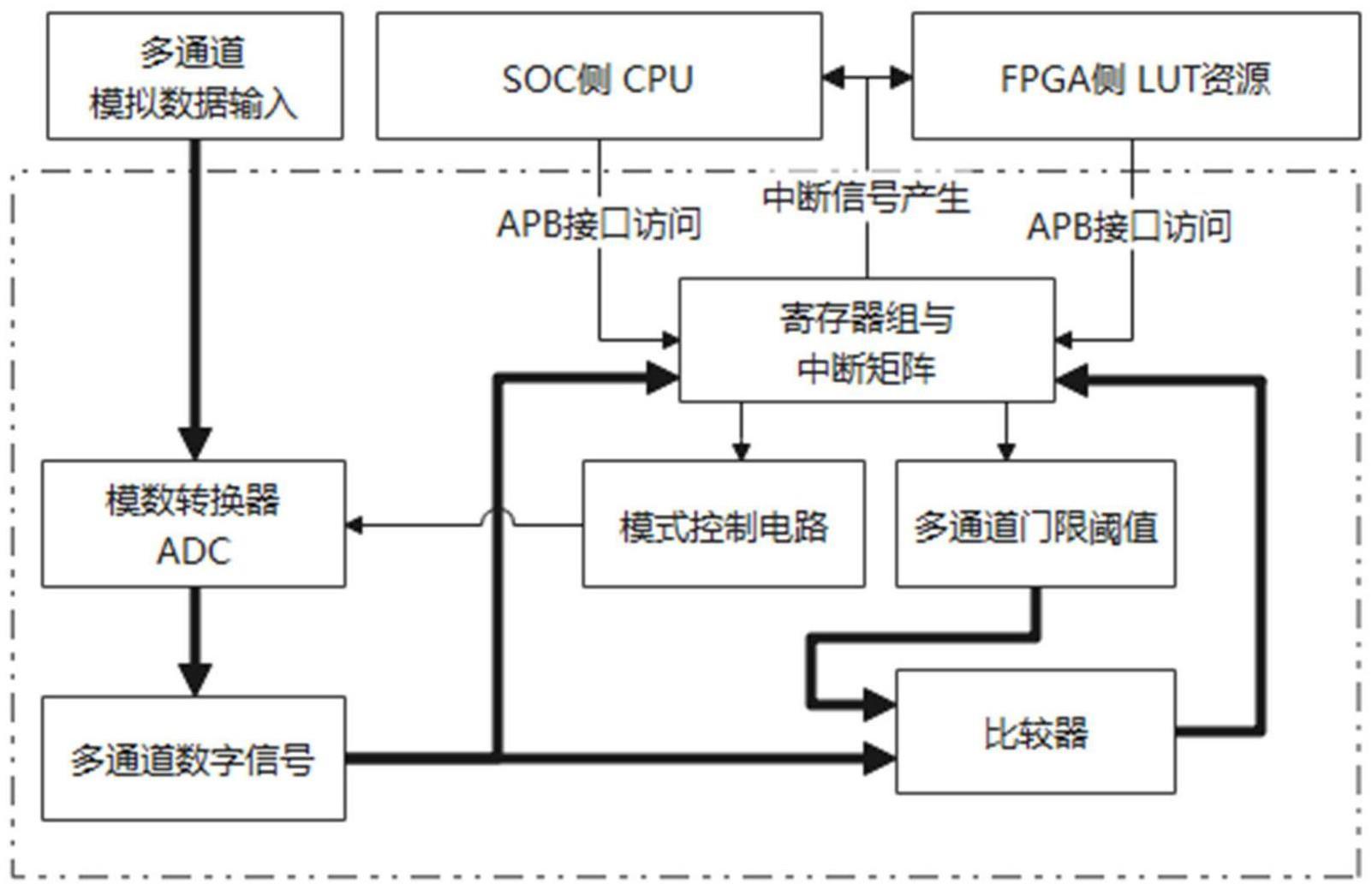

2、本申请公开了一种多通道模数转换器高效控制采样及中断系统,包括:

3、寄存器组;

4、模数转换器,对输入的n个通道的模拟信号进行采样转换成n个通道的数字信号,输出到所述寄存器组,n为大于1的整数;

5、n个比较器,每个比较器与所述模数转换器的一个通道对应,用于将所述寄存器组提供的门限阈值和对应通道输出的数字信号比较,将比较结果输出到中断矩阵;

6、中断矩阵,用于根据所述比较器输出的比较结果和该中断矩阵中配置的中断触发条件,触发中断信号。

7、在一个优选例中,还包括:

8、模式控制电路,用于根据所述寄存器组提供的控制信息控制所述模数转换器的运行模式。

9、在一个优选例中,还包括:

10、所述门限阈值有n组,每一组门限阈值对应一个比较器。

11、在一个优选例中,还包括:

12、每一组所述门限阈值包括一个或多个门限阈值。

13、本申请还公开了一种现场可编程的系统级芯片包括控制器和前文描述的多通道模数转换器高效控制采样及中断系统;

14、所述控制器用于配置所述寄存器组中的控制信息和门限阈值,和,在收到所述中断矩阵输出的中断信号时,进入中断处理函数,访问所述中断矩阵定位中断来源,以确定哪一个通道出现了超出阈值的情况。

15、在一个优选例中,所述控制器还用于根据中断来源确定触发中断的比较器,从所述寄存器组中读取该比较器输出的比较结果和输入该比较器的数字信号。

16、在一个优选例中,所述控制器包括处理器和\或现场可编程逻辑门阵列侧的查找表资源。

17、在一个优选例中,所述处理器包括中央处理器。

18、在一个优选例中,所述控制器和\或所述查找表资源通过先进外围总线耦合到所述寄存器组。

19、在一个优选例中,还包括传感器,所述传感器输出的模拟信号耦合到所述模数转换器的输入端。

20、技术效果:

21、在本申请实施方式的fpsoc内置的多通道adc高效控制采样及中断系统中,添加了阈值比较逻辑,在实现阈值比较功能的同时,能够节约fpga中的lut资源,以及减少数据处理的时间;进一步的,本申请实施方式中使用了中断矩阵来定位中断来源,节约了中断处理时间,通道数越多,节省的时间越显著;进一步的,本申请实施方式中使用soc侧的cpu或者fpga侧的用户逻辑(lut资源)来配置模数转换器adc,专用与通用并存,增加了模数转换器adc使用的灵活性。

22、本申请的说明书中记载了大量的技术特征,分布在各个技术方案中,如果要罗列出本申请所有可能的技术特征的组合(即技术方案)的话,会使得说明书过于冗长。为了避免这个问题,本申请上述

技术实现要素:

中公开的各个技术特征、在下文各个实施方式和例子中公开的各技术特征、以及附图中公开的各个技术特征,都可以自由地互相组合,从而构成各种新的技术方案(这些技术方案均因视为在本说明书中已经记载),除非这种技术特征的组合在技术上是不可行的。例如,在一个例子中公开了特征a+b+c,在另一个例子中公开了特征a+b+d+e,而特征c和d是起到相同作用的等同技术手段,技术上只要择一使用即可,不可能同时采用,特征e技术上可以与特征c相组合,则,a+b+c+d的方案因技术不可行而应当不被视为已经记载,而a+b+c+e的方案应当视为已经被记载。

技术特征:

1.一种多通道模数转换器高效控制采样及中断系统,其特征在于,包括:

2.如权利要求1所述的多通道模数转换器高效控制采样及中断系统,其特征在于,还包括:

3.如权利要求1所述的多通道模数转换器高效控制采样及中断系统,其特征在于,还包括:

4.如权利要求3所述的多通道模数转换器高效控制采样及中断系统,其特征在于,还包括:

5.一种现场可编程的系统级芯片,其特征在于,包括控制器和权利要求2所述的多通道模数转换器高效控制采样及中断系统;

6.如权利要求5所述的现场可编程的系统级芯片,其特征在于,所述控制器还用于根据中断来源确定触发中断的比较器,从所述寄存器组中读取该比较器输出的比较结果和输入该比较器的数字信号。

7.如权利要求5所述的现场可编程的系统级芯片,其特征在于,所述控制器包括处理器和\或现场可编程逻辑门阵列侧的查找表资源。

8.如权利要求7所述的现场可编程的系统级芯片,其特征在于,所述处理器包括中央处理器。

9.如权利要求7所述的现场可编程的系统级芯片,其特征在于,所述控制器和\或所述查找表资源通过先进外围总线耦合到所述寄存器组。

10.如权利要求5所述的现场可编程的系统级芯片,其特征在于,还包括传感器,所述传感器输出的模拟信号耦合到所述模数转换器的输入端。

技术总结

本申请涉及数据采集技术领域,公开了一种多通道模数转换器高效控制采样及中断系统,包括:寄存器组;模数转换器,对输入的N个通道的模拟信号进行采样转换成N个通道的数字信号,输出到所述寄存器组,N为大于1的整数;N个比较器,每个比较器与所述模数转换器的一个通道对应,用于将所述寄存器组提供的门限阈值和对应通道输出的数字信号比较,将比较结果输出到中断矩阵;中断矩阵,用于根据所述比较器输出的比较结果和该中断矩阵中配置的中断触发条件,触发中断信号。本申请能够显著提高FPSOC中ADC数据采集效率。

技术研发人员:叶澍霖

受保护的技术使用者:上海安路信息科技股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!