具有减少的数据路径延时的逐次逼近寄存器模/数转换器的制作方法

本公开大体上涉及通信系统,包含(但不限于)包含逐次逼近寄存器模/数转换器(sar adc)的通信系统。

背景技术:

1、通信及计算装置的最新发展要求高数据速率。举例来说,网络交换机、路由器、集线器或任何通信装置可高速(例如,1mbps到100gbps)交换数据,以实时流式传输数据或以无缝方式处理大量数据。为了在数字域中高效地处理数据,信号的幅度或电压可由多个位表示,且信号可通过缆线或无线介质在两个或更多个通信装置之间交换。例如,1.2v的信号可表示为字节(b),例如00010110,且1.3v的信号可表示为b,例如00011001。为了将输入信号的电压转换为对应的位,一些通信装置实施sar adc。例如,sar adc可通过逐次逼近来确定对应于输入信号的多个位。工艺、电压及温度(pvt)变化可能会影响sar adc的速度、精确度及/或准确度。

技术实现思路

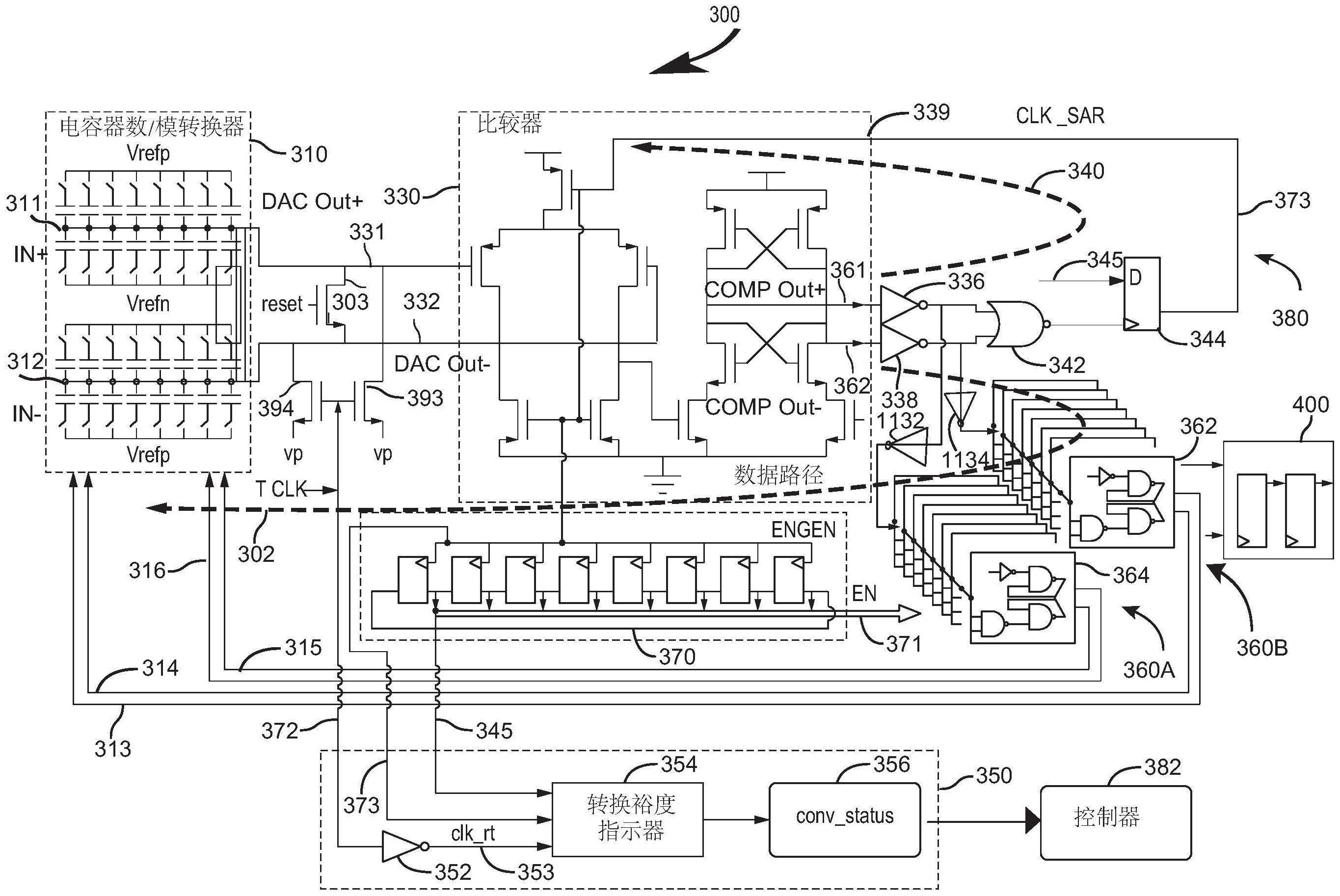

1、在一个方面中,本申请案涉及一种装置,其包括:数/模转换(dac)电路;比较器电路,其耦合到具有输出的dac电路;第一组存储电路,其耦合到所述比较器电路及所述dac电路,所述第一组存储电路经配置以存储对应于输入电压的多个第一位;以及比较器驱动器,其位于所述输出与所述第一组存储电路之间,其中所述比较器驱动器包括第一驱动器及第二驱动器,所述第一驱动器耦合到所述第一组存储电路的第一存储电路的输入,且所述第二驱动器耦合到所述第一组存储电路内的第二组存储电路的输入。

2、在另一方面中,本申请案涉及一种装置,其包括:数/模转换(dac)电路,其包括复位晶体管;比较器电路,其耦合到所述dac电路;第一组存储电路,其耦合到所述比较器电路及所述dac电路,所述第一组存储单元经配置以存储对应于由所述比较器电路提供的输入电压的多个第一位;以及启用电路,其经配置以向所述第一组存储电路提供启用信号,其中所述启用信号中的一者被提供到所述复位晶体管以复位所述数/模转换dac电路。

3、在另一方面中,本申请案涉及一种装置,其包括:数/模转换(dac)电路;比较器电路,其耦合到所述dac电路;第一组存储电路,其耦合到所述比较器电路及所述dac电路,所述第一组存储电路经配置以存储对应于输入电压的多个第一位,其中所述第一组存储电路是具有耦合到所述dac电路的反馈输入的输出的比率锁存器。

技术特征:

1.一种装置,其包括:

2.根据权利要求1所述的装置,其中所述第二组存储电路不包含所述第一存储电路。

3.根据权利要求1所述的装置,其中所述第一存储电路存储由所述比较器电路提供的所述第一位中的最高有效位。

4.根据权利要求1所述的装置,其中所述第二组存储电路包括所述第一组存储电路中的所有剩余存储电路。

5.根据权利要求1所述的装置,其进一步包括到所述比较器电路及所述dac电路的第三组存储电路,所述第三组存储电路经配置以存储对应于所述输入电压的多个第二位。

6.根据权利要求5所述的装置,其中所述比较器驱动器包括第三驱动器及第四驱动器,所述第三驱动器耦合到所述第三组存储电路的第二存储电路的输入,且所述第四驱动器耦合到所述第三组存储电路内的第四组存储电路的输入。

7.根据权利要求6所述的装置,其中所述第三驱动器耦合到所述第四驱动器的输入。

8.根据权利要求1所述的装置,其中所述第一驱动器耦合到所述第二驱动器的输入。

9.根据权利要求1所述的装置,其中所述数/模转换dac电路由所述第一组存储电路接收的启用零信号复位。

10.一种装置,其包括:

11.根据权利要求10所述的装置,其中所述启用信号中的所述一者是启用零信号。

12.根据权利要求11所述的装置,其中在与所述复位晶体管相关联的复位路径中提供延迟以确保不影响最后的转换。

13.根据权利要求11所述的装置,其中使用所述启用零信号停用所述比较器电路的比较器时钟信号。

14.根据权利要求10所述的装置,其中所述电路包括多个触发器,所述触发器由比较器时钟信号时控。

15.根据权利要求10所述的装置,其进一步包括转换状态电路,且其中所述转换状态电路使用所述启用信号中的所述一者来确定转换裕度。

16.一种装置,其包括:

17.根据权利要求16所述的装置,其中所述锁存器是置位及复位锁存器。

18.根据权利要求16所述的装置,其进一步包括:

19.根据权利要求18所述的装置,其中所述第一存储电路存储由所述比较器电路提供的所述第一位中的最高有效位,且所述第二组存储电路包括所述第一组存储电路中的所有剩余存储电路。

20.根据权利要求16所述的装置,其进一步包括启用电路,所述启用电路经配置以向所述第一组存储电路提供启用信号,其中所述启用信号中的一者被提供到所述数/模转换dac电路中的复位晶体管,以复位所述数/模转换dac电路。

技术总结

系统及方法与一种具有减少的数据路径延时的逐次逼近寄存器模/数转换器SAR ADC相关。所述SAR ADC包含:采样及数/模转换DAC电路,其经配置以采样输入电压;比较器电路,其耦合到所述采样及DAC电路并具有输出;第一组存储电路;以及比较器驱动器。所述比较器驱动器安置在所述输出与所述第一组存储电路之间(例如,比率锁存)。所述第一组存储电路耦合到所述比较器电路以及所述采样及DAC电路。所述比较器驱动器可包含第一驱动器及第二驱动器。所述第一驱动器耦合到所述第一组存储电路的第一存储电路的第一输入,且所述第二驱动器耦合到所述第一组存储电路内的第二组存储电路的第一输入。

技术研发人员:乌拉斯·辛格,纳米克·柯贾曼,穆罕默德明·托拉比,梅萨姆·霍纳瓦·纳扎里安,穆罕默德·巴图汉·达亚尼克,德龙·崔,曹军

受保护的技术使用者:安华高科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!