一种抑制EMC干扰的FPC排线及智能BDU的制作方法

本发明涉及电池配件,尤其涉及一种抑制emc干扰的fpc排线及智能bdu。

背景技术:

1、电动汽车的电气回路包括三个部分:动力电池系统、电机系统、高压附件系统,作为高压部分联结成为电气网络的bdu系统,其质量问题对于整车安全至关重要,电池能量分配单元(bdu)是电动汽车高压回路上的重要部件,其控制着高压电气回路的上下电过程,预充过程,充电过程,bdu 产品的特征参数是否满足合格条件,对整车的使用寿命,控制策略,高压电安全具有重要影响。

2、电池bdu内的线束一般是裸露在多个电气元件的外部,并对应与各个电气元件连接,这种连接方式会导致bdu内线路连接复杂,线束连接所占空间较大,对bdu 的集成设计造成一定的困难,且采用线束时,需要人工将端子与线束进行连接,导致人工成本较大。

3、授权公告号为cn218333933u的用于电池的bdu、电池及用电装置,其公开了采用fpc柔性板代替线束,连接bdu内的各个器件,从而降低bdu的整体重量与所占空间,且fpc可直接由产线进行生产,无需人工进行端子连接。

4、智能bdu具有继电器控制、电流采集、电压采集、内外通信等功能,其中控制功能、电流检测功能、功能保护等是普通bdu不具备的,fpc可应用到智能bdu内,但是,在智能bdu中,继电器的吸合断开或者信号采集,均存在emc干扰,线束可通过绞合形成双绞线的方式抑制emc干扰,而fpc使用在智能bdu内时,缺少抗干扰的手段,导致智能bdu接收信号进行处理时,会影响检测精度,甚至产生误判。

技术实现思路

1、有鉴于此,本发明提出了一种抑制emc干扰的fpc排线及智能bdu,通过类似双绞线的设置并增加抑制干扰的电路,替换传统fpc排线,从而抑制电路导通时,电路中所形成的emc干扰,保障智能bdu的稳定工作。

2、本发明的技术方案是这样实现的:

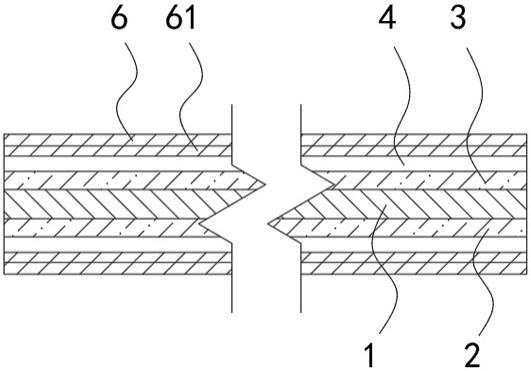

3、一方面,提供了一种抑制emc干扰的fpc排线,包括基层、第一走线层、第二走线层、两个绝缘层与干扰抑制电路,其中,

4、第一走线层设置在基层的一侧上,所述第一走线层包括第一导电线;

5、第二走线层设置在基层的另一侧上,所述第二走线层包括第二导电线,所述第二导电线在第一走线层上的正投影与第一导电线连续交错;

6、两个绝缘层分别覆盖在第一走线层与第二走线层相背的一侧;

7、干扰抑制电路设置在基层上,并与第一导电线和第二导电线电性连接,用于电路中的emc干扰。

8、在以上技术方案的基础上,优选的,还包括两个屏蔽层,两个所述屏蔽层分别设置在两个绝缘层相背的一侧。

9、进一步优选的,所述屏蔽层包括gnd层,所述gnd层设置在绝缘层上,且具有导电性,所述gnd层接地。

10、在以上技术方案的基础上,优选的,所述干扰抑制电路包括两个滤波电容,两个所述滤波电容串联,且分别与第一导电线和第二导电线电性连接。

11、在以上技术方案的基础上,优选的,所述干扰抑制电路包括两个二极管,两个所述二极管的正极分别与第一导电线和第二导电线电性连接,两个所述二极管的负极相接。

12、在以上技术方案的基础上,优选的,所述第一导电线与第二导电线的数量至少为一个,所述第一导电线与第二导电线一一对应。

13、进一步优选的,还包括接地线,所述接地线设置在基层上,且位于相邻两个第一导电线与相邻两个第二导电线之间。

14、另一方面,提供了一种智能bdu,包括智能pcba、高压采集控制板、多个电器元件以及上述fpc排线,其中,

15、智能pcba与高压采集控制板通过fpc排线电性连接;

16、智能pcba与各个电器元件均通过fpc排线电性连接。

17、在以上技术方案的基础上,优选的,所述多个电器元件包括主正继电器、主负继电器、霍尔电流传感器与分流器,其中,

18、主正继电器的低压控制端与智能pcba的第一输出端电性连接;

19、主负继电器的低压控制端与智能pcba的第二输出端电性连接;

20、霍尔电流传感器的输出端与智能pcba的第一输入端电性连接;

21、分流器的输出端与智能pcba的第二输入端电性连接。

22、进一步优选的,所述fpc排线包括2pin排线、4pin排线、6pin排线与8pin排线,其中,

23、2pin排线包括一个第一导电线与一个第二导电线,所述主负继电器与智能pcba通过2pin排线,所述主正继电器与智能pcba通过2pin排线电性连接;

24、4pin排线包括两个第一导电线与两个第二导电线,所述智能pcba的第三输入端与高压采集控制板的输出端通过4pin排线,所述霍尔电流传感器与智能pcba通过4pin排线电性连接;

25、6pin排线包括三个第一导电线与三个第二导电线,分流器与智能pcba通过6pin排线电性连接;

26、8pin排线包括四个第一导电线与四个第二导电线,所述智能pcba的第三输出端与高压采集控制板的输入端通过8pin排线电性连接。

27、本发明的抑制emc干扰的fpc排线及智能bdu相对于现有技术具有以下有益效果:

28、通过将第一导电线与第二导电线设置成类似双绞线,并在成对的第一导电线与第二导电线之间设置干扰抑制电路,有效的抑制电路中的共模干扰,并对其形成的电磁干扰进行屏蔽,避免其干扰产生的辐射,对其他器件造成影响,同时设置的干扰抑制电路可在信号传输过程中对其进行处理,提高信号传输精度,降低误判概率;

29、设置屏蔽层与接地线,可进一步的降低第一走线层与第二走线层传输信号时,对外形成的辐射,同时屏蔽外部干扰,提高信号传输稳定性及传输距离;

30、采用抑制emc干扰的fpc排线替换智能bdu内的传统线束,在节省布线空间,方便走线设计的同时,对信号传输过程中的干扰进行抑制与屏蔽,提高智能pcba接收信号的精度,降低误判概率。

技术特征:

1.一种抑制emc干扰的fpc排线,其特征在于:包括基层(1)、第一走线层(2)、第二走线层(3)、两个绝缘层(4)与干扰抑制电路(5),其中,

2.如权利要求1所述的抑制emc干扰的fpc排线,其特征在于:还包括两个屏蔽层(6),两个所述屏蔽层(6)分别设置在两个绝缘层(4)相背的一侧。

3.如权利要求2所述的抑制emc干扰的fpc排线,其特征在于:所述屏蔽层(6)包括gnd层(61),所述gnd层(61)设置在绝缘层(4)上,且具有导电性,所述gnd层(61)接地。

4.如权利要求1所述的抑制emc干扰的fpc排线,其特征在于:所述干扰抑制电路(5)包括两个滤波电容(51),两个所述滤波电容(51)串联,且分别与第一导电线(21)和第二导电线(31)电性连接。

5.如权利要求1所述的抑制emc干扰的fpc排线,其特征在于:所述干扰抑制电路(5)包括两个二极管(52),两个所述二极管(52)的正极分别与第一导电线(21)和第二导电线(31)电性连接,两个所述二极管(52)的负极相接。

6.如权利要求1所述的抑制emc干扰的fpc排线,其特征在于:所述第一导电线(21)与第二导电线(31)的数量至少为一个,所述第一导电线(21)与第二导电线(31)一一对应。

7.如权利要求6所述的抑制emc干扰的fpc排线,其特征在于:还包括接地线(7),所述接地线(7)设置在基层(1)上,且位于相邻两个第一导电线(21)与相邻两个第二导电线(31)之间。

8.一种智能bdu,其特征在于:包括智能pcba(101)、高压采集控制板(102)、多个电器元件(103)以及权利要求1-7中任意一项所述的fpc排线(10),其中,

9.如权利要求8所述的智能bdu,其特征在于:所述多个电器元件(103)包括主正继电器(1031)、主负继电器(1032)、霍尔电流传感器(1033)与分流器(1034),其中,

10.如权利要求9所述的智能bdu,其特征在于:所述fpc排线(10)包括2pin排线(1001)、4pin排线(1002)、6pin排线(1003)与8pin排线(1004),其中,

技术总结

本发明涉及电池配件技术领域,并提出了一种抑制EMC干扰的FPC排线及智能BDU,包括基层、第一走线层、第二走线层、两个绝缘层与干扰抑制电路,第一走线层设置在基层的一侧上,所述第一走线层包括第一导电线;第二走线层设置在基层的另一侧上,所述第二走线层包括第二导电线,所述第二导电线在第一走线层上的正投影与第一导电线连续交错;两个绝缘层分别覆盖在第一走线层与第二走线层相背的一侧;干扰抑制电路设置在基层上,并与第一导电线和第二导电线电性连接,用于抑制电路中的EMC干扰。该抑制EMC干扰的FPC排线,可有效的抑制电路中的共模干扰,对电磁干扰进行屏蔽,避免干扰向外辐射,提高信号传输精度。

技术研发人员:杜朝晖,李瑶,徐伟,孙宇澄,邵仁强,严俊飞,严祖冬,陈勇,张辉,王杭廷,蒲小勇,彭勇辉,吴昊

受保护的技术使用者:武汉嘉晨电子技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!