一种基于FPGA的高性能FIR滤波器计算电路结构

本发明涉及fpga底层计算电路设计领域,具体涉及一种基于fpga的高性能fir滤波器计算电路结构的实现。

背景技术:

1、近年来,信息技术的飞速发展使得有越来越多的领域需要处理海量的数据,需处理的数据位宽越来越大,对精度、速度、资源利用率等的要求也越来越高,使得高性能计算在越来愈多的领域不断体现其价值。

2、fpga(fieldprogrammablegatearray,现场可编程门阵列)技术可以提供丰富的计算资源和高度的设计灵活性,具有计算能力强、应用广泛、功耗较低等优点,基于fpga研究上述高性能计算电路有着重要的优势和意义。

3、fir滤波器作为数字信号处理的重要组成部分,在带宽选择、降噪等众多方面都起着至关重要的作用。其功能是把输入序列通过一定的运算变换成输出序列。不同的运算处理方法决定了不同的滤波器的不同实现功能。一个数字fir滤波器主要由乘法器和加法器构成,因此,这两个部分的性能对于fir滤波器的整体性能来说非常重要。

4、有鉴于此,基于fpga设计出性能更佳的fir滤波器计算电路结构有重要意义。

技术实现思路

1、本发明的目的在于提供一种基于fpga的高性能fir滤波器计算电路设计,旨在得到基于fpga实现的硬件资源利用率更高的fir滤波器计算电路结构。

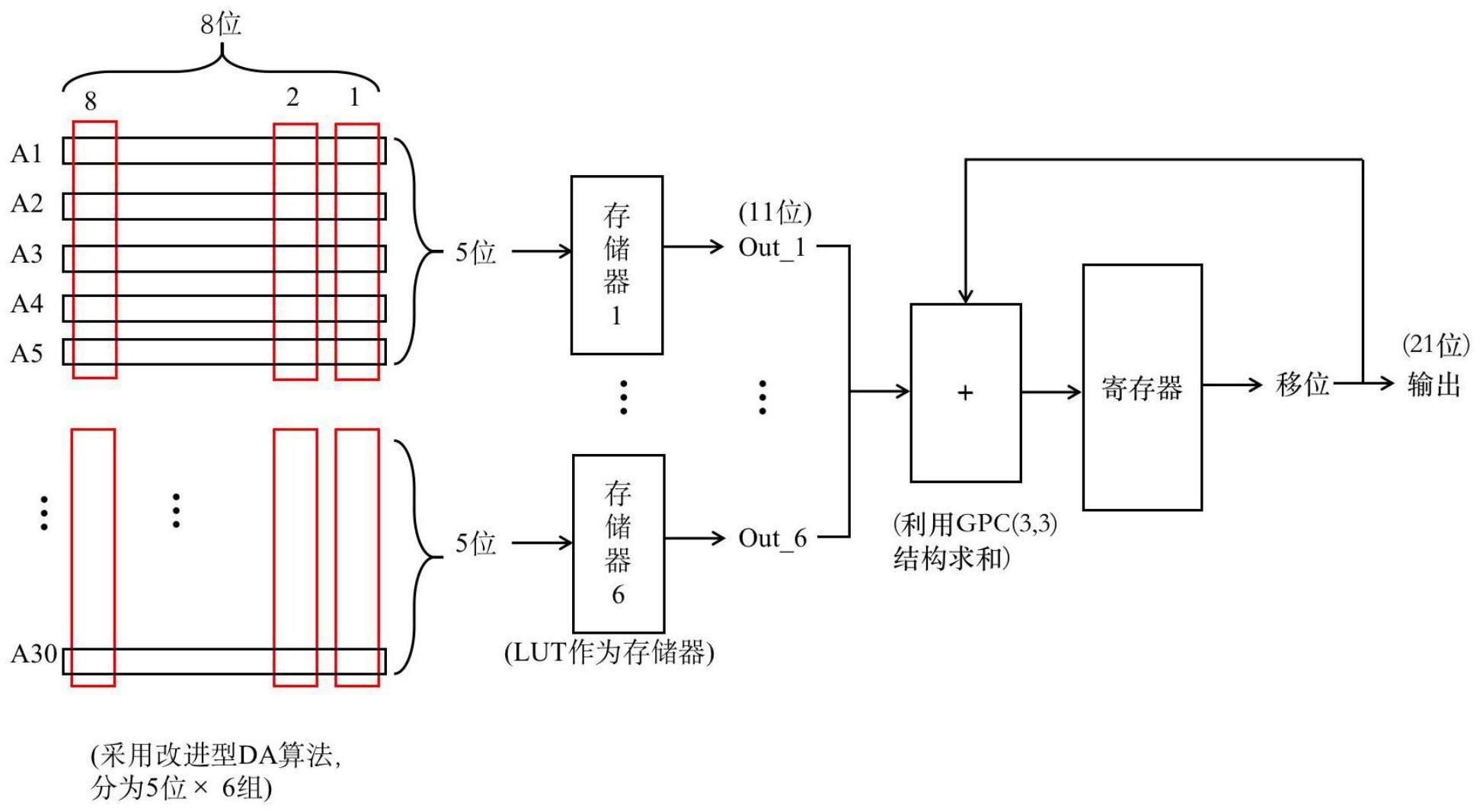

2、本发明采用的技术方案是:针对高性能fir滤波计算的需求,设计了结合基于lut结构进行分组的da算法和gpc(3,3)结构两种方法的高性能fir滤波器计算电路结构。且基于原语(primitive)进行编写。

3、分布式算法(distributedarithmetic,da)最初于1973年由croisier提出,是一种重要的硬件实现技术,并常常被应用于fir滤波器的设计中,基于该算法的fir滤波器可以采用纯硬件的方式来实现数字fir滤波。da算法运用了fpga中的查找表结构,将系数固定的乘积累加运算(multiplyaccumulate,mac)转换成查找表操作,用简单的加法代替了乘法运算。da算法的优点是相较于直接实现乘法器,该算法运算速度更快,在硬件规模上也有一定的改善,适合应用在高速、实时、快变的数字信号处理中。

4、本发明中使用了基于lut结构进行分组的da算法。该算法根据fpga中lut的结构特点,对输入数据进行分组,可以得到更高的硬件利用效率。该算法针对lut输入位数为5的情况,把输入数据分为5位一组,能得到更高的lut资源利用率。具体可参看本发明实施例部分。

5、广义并行计数器(generalizedparallelcounter,gpc)结构于2009年被hadiparandeh-afshar等人提出,gpc结构通过充分利用fpga中查找表(lut)与进位链(carrychain)的关系,在完成多组多位数据的求和操作时,相比于传统的加法计算单元通常能够得到更优的运算性能,减少lut资源的使用率,提高面积利用率。多种不同的gpc构成了庞大的gpc库,在设计过程中,人们可以根据操作数的的不同选取恰当的gpc结构来进行计算,与此同时,人们也继续设计着新的gpc结构以丰富已有的gpc库。

6、本发明中使用了gpc(3,3)结构,该gpc(3,3)结构可以一次性完成两列3位数据的求和运算;在其求和运算的过程中,lut将某一列加数的和与进位拆分开,通过进位链计算该列中3位与上一位进位的和,再将这3位求和产生的进位与进位链中的进位传递到下一位。该gpc(3,3)结构的合理组合可以实现高效的高阶高位数加法操作。

7、本发明的高性能fir滤波器计算电路中,上述基于lut结构进行分组的da算法应用于本高性能fir滤波器计算单元中的数据输入部分及存储器部分,通过查找表操作得到部分积结果,上述gpc(3,3)结构应用于本高性能fir滤波器计算单元的各组部分积求和;最后再通过寄存器移位相加得到最终的计算结果。

8、本发明的高性能fir滤波器计算电路中,采用了自底向上(bottom-up)的程序构造方式,基于原语(primitive)进行编写。上述采用了基于lut结构进行分组的da算法的存储器部分由多个add_lut模块组成,上述gpc(3,3)结构由四个add_lut模块以及一个carry4组成,这里的carry4为进位链的原语,add_lut为lut的原语(本发明中原语调用lut和进位链的具体语法参考xilinxfpga手册)。

技术特征:

1.一种基于fpga的高性能计算电路结构,其特征在于:所述电路结构是针对高性能滤波计算的需求,提出了一种基于fpga实现的高性能fir滤波器计算电路结构,所述电路结构结合了广义并行计数器(generalizedparallelcounter,gpc)库中的gpc(3,3)结构和基于lut结构进行分组的da(distributedarithmetic,分布式运算)算法的一种计算电路结构。

2.根据权利要求1所述的高性能fir滤波器计算电路结构,其特征在于,相比于传统fir滤波器计算电路结构采用自顶向下(top-down)的程序构造方式,且运用可综合rtl代码编写等特点,所述高性能fir滤波器计算电路结构采用的是自底向上(bottom-up)的程序构造方式,且基于原语(primitive)进行编写,可以针对fpga进行更细粒度的优化。

3.根据权利要求1所述的基于lut结构进行分组的da算法,其特征在于:所述da算法应用于本高性能fir滤波器计算电路结构中的数据输入部分及存储器部分,根据fpga中的lut结构特点,对输入数据进行分组,能减少fir滤波器的硬件资源使用量。

技术总结

本发明公开了一种基于FPGA的高性能FIR滤波器计算电路结构。本发明结合了GPC(3,3)结构和基于LUT结构进行分组的DA算法两种方法,充分利用了FPGA芯片上的进位链结构和LUT的结构特征,且采用了自底向上的程序构造方式,运用原语进行编写。本发明能减少FIR滤波器的硬件资源使用量。

技术研发人员:李辉,刘虹雨

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!