存储器及其形成方法与流程

本发明涉及半导体制造,尤其涉及一种存储器及其形成方法。

背景技术:

1、随着现今科技快速的发展,半导体存储器被广泛地应用于电子装置中。垂直沟道存储器架构(vcat)相比较于传统架构(bcat)具有更高的存储密度,垂直沟道存储器架构(vcat)的电容接触与垂直沟道器件的有源区相连,字线结构形成在有源区内且表面与有源区平齐。

2、然而,垂直沟道存储器在形成过程中仍存在诸多问题。

技术实现思路

1、本发明解决的技术问题是提供一种存储器及其形成方法,增加对位线层的保护,进而提升器件性能。

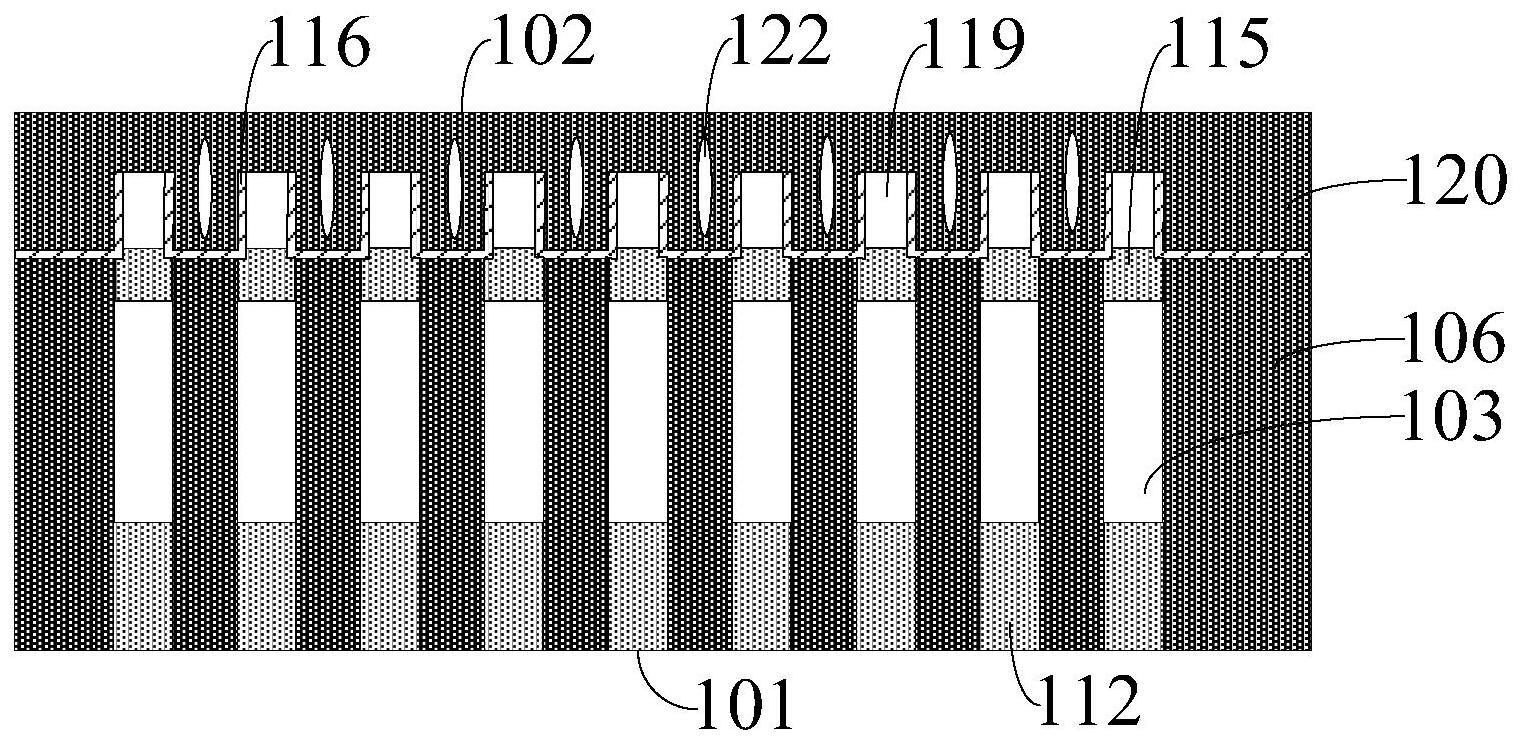

2、为解决上述问题,本发明提供一种存储器的形成方法,包括:提供衬底,所述衬底具有相对的第一面和第二面,所述衬底包括若干相互分立且平行于第一方向的有源区,且若干所述有源区沿第二方向排列,所述第一方向与所述第二方向垂直;在所述第一面上形成第一隔离层,所述第一隔离层位于相邻的所述有源区之间;自所述第二面向所述第一面的方向对所述衬底进行减薄处理,直至暴露出所述第一隔离层为止;自所述第二面向所述第一面的方向回刻蚀所述第一隔离层,暴露出所述有源区的部分侧壁表面;在暴露出的所述有源区的侧壁表面形成保护层;在形成所述保护层之后,在所述第二面上形成第二隔离层,所述第二隔离层覆盖所述保护层的侧壁;在形成所述第二隔离层之后,自所述第二面向所述第一面的方向回刻蚀所述有源区,在所述第二隔离层内形成位线开口;在所述位线开口内形成位线层;在形成所述位线层之后,去除所述第二隔离层;在去除所述第二隔离层之后,在所述第二面上形成第三隔离层,所述第三隔离层覆盖所述位线层和所述保护层,且所述第三隔离层内具有空腔。

3、可选的,在暴露出所述有源区的部分侧壁表面之后,且在形成所述保护层之前,还包括:对暴露出的所述有源区进行刻蚀处理,以减小暴露出的所述有源区的宽度尺寸。

4、可选的,所述保护层和所述第二隔离层的形成方法包括:在暴露出的所述有源区的侧壁和顶部表面、以及所述第一隔离层的表面形成保护材料层;在所述第二面上形成隔离材料层,所述隔离材料层覆盖所述保护材料层;自所述第二面向所述第一面的方向对隔离材料层和所述保护材料层进行平坦化处理,直至暴露出所述有源区的表面为止,形成所述保护层和所述第二隔离层。

5、可选的,所述保护层的材料包括:氮化硅、氮化钛或氧化铝。

6、可选的,所述位线层包括:多晶硅层、位于所述多晶硅层上的金属硅化物层、以及位于所述金属硅化物层上的金属层。

7、可选的,每个所述有源区均包括若干字线区和若干沟道区,且每个所述有源区中的若干所述字线区和若干所述沟道区沿所述第一方向间隔排列;在对所述衬底进行减薄之前,还包括:在每个所述字线区内形成字线栅沟槽,所述字线栅沟槽自所述第一面向所述第二面延伸,且所述字线栅沟槽沿所述第二方向贯穿所述有源区;在每个所述字线栅沟槽内形成两个电性隔离的字线栅结构。

8、可选的,在形成所述字线栅结构之后,还包括:自所述第一面向所述第二面的方向刻蚀部分所述沟道区,在所述衬底内形成若干平行于所述第二方向的隔离开口;在所述隔离开口内形成隔离结构;在每个所述沟道区第一面内形成第一源漏掺杂区;在所述第一面上形成若干电容结构,每个所述电容结构与一个所述第一源漏掺杂区电连接;在每个所述沟道区第二面内形成第二源漏掺杂区。

9、可选的,每个所述位线层与一个所述有源区中的若干所述第二源漏掺杂区电连接。

10、相应的,本发明技术方案中还提供一种存储器,包括:衬底,所述衬底具有相对的第一面和第二面,所述衬底包括若干相互分立且平行于第一方向的有源区,且若干所述有源区沿第二方向排列,所述第一方向与所述第二方向垂直;位于相邻的所述有源区之间的第一隔离层;位于所述第二面上的若干位线层,每个所述位线层与一个所述有源区电连接;位于所述位线层侧壁的保护层;位于所述第二面上的第三隔离层,所述第三隔离层覆盖所述位线层和所述保护层,且所述第三隔离层内具有空腔。

11、可选的,所述位线层的宽度尺寸小于所述有源区的宽度尺寸。

12、可选的,所述保护层的材料包括:氮化硅、氮化钛或氧化铝。

13、可选的,所述位线层包括:多晶硅层、位于所述多晶硅层上的金属硅化物层、以及位于所述金属硅化物层上的金属层。

14、可选的,每个所述有源区均包括若干字线区和若干沟道区,且每个所述有源区中的若干所述字线区和若干所述沟道区沿所述第一方向间隔排列。

15、可选的,还包括:位于每个所述字线区内的字线栅沟槽,所述字线栅沟槽自所述第一面向所述第二面延伸,且所述字线栅沟槽沿所述第二方向贯穿所述有源区;位于每个所述字线栅沟槽内的两个电性隔离的字线栅结构。

16、可选的,还包括:位于每个所述沟道区内的隔离开口;位于所述隔离开口内的隔离结构;位于每个所述沟道区第一面内的第一源漏掺杂区;位于所述第一面上的若干电容结构,每个所述电容结构与一个所述第一源漏掺杂区电连接;位于每个所述沟道区第二面内的第二源漏掺杂区。

17、可选的,每个所述位线层与一个所述有源区中的若干所述第二源漏掺杂区电连接。

18、与现有技术相比,本发明的技术方案具有以下优点:

19、本发明的技术方案的存储器的形成方法中,在暴露出的所述有源区的侧壁表面形成保护层,在去除所述第二隔离层的过程中,通过所述保护层对所述位线层的侧壁进行保护,进而有效减少对所述位线层造成的横向刻蚀,防止所述位线层出现倒塌的问题。另外,所述保护层还能够有效防止所述位线层的侧壁氧化,进而提升器件结构的性能。

20、进一步,在暴露出所述有源区的部分侧壁表面之后,且在形成所述保护层之前,还包括:对暴露出的所述有源区进行刻蚀处理,以减小暴露出的所述有源区的宽度尺寸。通过减少暴露出的所述有源区的宽度尺寸,进而减少所述位线层的宽度尺寸,以此增大相邻所述位线层之间的间距尺寸,进而降低相邻所述位线层之间的寄生电容。

21、本发明的技术方案的存储器中,通过所述保护层对所述位线层的侧壁进行保护,进而有效减少对所述位线层造成的横向刻蚀,防止所述位线层出现倒塌的问题。另外,所述保护层还能够有效防止所述位线层的侧壁氧化,进而提升器件结构的性能。

22、进一步,所述位线层的宽度尺寸小于所述有源区的宽度尺寸。通过减少暴露出的所述有源区的宽度尺寸,进而减少所述位线层的宽度尺寸,以此增大相邻所述位线层之间的间距尺寸,进而降低相邻所述位线层之间的寄生电容。

技术特征:

1.一种存储器的形成方法,其特征在于,包括:

2.如权利要求1所述存储器的形成方法,其特征在于,在暴露出所述有源区的部分侧壁表面之后,且在形成所述保护层之前,还包括:对暴露出的所述有源区进行刻蚀处理,以减小暴露出的所述有源区的宽度尺寸。

3.如权利要求1所述存储器的形成方法,其特征在于,所述保护层和所述第二隔离层的形成方法包括:在暴露出的所述有源区的侧壁和顶部表面、以及所述第一隔离层的表面形成保护材料层;在所述第二面上形成隔离材料层,所述隔离材料层覆盖所述保护材料层;自所述第二面向所述第一面的方向对隔离材料层和所述保护材料层进行平坦化处理,直至暴露出所述有源区的表面为止,形成所述保护层和所述第二隔离层。

4.如权利要求1所述存储器的形成方法,其特征在于,所述保护层的材料包括:氮化硅、氮化钛或氧化铝。

5.如权利要求1所述存储器的形成方法,其特征在于,所述位线层包括:多晶硅层、位于所述多晶硅层上的金属硅化物层、以及位于所述金属硅化物层上的金属层。

6.如权利要求1所述存储器的形成方法,其特征在于,每个所述有源区均包括若干字线区和若干沟道区,且每个所述有源区中的若干所述字线区和若干所述沟道区沿所述第一方向间隔排列;在对所述衬底进行减薄之前,还包括:在每个所述字线区内形成字线栅沟槽,所述字线栅沟槽自所述第一面向所述第二面延伸,且所述字线栅沟槽沿所述第二方向贯穿所述有源区;在每个所述字线栅沟槽内形成两个电性隔离的字线栅结构。

7.如权利要求6所述存储器的形成方法,其特征在于,在形成所述字线栅结构之后,还包括:自所述第一面向所述第二面的方向刻蚀部分所述沟道区,在所述衬底内形成若干平行于所述第二方向的隔离开口;在所述隔离开口内形成隔离结构;在每个所述沟道区第一面内形成第一源漏掺杂区;在所述第一面上形成若干电容结构,每个所述电容结构与一个所述第一源漏掺杂区电连接;在每个所述沟道区第二面内形成第二源漏掺杂区。

8.如权利要求7所述存储器的形成方法,其特征在于,每个所述位线层与一个所述有源区中的若干所述第二源漏掺杂区电连接。

9.一种存储器,其特征在于,包括:

10.如权利要求9所述存储器,其特征在于,所述位线层的宽度尺寸小于所述有源区的宽度尺寸。

11.如权利要求9所述存储器,其特征在于,所述保护层的材料包括:氮化硅、氮化钛或氧化铝。

12.如权利要求9所述存储器,其特征在于,所述位线层包括:多晶硅层、位于所述多晶硅层上的金属硅化物层、以及位于所述金属硅化物层上的金属层。

13.如权利要求9所述存储器,其特征在于,每个所述有源区均包括若干字线区和若干沟道区,且每个所述有源区中的若干所述字线区和若干所述沟道区沿所述第一方向间隔排列。

14.如权利要求13所述存储器,其特征在于,还包括:位于每个所述字线区内的字线栅沟槽,所述字线栅沟槽自所述第一面向所述第二面延伸,且所述字线栅沟槽沿所述第二方向贯穿所述有源区;位于每个所述字线栅沟槽内的两个电性隔离的字线栅结构。

15.如权利要求14所述存储器,其特征在于,还包括:位于每个所述沟道区内的隔离开口;位于所述隔离开口内的隔离结构;位于每个所述沟道区第一面内的第一源漏掺杂区;位于所述第一面上的若干电容结构,每个所述电容结构与一个所述第一源漏掺杂区电连接;位于每个所述沟道区第二面内的第二源漏掺杂区。

16.如权利要求15所述存储器,其特征在于,每个所述位线层与一个所述有源区中的若干所述第二源漏掺杂区电连接。

技术总结

一种存储器及其形成方法,其中形成方法包括:提供衬底,衬底具有相对的第一面和第二面,衬底包括若干有源区;在第一面上形成第一隔离层;自第二面向第一面的方向对衬底进行减薄处理;自第二面向第一面的方向回刻蚀第一隔离层;在暴露出的有源区的侧壁表面形成保护层;在第二面上形成第二隔离层,第二隔离层覆盖保护层的侧壁;自第二面向第一面的方向回刻蚀有源区,在第二隔离层内形成位线开口;在位线开口内形成位线层;去除第二隔离层;在第二面上形成第三隔离层。通过保护层对位线层的侧壁进行保护,进而有效减少对位线层造成的横向刻蚀,防止位线层出现倒塌的问题。另外,保护层还能够有效防止位线层的侧壁氧化,进而提升器件结构的性能。

技术研发人员:张帜

受保护的技术使用者:芯盟科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!