嵌套式Δ-Σ模数转换系统及方法

本发明涉及的是一种信号处理领域的技术,具体是一种嵌套式δ-σ模数转换系统及方法。

背景技术:

1、现有缩放式δ-σ模数转换技术通过一个粗量化器预先量化模拟输入信号,使得模拟δ-σ环路只需要处理一小部分模拟信号,从而降低δ-σ环路的设计难度。然而,缩放式δ-σ模数转换器存在杂散泄露和粗-细量化电平失配问题,限制δ-σ模数转换器的精度,即:细量化δ-σ模数转换器的信号传递函数不等于1,最终输出结果受该函数影响而存在泄露问题,输出信号的频谱存在杂散,限制模数转换器的精度;粗量化与细量化模数转换器输出均通过数模转换器反馈至模数转换器的输入端,粗量化产生的最高有效位(msb)与细量化产生的最低有效位(lsb)电平上的失配会导致细量化δ-σ模数转换器内部信号摆幅增加,恶化模数转换器的性能。

技术实现思路

1、本发明针对现有技术存在的上述不足,提出一种嵌套式δ-σ模数转换系统及方法,通过嵌套式的外部的数模外部混合δ-σ环路动态调整内部模拟δ-σ环路的信号摆幅,从而可以降低内部模拟δ-σ环路的设计难度,显著提高能效与精度。

2、本发明是通过以下技术方案实现的:

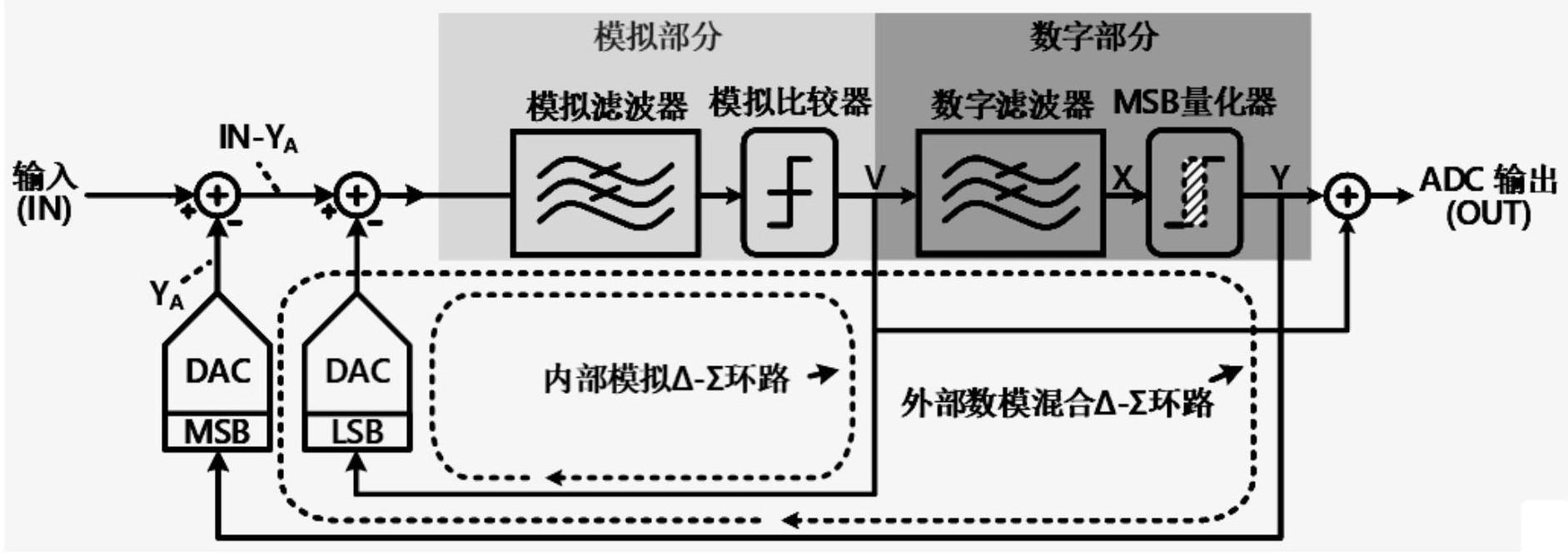

3、本发明涉及一种嵌套式δ-σ模数转换系统,包括:依次相连的模拟滤波器、模拟比较器与第一反馈数模转换器(dac)、设置于第一反馈数模转换器前的第二反馈数模转换器和设置于模拟比较器输出端的数字滤波器和msb量化器,其中:第一反馈数模转换器的输入端与模拟比较器的输出端相连,模拟滤波器、模拟比较器和第一反馈数模转换器构成内部模拟δ-σ环路,第二反馈数模转换器的输入端与msb量化器的输出端相连,第二反馈数模转换器的输出端与第一反馈数模转换器的输出端以及模拟滤波器的输入端相连,第二反馈数模转换器、内部模拟δ-σ环路、数字滤波器和msb量化器构成外部混合δ-σ环路。

4、技术效果

5、本发明通过嵌套架构显著降低模拟δ-σ环路内部的信号摆幅,提高模数转换器的能效;没有杂散泄露和电平失配问题,具备高精度的特点;除模拟δ-σ环路外,其它电路均为数字电路,具有高的数字电路亲和力与设计灵活度。

技术特征:

1.一种嵌套式δ-σ模数转换系统,其特征在于,包括:依次相连的模拟滤波器、模拟比较器与第一反馈数模转换器、设置于第一反馈数模转换器前的第二反馈数模转换器和设置于模拟比较器输出端的数字滤波器和msb量化器,其中:第一反馈数模转换器的输入端与模拟比较器的输出端相连,模拟滤波器、模拟比较器和第一反馈数模转换器构成内部模拟δ-σ环路,第二反馈数模转换器的输入端与msb量化器的输出端相连,第二反馈数模转换器的输出端与第一反馈数模转换器的输出端以及模拟滤波器的输入端相连,第二反馈数模转换器、内部模拟δ-σ环路、数字滤波器和msb量化器构成外部混合δ-σ环路。

2.根据权利要求1所述的嵌套式δ-σ模数转换系统,其特征是,所述的msb量化器包括:三态数字比较器与加减-累加器。

3.根据权利要求2所述的嵌套式δ-σ模数转换系统,其特征是,所述的三态数字比较器的工作状态包括:当三态数字比较器的输入d,大于比较阈值dh时,三态数字比较器输出+1;当三态数字比较器的输入d,小于比较阈值dl时,三态数字比较器输出-1;当三态数字比较器的输入d,介于dl和dh之间时,三态比较器不产生输出结果。

4.根据权利要求1所述的嵌套式δ-σ模数转换系统,其特征是,所述的内部模拟δ-σ环路对输入的差值in-ya量化后输出信号v=stf*(in-ya),其中stf为内部模拟δ-σ环路的信号传递函数;由于数字滤波器的高增益特点,数字滤波器的输入端,即内部模拟δ-σ环路的输出端为虚地端,内部模拟δ-σ环路的输出信号v仅有‘0’、‘1’两种状态的信号,当输出信号v偏离均值1/2时,msb量化器将检测到该偏差,具体为:当输出信号v的均值高于dh/低于dl时,msb量化器会增加/减小ya以减小/增加(in-ya),以迫使v的均值回到1/2;仅当输出信号v的均值变化足够大并超出(dl,dh)的范围时,才可能导致msb量化器的输出产生变化,其中:dh与dl分别为msb量化器的三态比较器的高、低阈值。

5.根据权利要求1或4所述的嵌套式δ-σ模数转换系统,其特征是,所述的外部混合δ-σ环路的输出信号其中:in为嵌套式δ-σ模数转换系统的输入,即外部混合δ-σ环路的输入模拟信号,v为内部模拟δ-σ环路的输出信号,lpfdig为数字滤波器的传递函数,ey为msb量化过程中的量化噪声,eq为内部模拟δ-σ环路的量化噪声,ntf为内部模拟δ-σ环路的噪声传递函数,stf为内部模拟δ-σ环路的信号传递函数。

6.根据权利要求5所述的嵌套式δ-σ模数转换系统,其特征是,所述的内部模拟δ-σ环路的量化噪声eq,在msb量化过程中,作为扰动信号打破msb量化过程中因精度低导致的信号相关特性,从而消除信号相关杂散,避免现有缩放型δ-σ模数转换技术中粗量化阶段的误差包含大量杂散泄露的问题。

7.一种基于权利要求1-6中任一所述模数转换系统的低延时msb量化方法,其特征在于,包括:

8.根据权利要求7所述的低延时msb量化方法,其特征是,所述的三态比较器,其阈值进一步通过以下方式进行优化,具体为:

技术总结

一种嵌套式Δ‑Σ模数转换系统及方法,包括:依次相连的模拟滤波器、模拟比较器与第一反馈数模转换器、设置于第一反馈数模转换器前的第二反馈数模转换器和设置于模拟比较器输出端的数字滤波器和MSB量化器,第一反馈数模转换器的输入端与模拟比较器的输出端相连,模拟滤波器、模拟比较器和第一反馈数模转换器构成内部模拟Δ‑Σ环路,第二反馈数模转换器的输入端与MSB量化器的输出端相连,第二反馈数模转换器的输出端与第一反馈数模转换器的输出端以及模拟滤波器的输入端相连,第二反馈数模转换器、内部模拟Δ‑Σ环路、数字滤波器和MSB量化器构成外部混合Δ‑Σ环路。本发明通过嵌套式的外部的数模外部混合Δ‑Σ环路动态调整内部模拟Δ‑Σ环路的信号摆幅,从而可以降低内部模拟Δ‑Σ环路的设计难度,显著提高能效与精度。

技术研发人员:过悦康,金晶,刘晓鸣,周健军

受保护的技术使用者:上海交通大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!