差分迟滞比较电路及方法

本公开涉及集成电路,尤其涉及一种差分迟滞比较电路及方法。

背景技术:

1、在信号产生、传输过程中,由于电源电压的噪声,以及环境噪声的干扰,会使信号出现噪声,噪声的存在影响了信号的准确性,会导致出现误码等问题。带有噪声的信号输入到比较器中时,尤其是当信号在比较器的阈值电压附近的噪声振幅较大的情况下,比较器的输出便会出现多次翻转,会带来误码,影响信号的准确性,虽然传统迟滞比较器可以在一定程度上降低误码率,但对差分信号的迟滞比较难以实现。

技术实现思路

1、鉴于上述问题,本发明提供了一种差分迟滞比较电路,以解决上述技术问题。

2、本公开的一个方面提供了一种差分迟滞比较电路,包括:差分输入电路,用于输入第一差分信号和第二差分信号;正反馈迟滞电路,与所述差分输入电路连接,用于比较所述第一差分信号和第二差分信号,得到差分比较结果,当所述差分比较结果大于第一阈值电压时,输出第一比较结果信号,当所述差分比较结果小于第二阈值电压时,输出第二比较信号,所述第一阈值电压大于第二阈值电压;输出级电路,与所述正反馈迟滞电路连接,用于将所述第一比较结果信号或所述第二比较结果信号转换为单端信号输出。

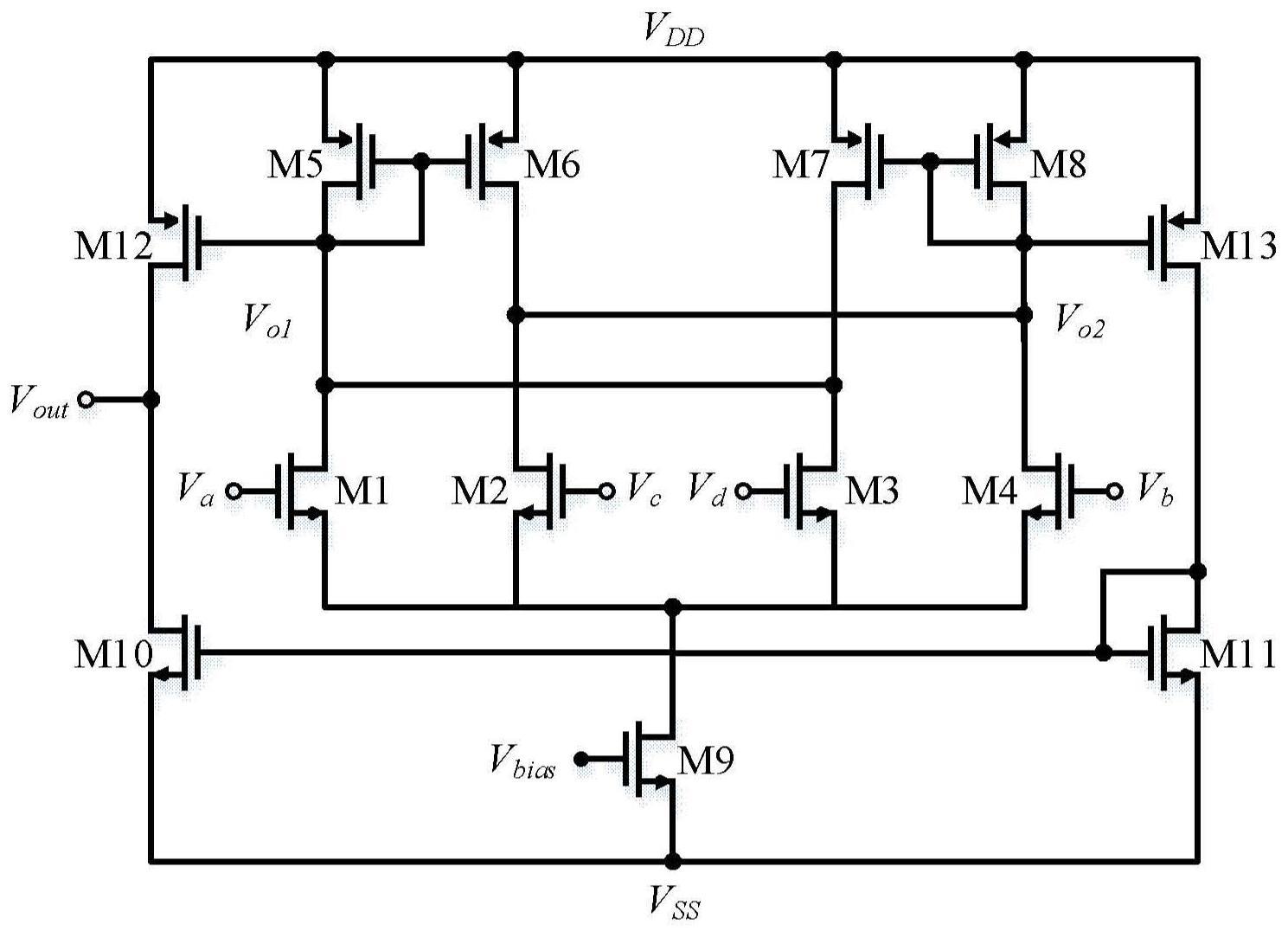

3、可选地,差分输入电路包括:第一差分输入电路,包括第一晶体管m1和第二晶体管m2,第一晶体管m1的栅极接入第一电压信号,所述第二晶体管m2的栅极接入第二电压信号,所述第一电压信号和所述第二电压信号构成第一差分信号;第二差分输入电路,包括第三晶体管m3和第四晶体管m4,第三晶体管m3的栅极接入第三电压信号,所述第四晶体管m4的栅极接入第四电压信号,所述第三电压信号和所述第四电压信号构成第二差分信号;所述第一晶体管m1、所述第二晶体管m2的漏极分别接入所述正反馈迟滞电路,向所述正反馈迟滞电路输入所述第一差分信号;所述第三晶体管m3和所述第四晶体管m4的漏极分别接入所述正反馈迟滞电路,向所述正反馈迟滞电路输入所述第二差分信号。

4、可选地,所述正反馈迟滞电路包括:第五晶体管m5,其栅极与漏极相连构成二极管连接,其漏极连接所述第一晶体管m1的漏极和所述第三晶体管m3的漏极;第六晶体管m6,其栅极与所述第五晶体管m5的栅极相连且连接第一输出端,其漏极连接所述第二晶体管m2的漏极和所述第四晶体管m4的漏极;第七晶体管m7,其栅极与第八晶体管m8的栅极相连且连接第二输出端,其漏极连接所述第三晶体管m3的漏极和所述第一晶体管m1的漏极;第八晶体管m8,其栅极与漏极相连构成二极管连接,其漏极连接所述第四晶体管m4的漏极和第二晶体管m2的漏极;第九晶体管m9,其漏极与所述第一晶体管m1、所述第二晶体管m2、所述第三晶体管m3和所述第四晶体管m4的源极连接,其源极接地,其栅极输入偏置电压vbias;所述第五晶体管m5、所述第六晶体管m6、所述第七晶体管m7和所述第八晶体管m8的源极输入工作电压vdd,所述第五晶体管m5与所述第七晶体管m7的漏极连接,所述第六晶体管m6和所述第八晶体管m8的漏极相连。

5、可选地,所述阈值电压vth的电压值为所述第一阈值电压或第二阈值电压;其中,当所述差分比较结果大于第一阈值电压时,所述阈值电压vth变为第二阈值电压;当所述差分比较结果小于第二阈值电压时,所述阈值电压变为第二阈值电压。

6、可选地,所述输出级电路包括:第十晶体管m10,其漏极连接单端输出端,其源极接地,其栅极与第十一晶体管m11的栅极连接;第十一晶体管m11,其的栅极与漏极相连构成二极管连接,其源极接地;第十二晶体管m12,其栅极连接所述第一输出端,其源极输入工作电压vdd,其漏极连接所述单端输出端;第十三晶体管m13,其栅极连接所述第二输出端,其源极输入工作电压vdd,其漏极连接所述第十一晶体管m11的漏极。

7、可选地,所述第一晶体管m1、所述第二晶体管m2、所述第三晶体管m3、所述第四晶体管m4、所述第九晶体管m9、所述第十晶体管m10和所述第十一晶体管m11为nmos管;所述第五晶体管m5、所述第六晶体管m6、所述第七晶体管m7、所述第八晶体管m8、所述第十二晶体管m12和所述第十三晶体管m13为pmos管。

8、本公开另一方面提供了一种差分迟滞比较方法,应用于如第一方面所述的差分迟滞比较电路,所述方法包括:利用差分输入电路输入第一差分信号和第二差分信号;利用正反馈迟滞电路比较所述第一差分信号和第二差分信号,得到差分比较结果,当所述差分比较结果大于第一阈值电压时,输出第一比较结果信号,当所述差分比较结果小于第二阈值电压时,输出第二比较信号,所述第一阈值电压大于第二阈值电压;利用输出级电路将所述第一比较结果信号或所述第二比较结果信号转换为单端信号输出。

9、可选地,包括:当所述差分比较结果大于第一阈值电压时,将所述正反馈迟滞电路的阈值电压vth变为第二阈值电压;当所述差分比较结果小于第二阈值电压时,将所述正反馈迟滞电路的阈值电压vth变为第一阈值电压。

10、可选地,所述第一阈值电压为:

11、

12、所述第二阈值电压为:

13、

14、其中,n=(w/l)6/(w/l)5=(w/l)8/(w/l)7,β=μ0cox(w/l)1,2,3,4,μ0cox为第一晶体管m1、第二晶体管m2、第三晶体管m3和第四晶体管m4的器件模型参数,w/l为第五晶体管m5、第六晶体管m6、第七晶体管m7和第八晶体管m8的器件宽长比,i9表示第九晶体管m9的电流。

15、在本公开实施例采用的上述至少一个技术方案能够达到以下有益效果:

16、本公开实施例提供了一种差分迟滞比较电路。通过差分输入电路做差可以减小输入信号中的共模噪声的影响,当迟滞比较电路的输入信号由低到高上升至大于第一阈值电压vt+时,迟滞比较电路的单端输出端输出为高电平,由于迟滞比较电路的第一阈值电压与第二阈值电压不同,即使输入信号在第一阈值电压附近的噪声振幅较大,只要未低于第二阈值电压,输出便不会发正翻转,保证信号的准确性。同理,当迟滞比较电路的输入信号由高到低下降至小于第一阈值电压vt-时,单端输出端输出为低电平,而且由于迟滞特性,保证信号的准确性,提高了电路的抗干扰能力。

技术特征:

1.一种差分迟滞比较电路,其特征在于,包括:

2.根据权利要求1所述的差分迟滞比较电路,其特征在于,差分输入电路包括:

3.根据权利要求2所述的差分迟滞比较电路,其特征在于,所述正反馈迟滞电路包括:

4.根据权利要求3所述的差分迟滞比较电路,其特征在于,所述阈值电压vth的电压值为所述第一阈值电压或第二阈值电压;

5.根据权利要求3所述的差分迟滞比较电路,其特征在于,所述输出级电路包括:

6.根据权利要求5所述的差分迟滞比较电路,其特征在于,所述第一晶体管m1、所述第二晶体管m2、所述第三晶体管m3、所述第四晶体管m4、所述第九晶体管m9、所述第十晶体管m10和所述第十一晶体管m11为nmos管;所述第五晶体管m5、所述第六晶体管m6、所述第七晶体管m7、所述第八晶体管m8、所述第十二晶体管m12和所述第十三晶体管m13为pmos管。

7.一种差分迟滞比较方法,应用于如权利要求1~6所述的差分迟滞比较电路,其特征在于,所述方法包括:

8.根据权利要求7所述的差分迟滞比较方法,其特征在于,包括:

9.根据权利要求7所述的差分迟滞比较方法,其特征在于,所述第一阈值电压为:

技术总结

本公开提供了一种差分迟滞比较电路及方法,该差分迟滞比较电路包括:差分输入电路,用于输入第一差分信号和第二差分信号;正反馈迟滞电路,与差分输入电路连接,用于比较第一差分信号和第二差分信号,得到差分比较结果,当差分比较结果大于第一阈值电压时,输出第一比较结果信号,当差分比较结果小于第二阈值电压时,输出第二比较信号,第一阈值电压大于第二阈值电压;输出级电路,与正反馈迟滞电路连接,用于将第一比较结果信号或第二比较结果信号转换为单端信号输出。

技术研发人员:李智,李成杰,赵慧冬,乔树山

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!