NAND闪存器件及其制备方法与流程

本发明涉及半导体,尤其涉及一种nand闪存器件及其制备方法。

背景技术:

1、nand闪存器件作为一种非易失性存储器,由于其大容量,擦写速度快,低成本等优点,适用于数据存储,广泛应用于消费、汽车、工业电子等领域。

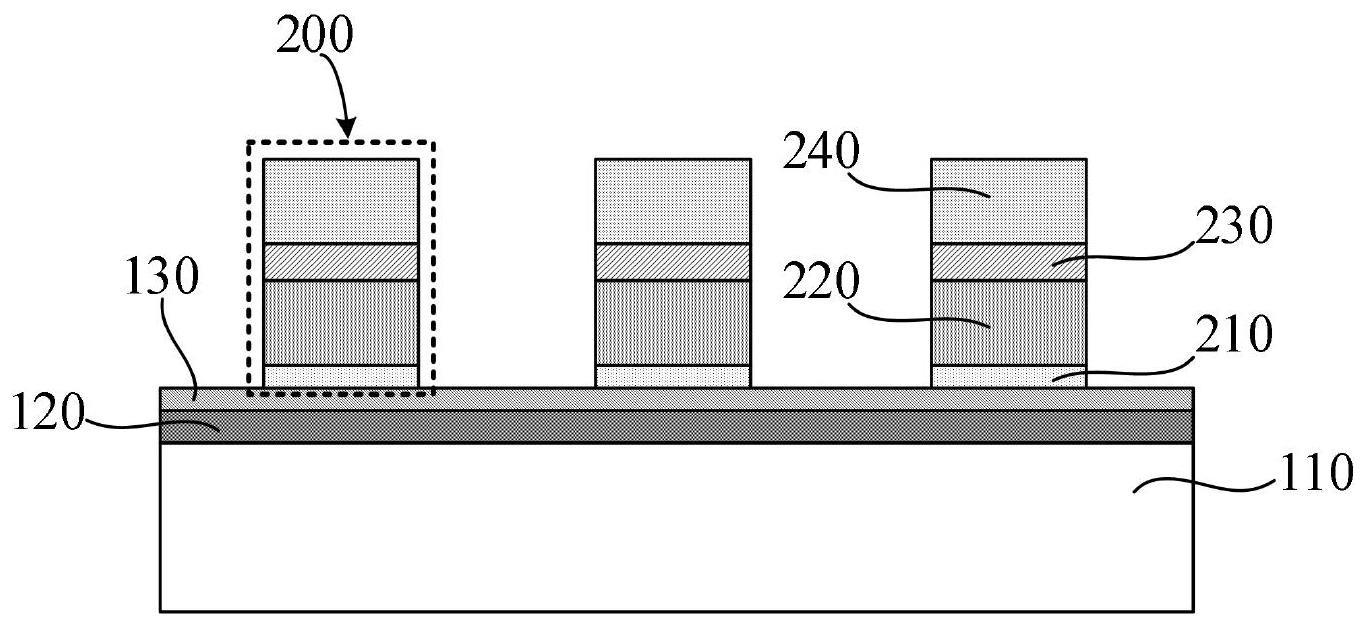

2、图1为一种nand闪存器件的剖面示意图。请参考图1,nand闪存器件包括衬底10和位于衬底10上的若干栅极结构20,其中栅极结构20包括由上至上依次堆叠的隧穿氧化层21、浮栅22、栅间介质层23及控制栅24,在栅极结构20两侧的衬底中分别形成源区和漏区(图中未示出)。nand闪存器件包括若干闪存单元,在nand闪存器件编程操作时,对部分的闪存单元进行编程时,要求不对另外的闪存单元产生编程影响,即要求对另外的闪存单元实现防止编程(program inhibit),提高防止编程的效果可以有效提升编程擦除窗口,改善nand闪存器件的可靠性。因此,需要提出一种能够提高防止编程的效果的nand闪存器件。

技术实现思路

1、本发明的目的在于提供一种nand闪存器件及其制备方法,提升编程擦除窗口,改善nand闪存器件的可靠性。

2、为了达到上述目的,本发明提供了一种nand闪存器件,包括:

3、绝缘体上半导体衬底,包括由下至上依次堆叠的第一半导体层、绝缘埋层及第二半导体层,所述第二半导体层的厚度小于或等于所述绝缘埋层的厚度;

4、若干栅极结构,位于所述绝缘体上半导体衬底上,所述栅极结构包括由下至上依次堆叠的隧穿氧化层、浮栅、栅间介质层及控制栅,其中所述nand闪存器件编程时,所述nand闪存器件处于全耗尽状态。

5、可选的,所述第二半导体层的厚度为100埃~300埃。

6、可选的,所述绝缘埋层的厚度为100埃~300埃。

7、可选的,所述绝缘埋层的材质包括氧化硅。

8、可选的,所述第二半导体层的材质包括硅。

9、可选的,所述隧穿氧化层的厚度为50埃~100埃。

10、可选的,所述浮栅的厚度为500埃~1500埃。

11、可选的,所述栅间介质层为ono叠层,所述栅间介质层的厚度为100埃~200埃。

12、可选的,所述控制栅的厚度为500埃~1500埃。

13、本发明还提供了一种nand闪存器件的制备方法,包括:

14、提供绝缘体上半导体衬底,所述绝缘体上半导体衬底包括由下至上依次堆叠的第一半导体层、绝缘埋层及第二半导体层,所述第二半导体层的厚度小于或等于所述绝缘埋层的厚度;

15、形成若干栅极结构,位于所述绝缘体上半导体衬底上,所述栅极结构包括由下至上依次堆叠的隧穿氧化层、浮栅、栅间介质层及控制栅,其中所述nand闪存器件编程时,所述nand闪存器件处于全耗尽状态。

16、在本发明提供的nand闪存器件及其制备方法中,绝缘体上半导体衬底包括由下至上依次堆叠的第一半导体层、绝缘埋层及第二半导体层,第二半导体层的厚度小于或等于绝缘埋层的厚度;若干栅极结构位于绝缘体上半导体衬底上,栅极结构包括由下至上依次堆叠的隧穿氧化层、浮栅、栅间介质层及控制栅,其中nand闪存器件编程时,nand闪存器件处于全耗尽状态。本发明中利用绝缘体上半导体衬底且第二半导体层的厚度小于或等于绝缘埋层的厚度,第二半导体层的厚度较薄,在nand闪存器件编程操作时,nand闪存器件处于全耗尽状态,此时nand闪存器件的沟道耗尽层电容接近于零,能够提高防止编程的效果,即有效提升编程擦除窗口,改善nand闪存器件的可靠性。

技术特征:

1.一种nand闪存器件,其特征在于,包括:

2.如权利要求1所述的nand闪存器件,其特征在于,所述第二半导体层的厚度为100埃~300埃。

3.如权利要求1或2所述的nand闪存器件,其特征在于,所述绝缘埋层的厚度为100埃~300埃。

4.如权利要求1所述的nand闪存器件,其特征在于,所述绝缘埋层的材质包括氧化硅。

5.如权利要求1所述的nand闪存器件,其特征在于,所述第二半导体层的材质包括硅。

6.如权利要求1所述的nand闪存器件,其特征在于,所述隧穿氧化层的厚度为50埃~100埃。

7.如权利要求1所述的nand闪存器件,其特征在于,所述浮栅的厚度为500埃~1500埃。

8.如权利要求1所述的nand闪存器件,其特征在于,所述栅间介质层为ono叠层,所述栅间介质层的厚度为100埃~200埃。

9.如权利要求1所述的nand闪存器件,其特征在于,所述控制栅的厚度为500埃~1500埃。

10.一种nand闪存器件的制备方法,其特征在于,包括:

技术总结

本发明提供了一种NAND闪存器件及其制备方法,包括:绝缘体上半导体衬底,包括由下至上依次堆叠的第一半导体层、绝缘埋层及第二半导体层,第二半导体层的厚度小于或等于绝缘埋层的厚度;若干栅极结构位于绝缘体上半导体衬底上,栅极结构包括由下至上依次堆叠的隧穿氧化层、浮栅、栅间介质层及控制栅,其中所述NAND闪存器件编程时,所述NAND闪存器件处于全耗尽状态。本发明中可以有效提升编程擦除窗口,改善NAND闪存器件的可靠性。

技术研发人员:姚邵康,王奇伟,陈昊瑜

受保护的技术使用者:上海华力微电子有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!