一种流水线逐次逼近型ADC的位权重检测和校准方法

本发明属于数模混合集成电路设计,尤其涉及一种流水线逐次逼近型adc的位权重检测和校准方法。

背景技术:

1、流水线逐次逼近型(pipelined-sar)adc通过级联多个中等分辨率的sar adc以流水线的方式进行工作,从而能够结合流水线型(pipelined)adc的高速高精度和sar adc的高能效优势。一方面,该架构克服了传统的pipelined adc中的flash 型adc成本随量化位数呈指数上升的缺点;另一方面,该架构采用多级中等分辨率的sar adc对采样信号进行多步的粗细量化,并结合pipelined adc的级间余量放大的方式将前级sar adc的余量信号放大后传递给第二级sar adc量化,从而提升了adc的整体精度。

2、由于pipelined-sar adc具备实现高速高精度以及高能效的潜力,因此成为了近年来国内外adc设计领域的研究热点。但是,pipelined-sar adc中电容失配和增益误差组成的位权重误差会限制其性能的进一步提升。对其进行校准是一种低成本的方案,然而传统的位权重校准窗口稳定性不好,容易受到工艺、电压和温度(process, voltage,temperature, pvt)的影响,校准电路复杂度也比较高。

技术实现思路

1、本发明针对现有技术中的不足,提供一种流水线逐次逼近型adc的位权重检测和校准方法。

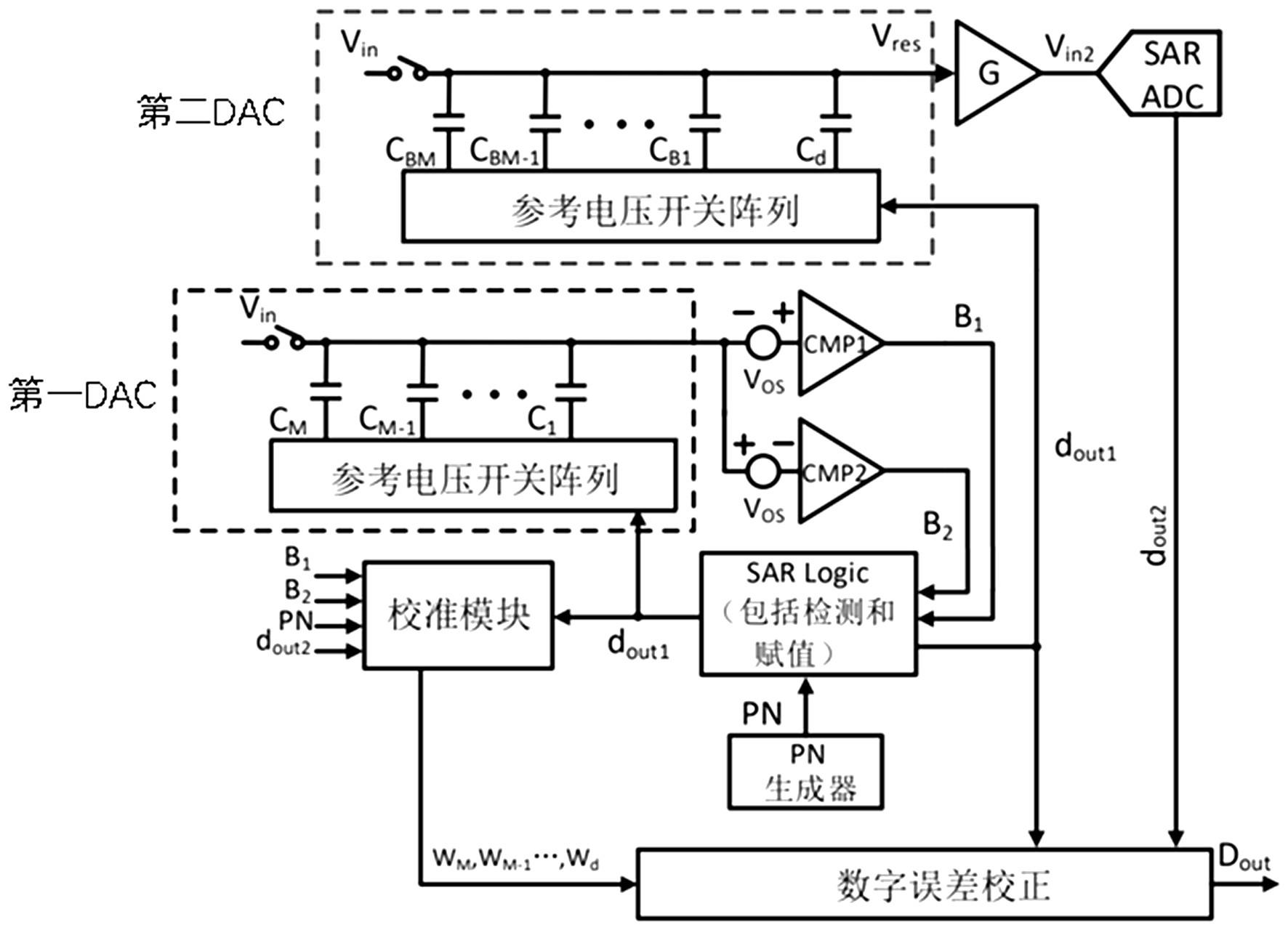

2、本发明提供一种流水线逐次逼近型adc的位权重检测和校准方法,包括:

3、双比较器的两个输出通过一个二选一的mux电路,选择最终输入到sar逻辑的值;当伪随机信号为高时,选择比较器cmp1的输出对应的sar逻辑的值输入到第一dac上;当伪随机信号为低时,选择比较器cmp2的输出对应的sar逻辑的值输入到第一dac上;

4、对两个比较器的移位寄存结果进行异或操作,判断比较器的输入是否落入失调电压建立的窗口以及落入窗口的位置;

5、在确定两个比较器结果相异的位置后,比较器停止工作,在sar逻辑中对当前位的结果强制赋值pn,当前位之后的各位的结果都强制赋值−pn,然后将统一强制赋值的结果一次性输入到第二dac上。

6、进一步地,所述第一dac的电容值小于第二dac的电容值。

7、进一步地,所述双比较器的输出结果的选择通过mux电路实现。

8、本发明提供一种流水线逐次逼近型adc的位权重检测和校准方法,通过对两个比较器输出的寄存结果进行异或,提高了检测窗口的稳定性;判断出两个比较器输出结果相异后,停止比较器工作,提高能效;通过统一强制赋值可以避免比较器后续比较结果出错的问题,且选择对移位寄存的值进行强制赋值,能够一步实现统一赋值的操作,然后一次性输入到第二dac,不会占用多余的相位,在电路上更容易实现。

技术特征:

1.一种流水线逐次逼近型adc的位权重检测和校准方法,其特征在于,包括:

2.根据权利要求1所述的流水线逐次逼近型adc的位权重检测和校准方法,其特征在于,所述第一dac的电容值小于第二dac的电容值。

3.根据权利要求1所述的流水线逐次逼近型adc的位权重检测和校准方法,其特征在于,所述双比较器的输出结果的选择通过mux电路实现。

技术总结

本发明提供一种流水线逐次逼近型ADC的位权重检测和校准方法,包括双比较器的两个输出通过一个二选一的MUX电路,选择最终输入到SAR逻辑的值;伪随机信号为高时,选择比较器CMP1的输出对应的SAR逻辑的值输入到第一DAC上;伪随机信号为低时,选择比较器CMP2的输出对应的SAR逻辑的值输入到第一DAC上;通过对两个比较器输出的寄存结果进行异或,提高检测窗口的稳定性;确定两个比较器输出结果相异后,停止比较器工作,提高能效;通过统一强制赋值,避免比较器后续比较结果出错,且选择对移位寄存的值进行强制赋值,一步实现统一赋值的操作,然后一次性输入到第二DAC,不占用多余的相位,在电路上更容易实现。

技术研发人员:孙杰,陈峥岩,刘伟,刘伟强

受保护的技术使用者:南京航空航天大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!