三维半导体存储器件及其制造方法与流程

各种示例实施例涉及一种三维半导体存储器件和/或其制造方法,并且更具体地,涉及一种三维铁电存储器件和/或其制造方法。

背景技术:

1、通常,半导体存储器件可以分为易失性存储器件和非易失性存储器件。易失性存储器件在电源被中断时丢失存储的数据,并且其示例包括动态随机存取存储器(dram)、静态ram(sram)等。非易失性存储器件即使在电源被中断时也不会丢失存储的数据,并且其示例包括可编程只读存储器(prom)、可擦除prom(eprom)、电eprom(eeprom)、闪存等。近来,根据半导体存储器件的高性能和/或低功率趋势,正在积极进行诸如磁随机存取存储器(mram)、相变随机存取存储器(pram)和铁电随机存取存储器(feram)之类的下一代半导体存储器件的开发。由于需要半导体器件的高集成度和高性能,因此正在进行使用具有不同特性的半导体器件的各种研究。

技术实现思路

1、各种示例实施例提供了一种具有改善的电特性的三维半导体存储器件。

2、备选地或附加地,各种示例实施例提供了一种制造具有改善的电特性的三维半导体存储器件的方法。

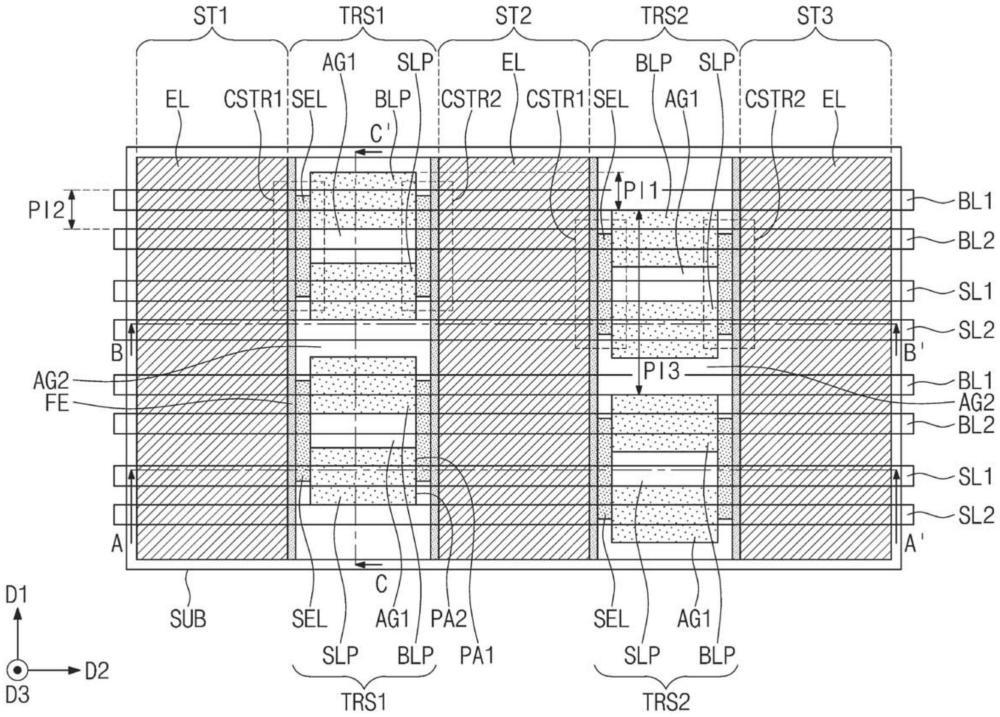

3、根据各种示例实施例的三维半导体存储器件可以包括:衬底上的第一贯通结构,第一贯通结构布置在第一方向上;电极,与第一贯通结构相邻,并且在第一方向上沿第一贯通水平地延伸;以及铁电层,介于电极和第一贯通结构之间。第一贯通结构中的每一个可以包括:第一导电柱和第二导电柱,在第一方向上彼此间隔开;以及沟道层,从第一导电柱的侧壁延伸到第二导电柱的侧壁,沟道层介于铁电层与第一导电柱和第二导电柱之间。第一导电柱和第二导电柱可以在第一方向上彼此间隔开,并且可以限定第一气隙。第一贯通结构中的相邻的第一贯通结构可以限定第二气隙。

4、根据一些示例实施例的三维半导体存储器件可以包括:衬底上的电极结构,电极结构包括彼此间隔开并且堆叠在衬底上的多个电极;第一导电柱,穿透电极结构;第二导电柱,穿透电极结构,第一导电柱和第二导电柱交替地布置在第一方向上,气隙分别介于彼此相邻的第一导电柱和第二导电柱之间;铁电层,介于第一导电柱和第二导电柱与电极结构之间;以及沟道层,介于第一导电柱和第二导电柱与铁电层之间。

5、根据一些示例实施例的三维半导体存储器件可以包括:衬底上的第一电极结构和第二电极结构,第一电极结构和第二电极结构中的每一个包括彼此间隔开并且堆叠在衬底上的多个电极,第一电极结构和第二电极结构在第一方向上延伸,并且第一电极结构和第二电极结构在与第一方向交叉的第二方向上彼此间隔开;贯通结构,在第一电极结构和第二电极结构之间;第一单元串,在第一电极结构和贯通结构之间;第二单元串,在第二电极结构和贯通结构之间;以及第一气隙,在第一单元串和第二单元串之间。贯通结构可以包括在第一方向上彼此间隔开的第一导电柱和第二导电柱,第一单元串和第二单元串中的每一个可以包括沟道层和铁电层,沟道层连接第一导电柱和第二导电柱,铁电层在沟道层与第一电极结构和第二电极结构中的与沟道层相邻的电极结构之间,并且第一气隙可以被第一单元串的沟道层、第二单元串的沟道层、第一导电柱和第二导电柱围绕。

技术特征:

1.一种三维半导体存储器件,包括:

2.根据权利要求1所述的三维半导体存储器件,还包括:

3.根据权利要求2所述的三维半导体存储器件,其中,所述第一封盖层的厚度和所述第二封盖层的厚度彼此不同。

4.根据权利要求1所述的三维半导体存储器件,其中,所述第一气隙在第二方向上的宽度与所述第二气隙在所述第二方向上的宽度彼此不同。

5.根据权利要求1所述的三维半导体存储器件,其中,所述沟道层包括半导体材料、非晶氧化物半导体、或二维材料中的至少一种。

6.根据权利要求1所述的三维半导体存储器件,其中,所述铁电层包括包含选自zr、si、al、y、gd、la、sc和sr中的至少一种杂质的hf基氧化物。

7.根据权利要求1所述的三维半导体存储器件,其中,

8.根据权利要求1所述的三维半导体存储器件,还包括:

9.根据权利要求1所述的三维半导体存储器件,还包括:

10.根据权利要求1所述的三维半导体存储器件,还包括:

11.一种三维半导体存储器件,包括:

12.根据权利要求11所述的三维半导体存储器件,

13.根据权利要求12所述的三维半导体存储器件,还包括:

14.根据权利要求13所述的三维半导体存储器件,其中,所述第一封盖层的最小厚度和所述第二封盖层的最小厚度彼此不同。

15.根据权利要求11所述的三维半导体存储器件,还包括:

16.一种三维半导体存储器件,包括:

17.根据权利要求16所述的三维半导体存储器件,其中,

18.根据权利要求17所述的三维半导体存储器件,还包括:

19.根据权利要求18所述的三维半导体存储器件,其中,所述第一封盖层的厚度和所述第二封盖层的厚度彼此不同。

20.根据权利要求16所述的三维半导体存储器件,还包括:

技术总结

一种三维半导体存储器件,包括:衬底上的第一贯通结构,第一贯通结构布置在第一方向上;电极,与第一贯通结构相邻,并且在第一方向上沿第一贯通结构水平地延伸;以及铁电层,介于电极和第一贯通结构之间。第一贯通结构中的每一个包括:第一导电柱和第二导电柱,在第一方向上彼此间隔开;以及沟道层,从第一导电柱的侧壁延伸到第二导电柱的侧壁,沟道层介于铁电层与第一导电柱和第二导电柱之间,第一导电柱和第二导电柱在第一方向上彼此间隔开并且限定第一气隙。第一贯通结构中的相邻的第一贯通结构限定第二气隙。

技术研发人员:李全一,李炅奂

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!