解决POR和LDO上电顺序的方法、电路、锁相环及芯片与流程

本发明涉及时钟芯片设计,尤其涉及一种解决por和ldo上电顺序的方法、电路、锁相环及芯片。

背景技术:

1、在时钟芯片设计中,正确可靠的上电时序决定芯片是否能正常的工作。这就需要por(power on reset)来进行上电复位,电源vdd上电初期产生一个复位信号(reset信号),初始化整个系统芯片,当vdd足够高时,por跟随电源电压输出,使各模块正常工作,当vdd下降至足够低时,por输出低即reset信号,复位整个芯片电路。

2、在数字模块需要用到ldo(低压差线性稳压器)的情形时,需要保证数字的ldo稳定后再输出por为高。这时无法确定是por先拉起还是ldo先稳定,通常可以用计数器计数来延迟por拉起,但延迟时间随vdd上电时间和pvt(process voltage temperature,工艺电压温度)的影响,往往无法给出准确的延迟时间。

技术实现思路

1、为了解决上述问题,本发明提出一种解决por和ldo上电顺序的方法、电路、锁相环及芯片,通过增加第一电阻作为上拉电阻使第二mos管保持初始关断状态,再通过低压差线性稳压器的输出信号控制第一mos管的栅极,使低压差线性稳压器输出稳定后上电复位电路再进行输出,从而确保正确的上电时序。

2、本发明采用的技术方案如下:

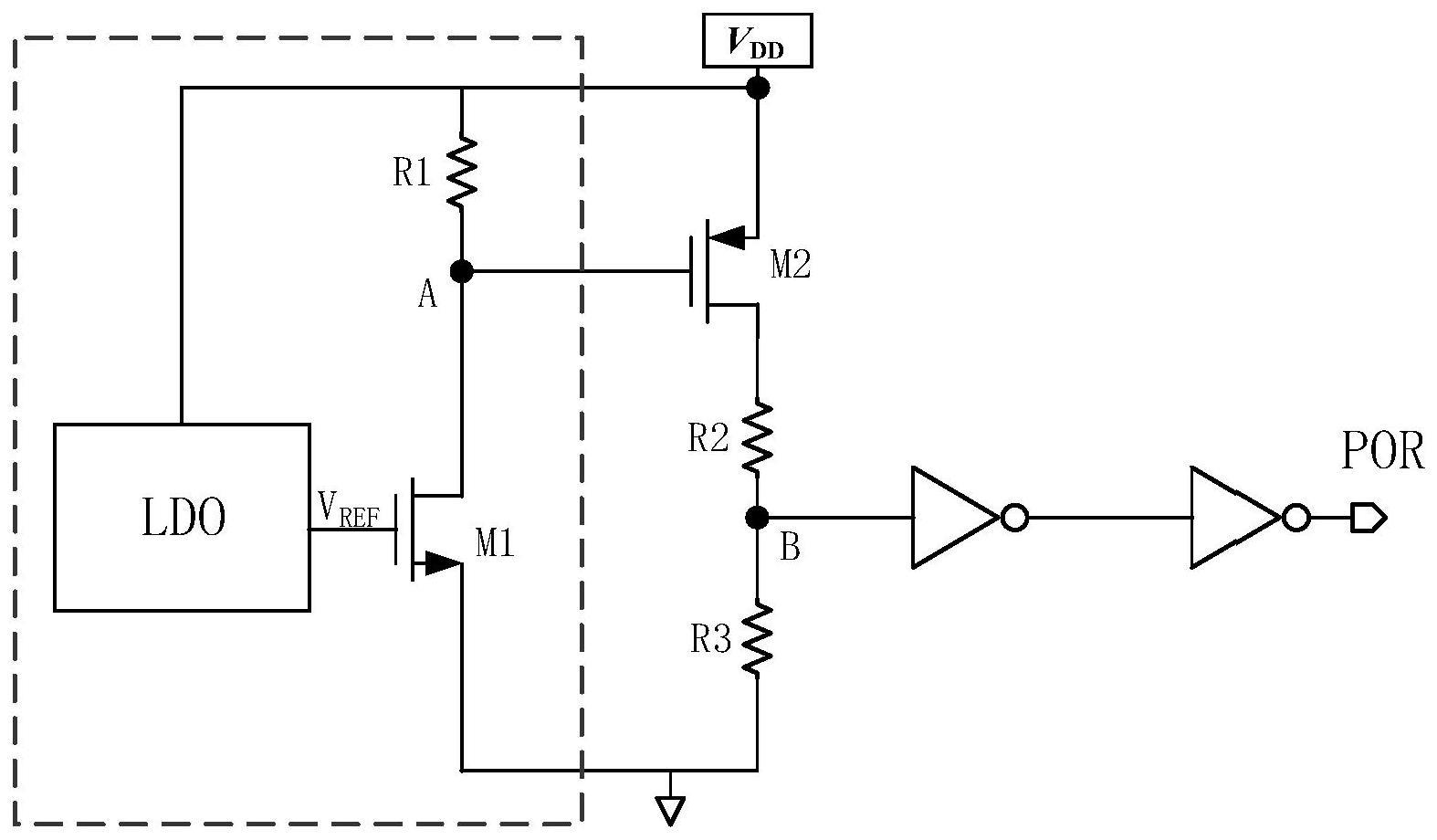

3、一种解决por和ldo上电顺序的电路,包括低压差线性稳压器、上电复位电路、反相器、第一mos管、第二mos管、第一电阻、第二电阻和第三电阻,所述低压差线性稳压器的信号输入端、第一电阻的第一端、第二mos管的源极接入工作电压vdd;所述第一mos管的栅极连接低压差线性稳压器的信号输出端,漏极连接第一电阻的第二端和第二mos管的栅极,源极接地;所述第二mos管的漏极连接第二电阻的第一端,所述第二电阻的第二端连接第三电阻的第一端和反相器的输入端,所述反相器的输出端连接上电复位电路,所述第三电阻的第二端接地;通过所述第一电阻作为上拉电阻使第二mos管保持初始关断状态,再通过所述低压差线性稳压器的输出信号控制第一mos管的栅极,使低压差线性稳压器输出稳定后上电复位电路再进行输出。

4、进一步地,通过调节第一电阻和第一mos管的尺寸使基准电压vref输出稳定后,第一mos管的下拉能力大于第一电阻的上拉能力,即第一mos管的导通电阻ron小于第一电阻,第二mos管开始导通,反相器、第一电阻和第二电阻的连接点电压开始上升,上升到反相器的阈值电压时,上电复位电路开始输出。

5、进一步地,所述第一mos管的导通电阻ron的计算方法包括:

6、

7、其中,l表示第一mos管的栅长,w表示第一mos管的栅宽,μn表示第一mos管的迁移率,cox表示单位面积栅氧化层电容,vgs表示第一mos管的栅源电压,vt表示第一mos管的阈值电压。

8、一种高性能锁相环,包括上述解决por和ldo上电顺序的电路。

9、一种时钟芯片,包括上述高性能锁相环。

10、一种解决por和ldo上电顺序的方法,包括以下步骤:

11、步骤s1.当工作电压vdd开始上电时,第一mos管的栅极处基准电压vref开始上升;第一mos管处于关断状态,将第一mos管的漏极、第二mos管的栅极和第一电阻第二端的连接点记为a点,则a点将被第一电阻上拉跟随工作电压vdd变化,此时第二mos管的栅源电压为零,处于关断状态,上电复位电路输出为0;

12、步骤s2.当基准电压vref上升到第一mos管的阈值电压vth后,第一mos管导通,a点开始下拉,第一mos管的导通电阻ron随基准电压vref上升而减小;

13、步骤s3.通过调节第一电阻和第一mos管的尺寸使基准电压vref输出稳定后,第一mos管的下拉能力大于第一电阻的上拉能力时,a点被下拉至0,第二mos管开始导通,反相器、第一电阻和第二电阻的连接点即b点的电压开始上升,上升到反相器的阈值电压时,上电复位电路的输出上拉至工作电压vdd。

14、进一步地,步骤s3中,第一mos管的下拉能力大于第一电阻的上拉能力时,第一mos管的导通电阻ron小于第一电阻。

15、进一步地,第一mos管的导通电阻ron的计算方法包括:

16、

17、其中,l表示第一mos管的栅长,w表示第一mos管的栅宽,μn表示第一mos管的迁移率,cox表示单位面积栅氧化层电容,vgs表示第一mos管的栅源电压,vt表示第一mos管的阈值电压。

18、一种高性能锁相环,基于上述解决por和ldo上电顺序的方法。

19、一种时钟芯片,包括上述高性能锁相环。

20、本发明的有益效果在于:

21、本发明通过增加第一电阻作为上拉电阻使第二mos管保持初始关断状态,再通过低压差线性稳压器的输出信号控制第一mos管的栅极,使低压差线性稳压器输出稳定后上电复位电路再进行输出,从而确保正确的上电时序。

技术特征:

1.一种解决por和ldo上电顺序的电路,其特征在于,包括低压差线性稳压器(ldo)、上电复位电路(por)、反相器、第一mos管(m1)、第二mos管(m2)、第一电阻(r1)、第二电阻(r2)和第三电阻(r3),所述低压差线性稳压器(ldo)的信号输入端、第一电阻(r1)的第一端、第二mos管(m2)的源极接入工作电压vdd;所述第一mos管(m1)的栅极连接低压差线性稳压器(ldo)的信号输出端,漏极连接第一电阻(r1)的第二端和第二mos管(m2)的栅极,源极接地;所述第二mos管(m2)的漏极连接第二电阻(r2)的第一端,所述第二电阻(r2)的第二端连接第三电阻(r3)的第一端和反相器的输入端,所述反相器的输出端连接上电复位电路(por),所述第三电阻(r3)的第二端接地;

2.根据权利要求1所述的解决por和ldo上电顺序的电路,其特征在于,通过调节第一电阻(r1)和第一mos管(m1)的尺寸使基准电压vref输出稳定后,第一mos管(m1)的下拉能力大于第一电阻(r1)的上拉能力,即第一mos管(m1)的导通电阻ron小于第一电阻(r1),第二mos管(m2)开始导通,反相器、第一电阻(r1)和第二电阻(r2)的连接点电压开始上升,上升到反相器的阈值电压时,上电复位电路(por)开始输出。

3.根据权利要求1所述的解决por和ldo上电顺序的电路,其特征在于,所述第一mos管(m1)的导通电阻ron的计算方法包括:

4.一种高性能锁相环,其特征在于,包括如权利要求1-3任一项所述的解决por和ldo上电顺序的电路。

5.一种时钟芯片,其特征在于,包括如权利要求4所述的高性能锁相环。

6.一种解决por和ldo上电顺序的方法,基于权利要求1所述的解决por和ldo上电顺序的电路,其特征在于,该方法包括以下步骤:

7.根据权利要求6所述的解决por和ldo上电顺序的方法,其特征在于,步骤s3中,第一mos管(m1)的下拉能力大于第一电阻(r1)的上拉能力时,第一mos管(m1)的导通电阻ron小于第一电阻(r1)。

8.根据权利要求6所述的解决por和ldo上电顺序的方法,其特征在于,第一mos管(m1)的导通电阻ron的计算方法包括:

9.一种高性能锁相环,其特征在于,基于权利要求6-8任一项所述的解决por和ldo上电顺序的方法。

10.一种时钟芯片,其特征在于,包括如权利要求9所述的高性能锁相环。

技术总结

本发明公开了一种解决POR和LDO上电顺序的方法、电路、锁相环及芯片,其中电路包括低压差线性稳压器、上电复位电路、反相器、第一MOS管、第二MOS管、第一电阻、第二电阻和第三电阻,低压差线性稳压器的信号输入端、第一电阻的第一端、第二MOS管的源极接入工作电压VDD;第一MOS管的栅极连接低压差线性稳压器的信号输出端,漏极连接第一电阻的第二端和第二MOS管的栅极,源极接地。本发明通过第一电阻作为上拉电阻使第二MOS管保持初始关断状态,再通过低压差线性稳压器的输出信号控制第一MOS管的栅极,使低压差线性稳压器输出稳定后上电复位电路再进行输出,从而确保正确的上电时序。

技术研发人员:郭涛

受保护的技术使用者:成都电科星拓科技有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!