一种差分输入ADC的静态性能测试装置及方法与流程

本发明涉及一种adc测试,具体为一种差分输入adc的静态性能测试装置及方法。

背景技术:

1、随着adc(模拟数字转换器)应用越来越多,对于adc性能指标要求也越来越高,因此应运而生了各种测试方案以及装备,adc的性能指标可以说整个soc(片上系统)芯片最核心、最关键性的指标之一,影响到整个装置的性能,这使得adc性能测试变得尤为重要和关键,adc的技术指标主要分为静态指标和动态指标。

2、传统的adc静态参数的测量,可以提供台阶波,如果对于单电源以及单端输入的adc而言,提供信号比较方便;但是对于差分输入的adc并且对输入共模电压有要求的adc而言,提供可变的台阶波信号,需要大量人工参与且效率极低,并且需要使用一些高精度的仪器设备。

3、现有技术已经不能满足现阶段人们的需求,基于现状,急需对现有技术进行改进。

技术实现思路

1、本发明的目的在于提供一种差分输入adc的静态性能测试装置,以解决上述背景技术中提出的问题。

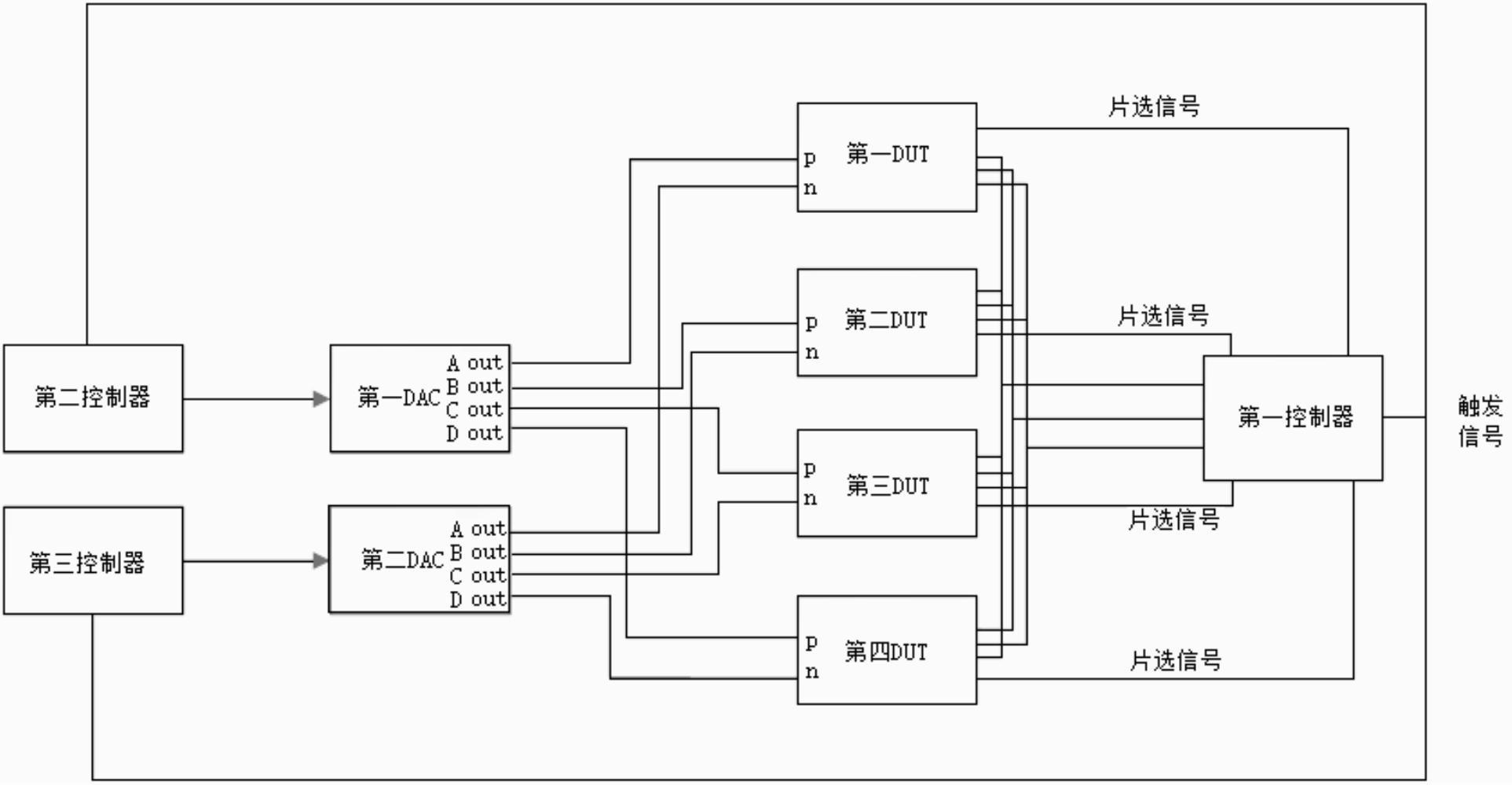

2、一方面,本发明提供如下技术方案一种差分输入adc的静态性能测试装置,包括:主控模块、信号产生模块、待测模块和pc(电脑)端;其中,所述主控模块包括:第一控制器、第二控制器和第三控制器。

3、所述信号产生模块包括:第一dac(数字模拟转换器)、第二dac。

4、所述待测模块包括:第一dut(待测芯片)、第二dut、第三dut和第四dut,且每个dut内部均集成有adc。

5、所述第一dac、第二dac的输出端均同步产生多路阶梯波,且所述第一dac、第二dac单独同步产生的多路阶梯波完全相同,但是,第一dac产生的阶梯波与第二dac产生的阶梯波互相不同,其中,第一dac的其中任意一路阶梯波与第二dac的其中任意一路阶梯波共同组成一组差分信号,并加载到dut内部集成的adc的差分信号采集输入端,且第一dac与第二dac能够实现同时测量被测dut的数量为n种;其中,n表示第一dac与第二dac输出端的数量。

6、所述第一dut、第二dut、第三dut和第四dut均具有3路控制输出端和1路片选信号输出端,且第一dut、第二dut、第三dut和第四dut的3路控制输出端均加载到第一控制器的控制输入端,且第一dut、第二dut、第三dut和第四dut的1路片选信号输出端分别输出的4路片选信号均通过同步测试接口加载到第一控制器的片选控制端;第一控制器通过同步测试接口片选第一dut、第二dut、第三dut和第四dut,来控制不同dut通信,去配置回读dut内部的adc的数据,同步采集第一dac和第二dac的输出信号,得到采样信号。

7、所述第一控制器的输出端输出同步触发信号分别加载到第二控制器和第三控制器的控制端,且所述第二控制器的输出端产生控制信号加载到第一dac的控制端,且所述第三控制器的输出端产生控制信号加载到第二dac的控制端。

8、所述第一控制器分别通过多个uart(异步收发传输器)接口并联连接到上位机pc端,第一控制器通过dma(直接内存访问)方式将数据从存储区域搬运至uart接口,并转发至pc端,可高效并行传输多路数据。

9、另一方面,本发明还提供如下技术方案一种差分输入adc的静态性能测试方法,步骤包括:

10、步骤s1:第一控制器通过同步测试接口对第一dut、第二dut、第三dut和第四dut内部的adc进行初始化的配置。

11、步骤s2:第一控制器通过触发信号去控制第二控制器和第三控制器产生中断信号标志,第二控制器和第三控制器响应该中断信号后同时向第一dac和第二dac发送信号产生的指令,发送结束后第二控制器和第三控制器回馈给第一控制器,此时第一控制器通过片选信号选择不同的dut对象,回读dut内的adc code(编码)值,回读后第一控制器将其存储在对应的存储区域,同时将数据回传到上位机pc端。

12、步骤s3:循环重复上述步骤,第二控制器和第三控制器会根据每次步骤控制第一dac、第二dac产生阶梯波信号,由于,第一dac、第二dac同步产生的阶梯波的电压值为-vref~+vref范围的输入信号,所以最终差分输入信号采用-vref~+vref的阶梯波,得到一组数据,最终做数据处理计算inl和dnl等静态参数。

13、本发明具有如下有益效果:

14、本发明可同时测量多个dut,也可同时测一个dut的多个通道,并且无须cpu参与和人工干预即可通过模拟测试对dut进行有效控制,可根据测试需求更换dut的目标板测试;灵活,方便快捷配置不同的采样率,快速测量adc模块的静态指标;还可以自校正adc,并且同时测量vref的温度系数。

技术特征:

1.一种差分输入adc的静态性能测试装置,其特征在于,包括:主控模块、信号产生模块、待测模块和pc端;其中,

2.根据权利要求1所述的差分输入adc的静态性能测试装置,其特征在于:所述第一dac、第二dac的输出端同步产生的阶梯波的数量相同。

3.根据权利要求1所述的差分输入adc的静态性能测试装置,其特征在于:所述第一dac与第二dac同时测量被测dut的数量为n种;其中,所述n表示第一dac、第二dac输出端的数量。

4.根据权利要求1所述的差分输入adc的静态性能测试装置,其特征在于:

5.根据权利要求1所述的差分输入adc的静态性能测试装置,其特征在于:所述第二控制器和第三控制器同时触发中断,且同步产生控制信号,并通过所述控制信号分别控制第一dac和和第二dac。

6.根据权利要求1所述的差分输入adc的静态性能测试装置,其特征在于:所述第一控制器通过dma方式将数据从存储区域搬运至uart接口,并转发至pc端,并行传输多路数据。

7.根据权利要求1所述的差分输入adc的静态性能测试装置,其特征在于:

8.根据权利要求7所述的差分输入adc的静态性能测试装置,其特征在于:

9.一种基于权利要求1-8任意一项权利要求所述装置的差分输入adc的静态性能测试方法,其特征在于,步骤包括:

10.根据权利要求9所述的差分输入adc的静态性能测试方法,其特征在于:在执行步骤s2和s3时,要先向第一dac和第二dac发送信号产生的指令,再模拟测试去触发dut中的adc连续采样8次并回读8次数据,做数据处理后,再触发下次dac输出下一个阶梯波信号,重复循环,最终得到-vref~+vref差分输入信号时的adc采样编码。

技术总结

本发明公开了一种差分输入ADC的静态性能测试装置及方法,包括:主控模块、信号产生模块和待测模块;其中主控模块包括第一控制器、第二控制器和第三控制器;信号产生模块包括第一DAC、第二DAC;待测模块包括第一DUT、第二DUT、第三DUT和第四DUT,且每个DUT内部均集成有ADC;第一和第二DAC的输出端均同步产生多路阶梯波,且第一和第二DAC单独同步产生的多路阶梯波完全相同,但是第一DAC产生的阶梯波与第二DAC产生的阶梯波互相不同。本发明可同时测量多个DUT,也可同时测一个DUT的多个通道,且无须CPU参与和人工干预即可通过模拟测试对DUT进行有效控制,可根据测试需求更换DUT的目标板测试。

技术研发人员:徐晨曦,潘明方,熊海峰

受保护的技术使用者:上海泰矽微电子有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!