低电压差分信号驱动电路及具有该驱动电路的芯片的制作方法

本申请涉及集成电路,特别涉及一种低电压差分信号驱动电路及具有该驱动电路的芯片。

背景技术:

1、lvds(low voltage differential signaling,低电压差分信号)采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点。

2、在lvds驱动电路工作时,pvt(process voltage temperature)的变化很容易导致在信号传输过程中共模电平的偏移和波动,这就很难保证达到lvds国际标准的要求。现有技术中,一般是通过加入共模反馈电路来稳定lvds驱动电路输出的共模电平,但共模反馈电路环路稳定性不高,导致lvds驱动电路在传输高速率的信号时,共模电平依然会具有一定的偏差,从而导致lvds驱动电路输出信号完整性较差。

技术实现思路

1、为了解决上述问题,本申请提供了一种低电压差分信号驱动电路及具有该低电压差分信号驱动电路的芯片。

2、根据本申请实施例的一方面,公开了一种低电压差分信号驱动电路,所述低电压差分信号驱动电路包括:

3、主体驱动电路,用于输出差分信号;

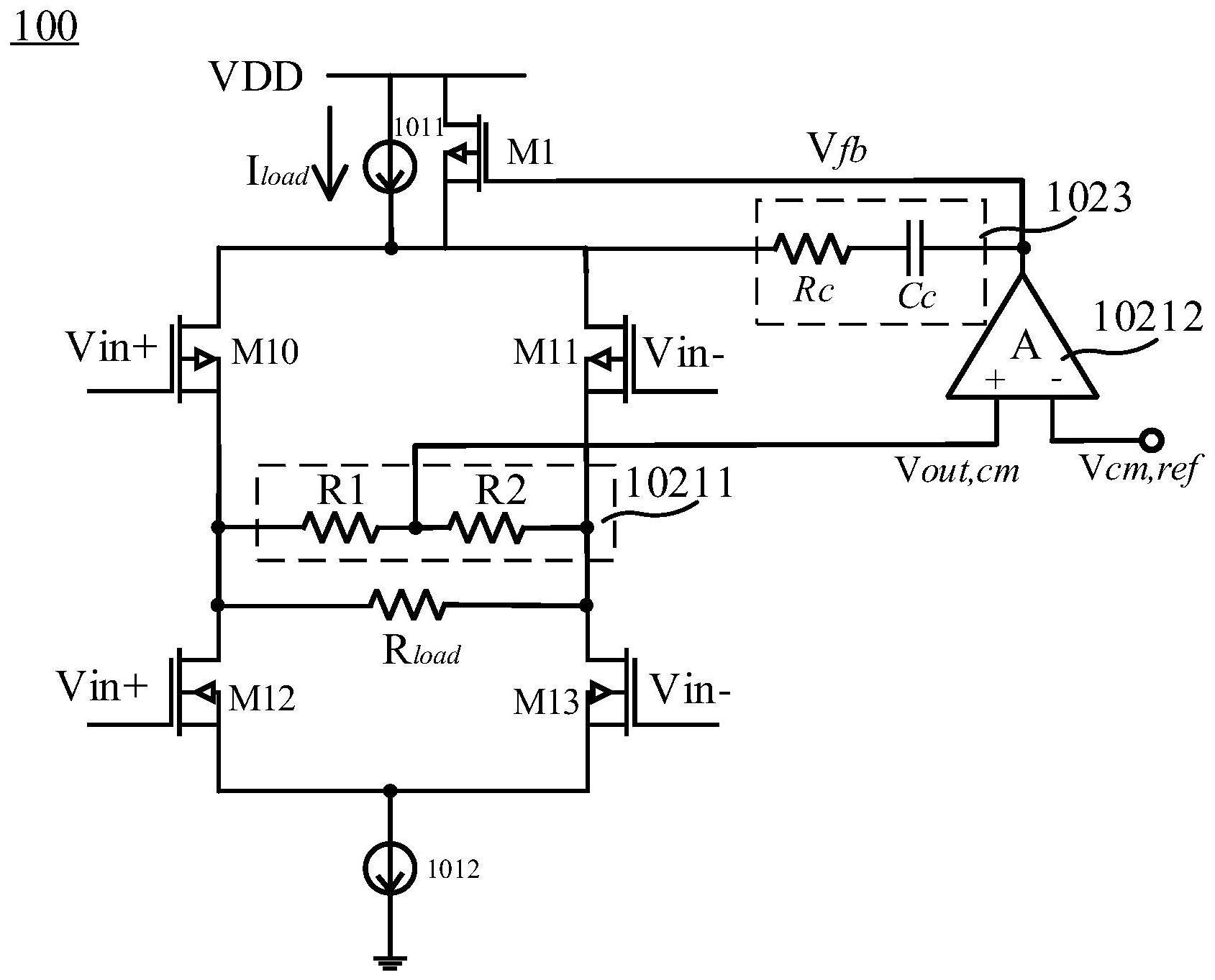

4、共模反馈电路,包括第一反馈放大电路和第二反馈放大电路,所述第一反馈放大电路连接所述主体驱动电路的输出端,用于检测所述主体驱动电路输出的差分信号的共模电压,并放大所述共模电压与基准电压的电压差值后输出,所述第二反馈放大电路的输入端连接所述第一反馈放大电路的输出端,以接收并放大经所述第一反馈放大电路放大后的电压差值,所述第二反馈放大电路的输出端连接所述主体驱动电路的电源端,以调整所述主体驱动电路输出的差分信号的共模电压。

5、在一种示例性实施例中,所述第二反馈放大电路包括第一晶体管,所述第一晶体管具有控制端、第一端以及第二端,所述第一晶体管的控制端作为所述第二反馈放大电路的输入端,所述第一晶体管的第一端作为所述第二反馈放大电路的输出端,所述第一晶体管的第二端连接电压源。

6、在一种示例性实施例中,所述主体驱动电路的输出端包括两个差分输出端,所述第一反馈放大电路包括:

7、电压检测电路,连接在所述主体驱动电路的两个差分输出端之间,用于检测所述主体驱动电路输出的差分信号的共模电压;

8、比较放大器,具有第一输入端、第二输入端以及输出端,所述比较放大器的第一输入端连接所述电压检测电路,以接收所述共模电压,所述比较放大器的第二输入端用于接收基准电压,所述比较放大器的输出端连接所述第一晶体管的控制端。

9、在一种示例性实施例中,所述电压检测电路包括第一分压电阻和第二分压电阻,所述第一分压电阻的一端连接所述主体驱动电路的其中一差分输出端,所述第一分压电阻的另一端连接所述第二分压电阻的一端,所述第二分压电阻的另一端连接所述主体驱动电路的另一差分输出端,所述比较放大器的第一输入端连接所述第一分压电阻与所述第二分压电阻的相接节点。

10、在一种示例性实施例中,所述比较放大器包括第二晶体管、第三晶体管、第四晶体管、第五晶体管以及第六晶体管,所述第二晶体管的控制端作为所述比较放大器的第一输入端,所述第二晶体管的第二端与所述第四晶体管的第一端连接,所述第三晶体管的控制端作为所述比较放大器的第二输入端,所述第三晶体管的第二端与所述第五晶体管的第一端连接,且所述第三晶体管的第二端与所述第五晶体管的第一端的连接节点作为所述比较放大器的输出端,所述第四晶体管的控制端连接所述第五晶体管的控制端,且所述第四晶体管的控制端与所述第五晶体管的控制端的连接节点和所述第二晶体管的第二端与所述第四晶体管的第一端的连接节点连接,所述第四晶体管的第二端和所述第五晶体管的第二端连接所述电压源,所述第六晶体管的第二端连接所述第二晶体管和所述第三晶体管的第一端,所述第六晶体管作为尾电流源。

11、在一种示例性实施例中,所述主体驱动电路的输出端包括两个差分输出端,所述第一反馈放大电路包括第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管、第八晶体管、第九晶体管,所述第二晶体管和所述第三晶体管的控制端作为所述第一反馈放大电路的一输入端,所述第二晶体管和所述第三晶体管的第二端连接所述第六晶体管的第二端,所述第四晶体管和所述第五晶体管的控制端作为所述第一反馈放大电路的另一输入端,所述第四晶体管和所述第五晶体管的第二端连接所述第七晶体管的第二端,所述第二晶体管和所述第三晶体管的第二端与所述第六晶体管的第二端的连接节点以及所述第四晶体管和所述第五晶体管的第二端与所述第七晶体管的第二端的连接节点作为所述第一反馈放大电路的输出端,所述第六晶体管的控制端与第二端连接,所述第七晶体管的控制端与第二端连接,所述第六晶体管和所述第七晶体管的第一端连接所述电压源,所述第八晶体管的第二端连接所述第二晶体管和所述第四晶体管的第一端,所述第九晶体管的第二端连接所述第三晶体管和所述第五晶体管的第一端,所述第八晶体管和所述第九晶体管作为尾电流源。

12、在一种示例性实施例中,所述共模反馈电路还包括密勒补偿电路,所述密勒补偿电路连接在所述第一反馈放大电路的输出端与所述电源端之间。

13、在一种示例性实施例中,所述密勒补偿电路包括密勒补偿电容和调零电阻,所述密勒补偿电容的一端连接在所述第一反馈放大电路的输出端,所述密勒补偿电容的另一端连接所述调零电阻的一端,所述调零电阻的另一端连接所述电源端。

14、在一种示例性实施例中,所述低电压差分信号驱动电路还包括电压源,所述电压源能够提供1.8v电压输出,以导通所述主体驱动电路和所述共模反馈电路中的各个晶体管。

15、根据本申请实施例的一方面,公开了一种芯片,所述芯片包括前述的低电压差分信号驱动电路。

16、本申请的实施例提供的技术方案至少包括以下有益效果:

17、本申请公开的低电压差分信号驱动电路,其共模反馈电路包括第一反馈放大电路和第二反馈放大电路,第一反馈放大电路连接主体驱动电路的输出端,第二反馈放大电路的输入端连接第一反馈放大电路的输出端,第二反馈放大电路的输出端连接主体驱动电路的电源端,通过第一反馈放大电路检测主体驱动电路输出的差分信号的共模电压,并将共模电压与基准电压比较,获得共模电压与基准电压的电压差值并将该电压差值进行放大后输出,再通过第二反馈放大电路放大经第一反馈放大电路放大后的电压差值,基于最终获得的电压差值调整输入主体驱动电路的电源大小,从而调整主体驱动电路输出的差分信号的共模电压。本申请采用两级反馈放大电路,整个共模反馈电路的环路增益较高,提高了共模反馈电路的稳定性,使得整个低电压差分信号驱动电路在传输高速率信号时,输出波形不会出现大幅度的偏移,从而提高输出信号的准确性。

18、应当理解的是,以上的一般描述和后文的细节描述仅是示例性的,并不能限制本申请。

技术特征:

1.一种低电压差分信号驱动电路,其特征在于,包括:

2.根据权利要求1所述的低电压差分信号驱动电路,其特征在于,所述第二反馈放大电路包括第一晶体管,所述第一晶体管具有控制端、第一端以及第二端,所述第一晶体管的控制端作为所述第二反馈放大电路的输入端,所述第一晶体管的第一端作为所述第二反馈放大电路的输出端,所述第一晶体管的第二端连接电压源。

3.根据权利要求2所述的低电压差分信号驱动电路,其特征在于,所述主体驱动电路的输出端包括两个差分输出端,所述第一反馈放大电路包括:

4.根据权利要求3所述的低电压差分信号驱动电路,其特征在于,所述电压检测电路包括第一分压电阻和第二分压电阻,所述第一分压电阻的一端连接所述主体驱动电路的其中一差分输出端,所述第一分压电阻的另一端连接所述第二分压电阻的一端,所述第二分压电阻的另一端连接所述主体驱动电路的另一差分输出端,所述比较放大器的第一输入端连接所述第一分压电阻与所述第二分压电阻的相接节点。

5.根据权利要求3所述的低电压差分信号驱动电路,其特征在于,所述比较放大器包括第二晶体管、第三晶体管、第四晶体管、第五晶体管以及第六晶体管,所述第二晶体管的控制端作为所述比较放大器的第一输入端,所述第二晶体管的第二端与所述第四晶体管的第一端连接,所述第三晶体管的控制端作为所述比较放大器的第二输入端,所述第三晶体管的第二端与所述第五晶体管的第一端连接,且所述第三晶体管的第二端与所述第五晶体管的第一端的连接节点作为所述比较放大器的输出端,所述第四晶体管的控制端连接所述第五晶体管的控制端,且所述第四晶体管的控制端与所述第五晶体管的控制端的连接节点和所述第二晶体管的第二端与所述第四晶体管的第一端的连接节点连接,所述第四晶体管的第二端和所述第五晶体管的第二端连接所述电压源,所述第六晶体管的第二端连接所述第二晶体管和所述第三晶体管的第一端,所述第六晶体管作为尾电流源。

6.根据权利要求2所述的低电压差分信号驱动电路,其特征在于,所述主体驱动电路的输出端包括两个差分输出端,所述第一反馈放大电路包括第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管、第八晶体管、第九晶体管,所述第二晶体管和所述第三晶体管的控制端作为所述第一反馈放大电路的一输入端,所述第二晶体管和所述第三晶体管的第二端连接所述第六晶体管的第二端,所述第四晶体管和所述第五晶体管的控制端作为所述第一反馈放大电路的另一输入端,所述第四晶体管和所述第五晶体管的第二端连接所述第七晶体管的第二端,所述第二晶体管和所述第三晶体管的第二端与所述第六晶体管的第二端的连接节点以及所述第四晶体管和所述第五晶体管的第二端与所述第七晶体管的第二端的连接节点作为所述第一反馈放大电路的输出端,所述第六晶体管的控制端与第二端连接,所述第七晶体管的控制端与第二端连接,所述第六晶体管和所述第七晶体管的第一端连接所述电压源,所述第八晶体管的第二端连接所述第二晶体管和所述第四晶体管的第一端,所述第九晶体管的第二端连接所述第三晶体管和所述第五晶体管的第一端,所述第八晶体管和所述第九晶体管作为尾电流源。

7.根据权利要求1至6任一项所述的低电压差分信号驱动电路,其特征在于,所述共模反馈电路还包括密勒补偿电路,所述密勒补偿电路连接在所述第一反馈放大电路的输出端与所述电源端之间。

8.根据权利要求7所述的低电压差分信号驱动电路,其特征在于,所述密勒补偿电路包括密勒补偿电容和调零电阻,所述密勒补偿电容的一端连接在所述第一反馈放大电路的输出端,所述密勒补偿电容的另一端连接所述调零电阻的一端,所述调零电阻的另一端连接所述电源端。

9.根据权利要求2所述的低电压差分信号驱动电路,其特征在于,还包括电压源,所述电压源能够提供1.8v电压输出,以导通所述主体驱动电路和所述共模反馈电路中的各个晶体管。

10.一种芯片,其特征在于,所述芯片包括如权利要求1至8任一项所述的低电压差分信号驱动电路。

技术总结

本申请揭示一种低电压差分信号驱动电路及具有该驱动电路的芯片,该方案的共模反馈电路包括第一反馈放大电路和第二反馈放大电路,第一反馈放大电路连接主体驱动电路的输出端,第二反馈放大电路的输入端连接第一反馈放大电路的输出端,第二反馈放大电路的输出端连接主体驱动电路的电源端,通过第一反馈放大电路检测并放大共模电压与基准电压的电压差值后输出,再通过第二反馈放大电路进一步放大电压差值,最终基于电压差值调整输入主体驱动电路的电源大小,从而共模电压。共模反馈电路的环路增益高,提高了共模反馈电路的稳定性,使得整个低电压差分信号驱动电路在传输高速率信号时,输出波形不会出现大幅度的偏移,从而提高输出信号的准确性。

技术研发人员:白丽霞

受保护的技术使用者:牛芯半导体(深圳)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!