存储器的制备方法及存储器与流程

本公开涉及半导体制备,尤其涉及一种存储器的制备方法及存储器。

背景技术:

1、随着半导体技术的不断成熟,对存储器的高密度以及大容量的要求越来越高,目前可将平面的存储器单元转换为三维存储器架构,以进一步提高存储器的密度,增大存储容量。然而,目前三维存储器的制备工艺比较局限。

2、在所述背景技术部分公开的上述信息仅用于加强对本公开的背景的理解,因此它可以包括不构成对本领域普通技术人员已知的相关技术的信息。

技术实现思路

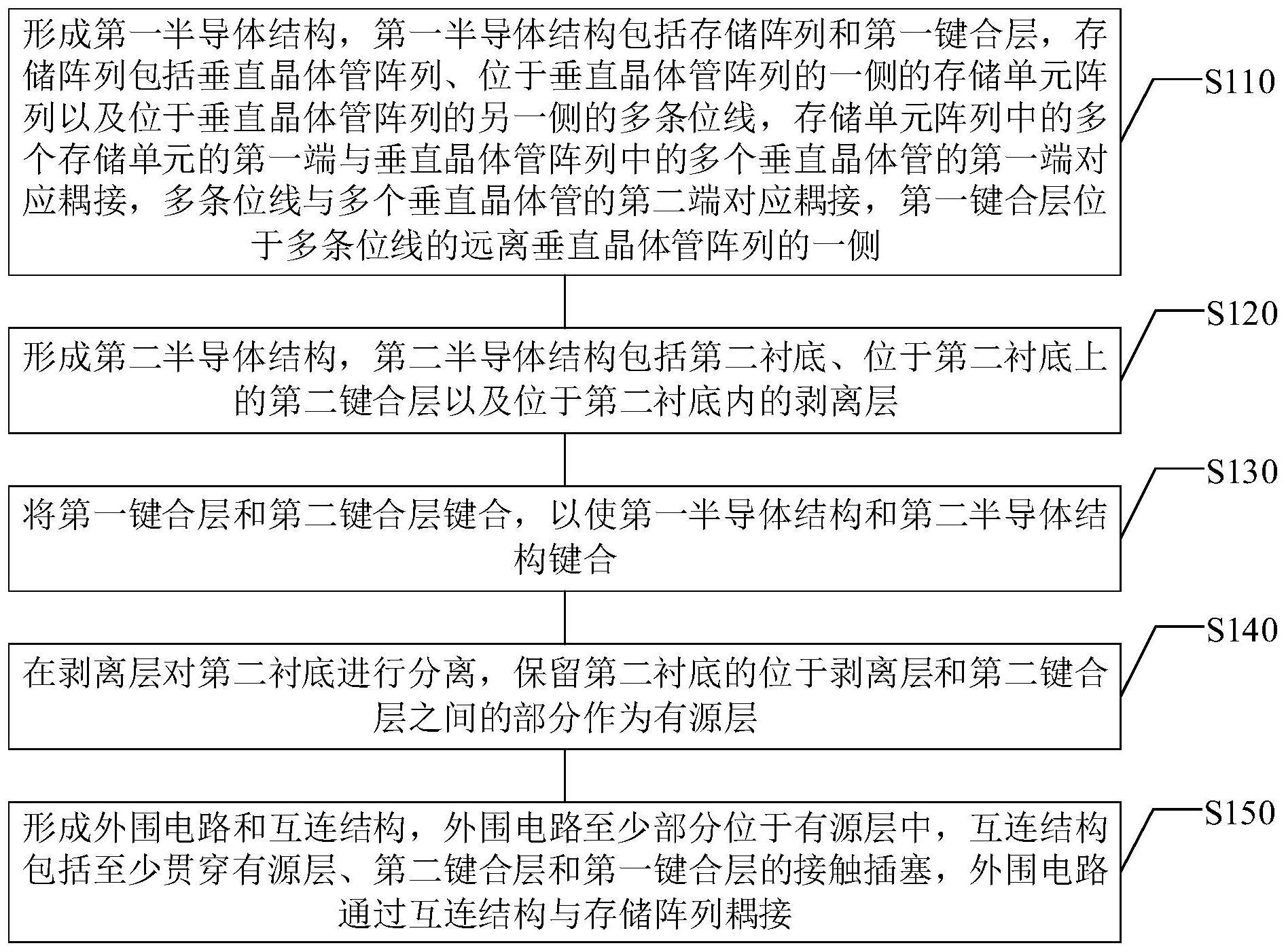

1、本公开实施例提供了一种存储器的制备方法,包括:形成第一半导体结构,所述第一半导体结构包括存储阵列和第一键合层,所述存储阵列包括垂直晶体管阵列、位于所述垂直晶体管阵列的一侧的存储单元阵列以及位于所述垂直晶体管阵列的另一侧的多条位线,所述存储单元阵列中的多个存储单元的第一端与所述垂直晶体管阵列中的多个垂直晶体管的第一端对应耦接,所述多条位线与所述多个垂直晶体管的第二端对应耦接,所述第一键合层位于所述多条位线的远离所述垂直晶体管阵列的一侧;形成第二半导体结构,所述第二半导体结构包括第二衬底、位于所述第二衬底上的第二键合层以及位于所述第二衬底内的剥离层;将所述第一键合层和所述第二键合层键合,以使所述第一半导体结构和所述第二半导体结构键合;在所述剥离层对所述第二衬底进行分离,保留所述第二衬底的位于所述剥离层和所述第二键合层之间的部分作为有源层;形成外围电路和互连结构,所述外围电路至少部分位于所述有源层中,所述互连结构包括至少贯穿所述有源层、所述第二键合层和所述第一键合层的接触插塞,所述外围电路至少部分通过所述接触插塞与所述存储阵列耦接。

2、在本公开的一些实施例中,形成所述第一半导体结构,包括:提供第一衬底,并在在所述第一衬底上形成所述垂直晶体管阵列;在所述垂直晶体管阵列的远离所述第一衬底的一侧形成所述存储单元阵列;从所述第一衬底的远离所述垂直晶体管阵列的一侧减薄所述第一衬底,直到露出所述多个垂直晶体管的第二端;在所述多个垂直晶体管的第二端的远离所述存储单元阵列的一侧形成所述多条位线;在所述多条位线的远离所述垂直晶体管阵列的一侧形成所述第一键合层。

3、在本公开的一些实施例中,在所述第一衬底上形成所述垂直晶体管阵列,包括:在所述第一衬底中形成有源柱阵列;在所述有源柱阵列中的多个有源柱的侧壁上形成多条字线,每个所述有源柱包括位于对应的所述字线的相对两侧的第一端和第二端;对所述多个有源柱的第一端进行掺杂以形成第一源漏区,所述第一源漏区作为所述多个垂直晶体管的第一端;以及在露出所述多个垂直晶体管的第二端之后,在形成所述多条位线之前,对所述多个有源柱的第二端进行掺杂以形成第二源漏区,所述第二源漏区作为所述多个垂直晶体管的第二端。

4、在本公开的一些实施例中,所述方法还包括:在形成所述第一键合层之前,形成多个第一连接插塞和至少一个第二连接插塞,所述多个第一连接插塞分别与所述多条字线的端部对应耦接,所述至少一个第二连接插塞与所述多个存储单元的第二端耦接;其中,在形成所述第一键合层之后,所述多个第一连接插塞位于所述多条字线和所述第一键合层之间,所述至少一个第二连接插塞位于所述多个存储单元和所述第一键合层之间。

5、在本公开的一些实施例中,形成所述外围电路和所述互连结构,包括:在所述有源层上形成所述外围电路;形成覆盖所述有源层和所述外围电路的介质层;形成所述互连结构,所述互连结构包括贯穿所述介质层、所述有源层、所述第二键合层和所述第一键合层的所述接触插塞,所述接触插塞包括与所述多个第一连接插塞对应耦接的多个第一接触插塞、与所述至少一个第二连接插塞对应耦接的至少一个第二接触插塞以及与所述多条位线对应耦接的多个第三接触插塞。

6、在本公开的一些实施例中,形成所述互连结构包括:在形成所述接触插塞之前,形成贯穿所述介质层、所述有源层、所述第二键合层和所述第一键合层的过孔;至少在贯穿所述有源层的所述过孔的内壁上形成间隔层;在所述过孔中填充所述接触插塞,所述间隔层至少位于所述有源层的过孔的内壁和所述接触插塞之间。

7、在本公开的一些实施例中,在所述多个垂直晶体管的第二端的远离所述存储单元阵列的一侧形成所述多条位线,包括:在所述多个垂直晶体管的第二端所在的一侧形成绝缘层;在所述绝缘层中形成所述多条位线。

8、在本公开的一些实施例中,形成所述第二半导体结构,包括:提供所述第二衬底;在所述第二衬底的一侧形成所述第二键合层;从形成有所述第二键合层的一侧向所述第二衬底内注入氢离子,以形成所述剥离层;在所述剥离层对所述第二衬底进行分离,包括:对所述第二衬底进行加热,使得所述第二衬底以所述剥离层为界线分离。

9、本公开实施例还提供了一种存储器,包括:存储阵列、第一键合层、第二键合层、有源层、外围电路和互连结构。

10、所述存储阵列包括垂直晶体管阵列、位于所述垂直晶体管阵列的一侧的存储单元阵列以及位于所述垂直晶体管阵列的另一侧的多条位线,所述存储单元阵列中的多个存储单元的第一端与所述垂直晶体管阵列中的多个垂直晶体管的第一端对应耦接,所述多条位线与所述多个垂直晶体管的第二端对应耦接。

11、第一键合层位于所述多条位线的远离所述垂直晶体管阵列的一侧。第二键合层,位于所述第一键合层的远离所述多条位线的一侧,与所述第一键合层键合。有源层位于所述第二键合层的远离所述第一键合层的一侧。所述外围电路至少部分位于所述有源层中,所述互连结构包括至少贯穿所述有源层、所述第二键合层和所述第一键合层的接触插塞,所述外围电路至少部分通过所述接触插塞与所述存储阵列耦接。

12、在本公开的一些实施例中,所述存储器还包括:多条字线,与所述多个垂直晶体管对应耦接;多个第一连接插塞,位于所述多条字线和所述第一键合层之间,分别与所述多条字线的端部对应耦接;至少一个第二连接插塞,位于所述多个存储单元和所述第一键合层之间,与所述多个存储单元的第二端耦接。

13、在本公开的一些实施例中,所述接触插塞包括:多个第一接触插塞,与所述多个第一连接插塞对应耦接;至少一个第二接触插塞,与所述至少一个第二连接插塞对应耦接;多个第三接触插塞,与所述多条位线的中部对应耦接。

14、在本公开的一些实施例中,所述存储单元包括电容器、相变存储单元和铁电存储单元之一。

15、上述技术方案可知,本公开实施例的晶体管结构具备以下优点和积极效果中的至少之一:

16、本公开实施例中,利用第一键合层和第二键合层,将第一半导体结构和第二半导体结构键合后,再在第二半导体结构的有源层上形成外围电路和互连结构,以形成存储器,因而本公开实施例提供了一种新的三维存储器的制备方法,以提高存储器的密度。

技术特征:

1.一种存储器的制备方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,形成所述第一半导体结构,包括:

3.根据权利要求2所述的方法,其特征在于,在所述第一衬底上形成所述垂直晶体管阵列,包括:

4.根据权利要求3所述的方法,其特征在于,还包括:

5.根据权利要求4所述的方法,其特征在于,形成所述外围电路和所述互连结构,包括:

6.根据权利要求5所述的方法,其特征在于,形成所述互连结构包括:

7.根据权利要求2所述的方法,其特征在于,在所述多个垂直晶体管的第二端的远离所述存储单元阵列的一侧形成所述多条位线,包括:

8.根据权利要求1至7中任一项所述的方法,其特征在于,形成所述第二半导体结构,包括:

9.一种存储器,其特征在于,包括:

10.根据权利要求9所述的存储器,其特征在于,还包括:

11.根据权利要求10所述的存储器,其特征在于,所述接触插塞包括:

12.根据权利要求9所述的存储器,其特征在于,所述存储单元包括电容器、相变存储单元和铁电存储单元之一。

技术总结

本公开提供一种存储器的制备方法及存储器,该方法包括:形成第一半导体结构,其包括存储阵列和第一键合层,存储阵列包括垂直晶体管阵列、存储单元阵列以及多条位线,多个存储单元的第一端与多个垂直晶体管的第一端对应耦接,多条位线与多个垂直晶体管的第二端对应耦接,第一键合层位于多条位线的一侧;形成第二半导体结构,其包括第二衬底、位于第二衬底上的第二键合层以及位于第二衬底内的剥离层;将第一键合层和第二键合层键合;在剥离层对第二衬底分离,保留位于剥离层和第二键合层之间的部分作为有源层;形成外围电路和互连结构,外围电路至少部分位于有源层中,外围电路通过互连结构与存储阵列耦接。本公开的制备方法能提高存储器的密度。

技术研发人员:冯道欢,蒋懿,肖德元

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!