布线基板的制作方法

本发明涉及布线基板。

背景技术:

1、专利文献1所公开的印刷布线板具有:芯基板;第1低密度积层,其形成在芯基板的第1面上;第2低密度积层,其形成在芯基板的第2面上;第1高密度积层,其形成在第1低密度积层的芯基板的相反侧;以及第2高密度积层,其形成在第2低密度积层的芯基板的相反侧。

2、专利文献1:日本特开2019-75398号公报

3、在专利文献1所公开的印刷布线板中,具有相同程度的导体密度的第1以及第2高密度积层所具有的导体层形成得比第1以及第2低密度积层所具有的导体层薄。认为存在第1以及第2高密度积层所具有的导体层中包含的布线的纵横比较低的情况。另外,认为存在由第1以及第2高密度积层所包含的布线输送的信号的插入损失(插入损耗)较大的情况。

技术实现思路

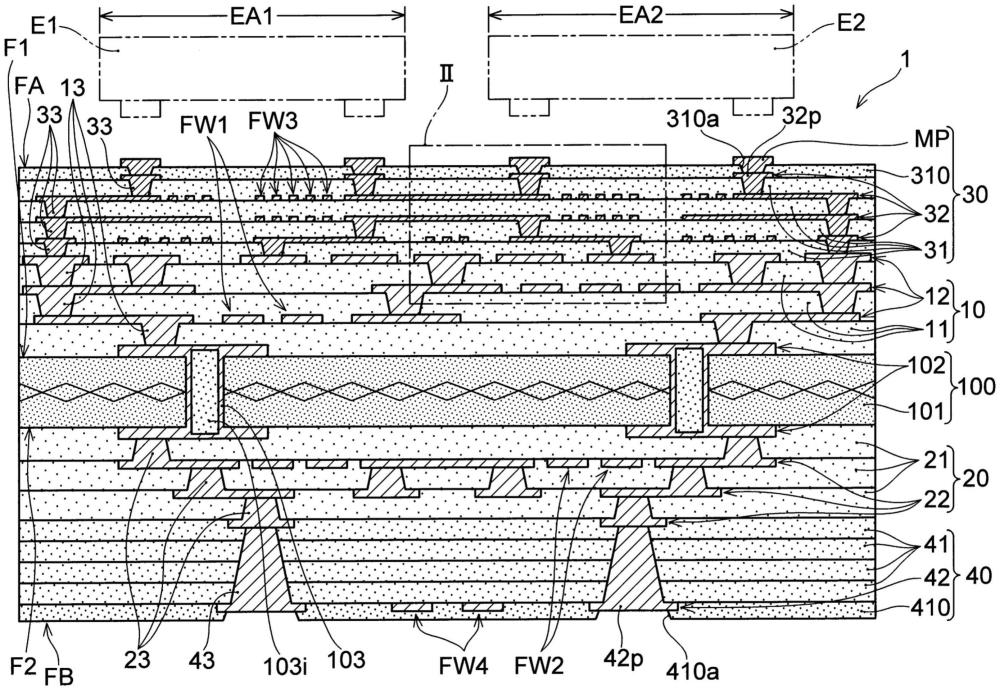

1、本发明的布线基板具有:芯基板,其具有第1面和与所述第1面相反侧的第2面;第1积层部,其形成在所述第1面上,包含交替层叠的多个第1绝缘层和多个第1导体层;第2积层部,其形成在所述第2面上,包含交替层叠的多个第2绝缘层和多个第2导体层;第3积层部,其形成在所述第1积层部上,包含交替层叠的多个第3绝缘层和多个第3导体层;以及第4积层部,其形成在所述第2积层部上,包含交替层叠的至少一层第4绝缘层和至少一层第4导体层。所述布线基板的最外侧的面由所述第3积层部的最外表面和所述第4积层部的最外表面构成,所述第3导体层所包含的布线的布线宽度的最小值小于所述第1导体层、所述第2导体层以及所述第4导体层所包含的布线的布线宽度的最小值,所述第3导体层所包含的布线的布线间距离的最小值小于所述第1导体层、所述第2导体层以及所述第4导体层所包含的布线的布线间距离的最小值,所述第3导体层所包含的布线的布线宽度的最小值为3μm以下且布线间距离的最小值为3μm以下,所述第3导体层所包含的布线的纵横比为2.0以上且4.0以下,所述第3导体层所包含的布线的上表面为研磨面。

2、根据本发明的实施方式,认为能够提供一种布线基板,该布线基板包含比较微细且高纵横比、通过比较良好的厚度的均匀性而输送的信号的插入损失比较小的布线。

技术特征:

1.一种布线基板,其具有:

2.根据权利要求1所述的布线基板,其中,

3.根据权利要求1所述的布线基板,其中,

4.根据权利要求1所述的布线基板,其中,

5.根据权利要求1所述的布线基板,其中,

6.根据权利要求1所述的布线基板,其中,

7.根据权利要求1所述的布线基板,其中,

8.根据权利要求1所述的布线基板,其中,

9.根据权利要求1所述的布线基板,其中,

10.根据权利要求1所述的布线基板,其中,

11.根据权利要求1所述的布线基板,其中,

技术总结

本发明提供布线基板,其包含高纵横比的布线。实施方式的布线基板具有:第1积层部(10),其形成在芯基板(100)的第1面(F1)上,包含第1导体层(12);第2积层部(20),其形成在芯基板的第2面(F2)上,包含第2导体层(22);第3积层部(30),其形成在第1积层部上,包含第3导体层(32);以及第4积层部(40),其形成在第2积层部上,包含第4导体层(42)。第3导体层所包含的布线的布线宽度和布线间距离的最小值小于第1、第2和第4导体层所包含的布线的布线宽度和布线间距离的最小值,第3导体层所包含的布线的布线宽度的最小值为3μm以下,并且布线间距离的最小值为3μm以下,纵横比为2.0以上且4.0以下,上表面为研磨面。

技术研发人员:古谷俊树,桑原雅

受保护的技术使用者:揖斐电株式会社

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!