一种新型无源浮地型忆阻器电路

本发明属于新型器件领域,具体涉及一种新型无源浮地型忆阻器电路。

背景技术:

1、如今的大数据时代,传统计算机中访问速度和cpu处理速度之间的差距逐渐增大,功耗墙、存储墙等问题愈发严重。忆阻器具有低功耗、非易失性等特点,为发展信息存储和处理融合的新型计算机体系框架、突破冯·诺依曼架构瓶颈提供了可行的路线。蔡少棠教授早在1971年提出了忆阻器的概念,并在2013年总结出了忆阻器的三条判断依据。然而,利用mosfet搭建电路构成的忆阻器大部分为有源器件,其余的无源忆阻器电路存在工作频率低、工作电压范围窄、需要单端接地等缺点。因此寻找新的忆阻器无源电路尤为重要。

技术实现思路

1、本发明的目的:提出种新型无源浮地型忆阻器电路。

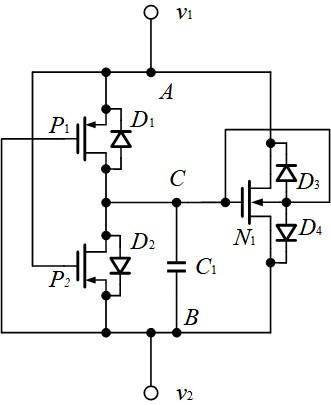

2、为实现本发明,采用的技术方案是:一种新型无源浮地型忆阻器电路,整体电路由2个pmos晶体管( p1、 p2)、1个nmos晶体管( n1)和1个电容( c1)构成。其中, p1的源极和 p2的栅极、 n1的源、漏极中任意一端连接,并和一个电源端口 v1连接; p1的漏极和 p2的漏极、 n1的栅极连接,并和电容器 c1的一端连接; p2的源极和 p1的栅极、电容器 c1的另一端、 n1的源、漏极中的另一端连接,并和另一个电源端口 v2连接; n1的衬底和它的栅极连接。

3、当忆阻器电路的两端通入正弦电压信号时, p1、 p2 、p1的寄生二极管 d1 、p2的寄生二极管 d2 、n1的寄生二极管 d3和 d4分别导通,产生的电流控制电容 c1的充电和放电,电容 c1上产生周期性变化的电压; n1的衬底和 n1的栅极连接, n1上流过的电流由电容 c1两端的电压控制; n1的宽长之比大于 p1、 p2的宽长之比,忆阻器电路上的电流可以等效为 n1上流过的电流;电路两端的输入电压和电路上的电流呈非线性关系,表现忆阻器的阻变特性。所述的忆阻器电路仅由mos晶体管和电容两种无源分立器件构成,工作时不需要额外的偏置电压,拥有较高的工作频率和较宽的工作电压范围,结构简单,方便集成。

4、本发明的有益效果:1. 本发明使用2个pmos晶体管、1个nmos晶体管和1个电容实现忆阻器电路,不需要使用除mos晶体管和电容之外的无源分立器件,结构设计简单。2. 本发明属于二端浮地型器件,工作时不需要额外的偏置电压。3. 本发明具有较高的工作频率、较宽的工作电压范围。

5、图1是本发明一种新型无源浮地型忆阻器电路的整体电路图。

6、图2是本发明电路在输入正弦波时的正半周期回路。

7、图3是本发明电路在输入正弦波时的负半周期回路。

8、图4是本发明电路电容 c 1 =30 pf,电路通入频率 f=100 khz、幅值为1 v的正弦波时输入电压和输入电流之间的伏安曲线图。

9、图5是本发明电路电容 c 1 =100 ff,电路通入频率 f=10 mhz、幅值为1 v的正弦波时输入电压和输入电流之间的伏安曲线图。

10、图6是本发明电路电容 c 1 =5 ff,电路通入频率 f=100 mhz、幅值为1 v的正弦波时输入电压和输入电流之间的伏安曲线图。

11、图7是本发明电路电容 c 1=1 nf,电路通入脉冲宽度2 us、周期20 us、高电平1 v 、低电平0 v的脉冲电压时的输入电压和输入电流的曲线图。

技术特征:

1.一种新型无源浮地型忆阻器电路,忆阻器电路特点在于:整体电路由2个pmos晶体管(p1、p2)、1个nmos晶体管(n1)和1个电容(c1)构成。其中,p1的源极和p2的栅极、n1的源、漏极中的一端连接,并和一个电源端口v1连接;p1的漏极和p2的漏极、n1的栅极连接,并和电容器c1的一端连接;p2的源极和p1的栅极、电容器c1的另一端、n1的源、漏极中的另一端连接,并和另一个电源端口v2连接;n1的衬底和它的栅极连接。当忆阻器电路的两端通入正弦电压信号时,p1、p2、p1的寄生二极管d1、p2的寄生二极管d2、n1的寄生二极管d3和d4分别导通,产生的电流控制电容c1的充电和放电,电容c1上产生周期性变化的电压;n1上流过的电流由电容c1两端的电压控制;n1的宽长之比大于p1、p2的宽长之比,忆阻器电路上的电流可以等效为n1上的电流;电路两端的输入电压和电路上的电流呈非线性关系,表现忆阻器的阻变特性。所述电路构成的忆阻器属于二端浮地型元件,仅由mos晶体管和电容两种无源分立器件构成,工作时不需要额外的偏置电压,拥有较高的工作频率和较宽的工作电压范围,整体结构简单,方便集成。

2.根据权利要求1所述的一种新型无源浮地型忆阻器电路,电路的特点在于:电路的正半周期回路包括pmos晶体管p1、p2的寄生二极管d2、nmos晶体管n1、n1的寄生二极管d4和电容c1。当电路处于正半周期时,a点的电势首先不断升高,当a点和b点之间的电势差满足p1的导通条件后,p1导通,p1上产生的电流流入电容c1,电容c1充电,电容c1上的电压不断升高;之后a点的电势不断下降,当a点的电势低于c点的电势时,电容c1不再充电,电容c1通过p1向端口v1放电;当a点和b点之间的电势差不满足p1的导通条件时,p1关断;当c点和b点之间的电势差满足p2的寄生二极管d2、n1的寄生二极管d4的导通条件后,电容c1通过d2和d4向端口v2放电,电容c1上的电压不断降低;电容c1上的电压控制由n1上流过的电流,电流从端口v1流出,经过n1后流向端口v2;整体电路上的电流等效为n1上流过的电流,此时电流方向为正。

3.根据权利要求1所述的一种新型无源浮地型忆阻器电路,电路的特点在于:电路的负半周期回路包括pmos晶体管p2、p2的寄生二极管d2、pmos晶体管p1的寄生二极管d1、nmos晶体管n1、n1的寄生二极管d3、d4和电容c1。当电路处于负半周期时,c点和b点之间的电势差满足p2的寄生二极管d2、n1的寄生二极管d4的导通条件后,电容c1通过d2和d4向端口v2放电,电容c1上的电压不断降低;当c点和b点之间的电势差不满足p2的寄生二极管d2、n1的寄生二极管d4的导通条件时,d2和d4关断,电容c1不再放电;当a点和b点之间的电势差满足p2的导通条件后,p2导通,p2上产生的电流流入电容c1,电容c1充电,电容c1上的电压不断升高;当c点和a点之间的电势差达到p1的寄生二极管d1、n1的寄生二极管d3的导通压降后,电流从端口v2分别通过p2和d1、p2和d4流向端口v1;当a点和b点之间的电势差不满足p2的导通条件时,p2关断;电容c1上的电压控制由n1上流过的电流,电流从端口v2流出,经过n1后流向端口v1;整体电路上的电流等效为n1上流过的电流,此时电流方向为负。

4.根据权利要求1所述的一种新型无源浮地型忆阻器电路,电路的特点在于:所述忆阻器电路的阻值等效为忆阻器电路的输入电压和n1上流过的电流之间的比值。

5.根据权利要求1所述的一种新型无源浮地型忆阻器电路,电路的特点在于:所述电路构成的忆阻器属于二端浮地型器件,工作时不需要额外的偏置电压。

6.根据权利要求1所述的一种新型无源浮地型忆阻器电路,电路的特点在于:所述电路构成的忆阻器工作电压频率可达到100 mhz,工作电压幅值可到达2 v。

技术总结

本发明公开了一种新型无源浮地型忆阻器电路,整体电路由2个PMOS晶体管(P<subgt;1</subgt;、P<subgt;2</subgt;)、1个NMOS晶体管(N<subgt;1</subgt;)和1个电容(C<subgt;1</subgt;)构成。当P<subgt;1</subgt;、P<subgt;2</subgt;、P<subgt;1</subgt;的寄生二极管D<subgt;1</subgt;、P<subgt;2</subgt;的寄生二极管D<subgt;2</subgt;、N<subgt;1</subgt;的寄生二极管D<subgt;3</subgt;和D<subgt;4</subgt;导通后,产生的电流控制电容C<subgt;1</subgt;的充电和放电,电容C<subgt;1</subgt;上产生周期性变化的电压;N<subgt;1</subgt;的衬底和N<subgt;1</subgt;的栅极连接,N<subgt;1</subgt;上流过的电流由电容C<subgt;1</subgt;两端的电压控制。忆阻器电路的阻值可以等效为电路的输入电压和N<subgt;1</subgt;上流过的电流之间的比值。本发明中忆阻器电路仅由MOS晶体管和电容两种无源分立器件构成,工作时不需要额外的偏置电压,拥有较高的工作频率和较宽的工作电压范围,结构简单,利于集成。

技术研发人员:施阁,吴世恩,林如斌,王晨宇,黄玉清

受保护的技术使用者:中国计量大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!