一种高能耗效率和高面积效率的Sigma-Delta模数转换器

本发明涉及一种高能耗效率和高面积效率的sigma-delta模数转换器。

背景技术:

1、传感器在许多应用中都是必需的,比如应用于音频、温度、光、磁、力和电容等传感中,以及可穿戴设备的生物电位采集等。它通常处理频率从直流到数十khz的窄带信号。对于电池供电的传感器系统,节能的模数转换器(adc)尤为重要,通常会根据传感器的要求进行定制。这种adc还必须对偏移和闪烁噪声具有鲁棒性。此外,这类片上的adc通常需要在许多通道和需要大量通道的应用中进行多路复用,例如图像传感器或生物电位采集传感器,这些设备在能源和面积方面必须非常高效。

2、在所有类型的adc中,利用过采样和噪声整形的sigma-delta adc被广泛用于实现高分辨率。该体系结构包括三个主要的必备组件:环路滤波器、量化器和反馈数模转换器(dac)。调制器对模拟输入信号进行过采样,然后环路滤波器对该输入和估计输出(来自dac)之间的残余误差进行积分。在环路滤波器之后,量化器将处理后的信号数字化,并通过反馈dac提供信息。sigma-delta调制器在不重置环路积分器的情况下连续运行,并产生整形的量化噪声。因此,用低通数字抽取滤波器过滤带外量化噪声,并保持带内信号功率,可保证高的带内信号量化噪声比(sqnr)。此外,更高的环路阶数会在带外形成更多量化噪声,从而产生高分辨率性能。若周期性地重置环路滤波器和数字滤波器,便构成增量式adc(iadc)。iadc虽然中断了环路的连续性,但也带来易于多路复用和低延迟、较少受到空闲音的影响以及滤波比较简单的优点,因此被广泛用于传感器应用中。iadc由于周期性进行重置,因此也可以被认为是奈奎斯特型adc,这也为其与其他奈奎斯特型adc的混合应用提供了条件。

3、一阶iadc需要很长的转换时间,导致能源效率低下。为了缩短转换时间,从而提高能源效率,可以使用高阶iadc。然而,它们更容易不稳定,并且输入范围较小。因此,研究了与奈奎斯特速率adc结合的混合iadc。在混合iadc结构中,zoom技术和两步式以及多步式架构等被广泛应用。

4、zoom技术最显著的优点是可以缩小环路积分器的摆幅,因此可以在不损失信号的输入范围基础上,使用高能效的放大器,以节约能耗。两步式以及多步式架构最显著的优点是可以通过多步的转换在达到相同信号噪声比(snr)情况下降低adc的过采样率(osr),从而降低时钟频率,降低系统总能耗。

技术实现思路

1、本发明的目的在于提供一种高能耗效率和高面积效率的sigma-delta模数转换器。

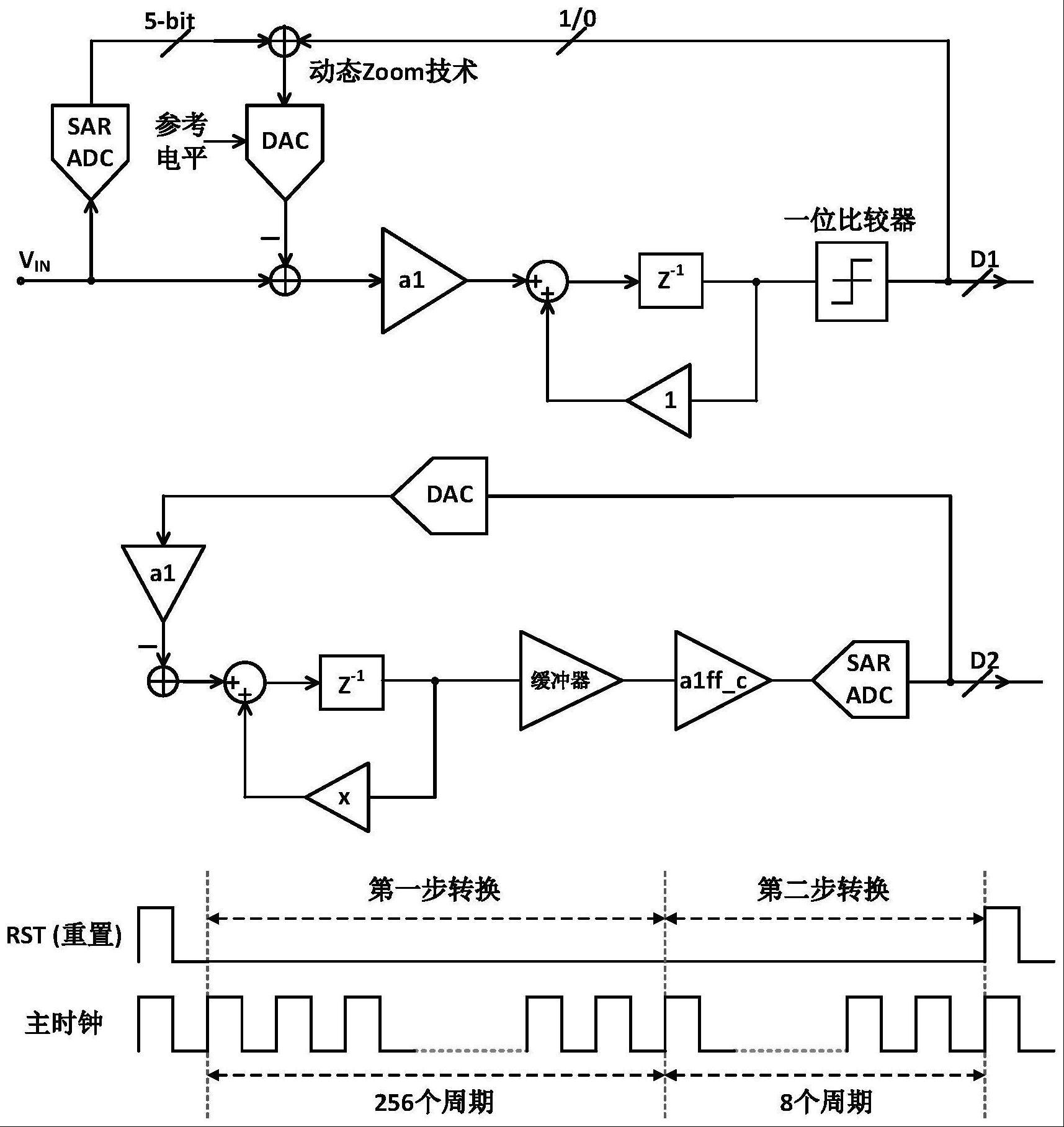

2、本发明提供了一种高能耗效率和高面积效率的sigma-delta模数转换器,包括:环路积分器、量化器、比较器、缓冲器、电容dac(cdac)模块和时钟产生模块,量化器为saradc,以信号流为描述路径,其中:

3、在第一步转换中,输入信号分别连接sar adc的输入端和cdac模块的输入端;saradc的输出端连接cdac模块的输入端;cdac模块的输出端连接环路积分器的输入端,环路积分器的输出端连接比较器的输入端,比较器的输出端连接cdac模块的输入端,构成sigma-delta环路;

4、在第二步转换中,不接收输入信号,同时关闭比较器,打开缓冲器;当环路积分器进行重构后,环路积分器的输出端连接缓冲器的输入端,缓冲器的输出端连sar adc的输入端,sar adc的输出端连接cdac模块的输入端,cdac模块的输出端连接环路积分器的输入端,构成sigma-delta环路。

5、本发明提出的一种高能耗效率和高面积效率的sigma-delta模数转换器的操作方法,具体步骤如下:

6、在第一步转换中,sar adc首先量化输入信号,其转换结果结合比较器的比较结果,产生cdac模块的参考电平,再由输入信号与cdac模块产生环路积分器的输入值;此时,缓冲器关闭;

7、在第二步转换中,不接收输入信号,比较器关闭,sar adc作为sigma-delta环路中的量化器使用,缓冲器开启,形成新的环路;

8、最终的输出结果由第一步转换和第二步转换的sar adc转换结果共同产生。

9、本发明中,zoom技术采用sar adc和一位比较器结合实现。

10、本发明中,两步式架构将重构环路量化器,并仅在第二步开启缓冲器模块。第一步运行时,量化器采用一位比较器实现,zoom技术同时开启,此时缓冲器未开启;第二步运行时,启动在第一步未开启的缓冲器,zoom技术关闭,用作zoom量化的sar adc重构为环路量化器。

11、本发明结合了两步式架构和zoom技术,显著缩小了环路积分器模块的输入、输出摆幅,为使用高能效的放大器提供了可能。同时,利用第二步的再转换,在达到同样的snr情况下,大大降低了osr,为达到高精度要求的同时进一步降低功耗提供了可能。

12、本发明提出的第一步采用sar adc辅助实现的zoom技术和第二步采用sar adc量化器的方法,为sar adc的复用提供了可能。本发明中,采用同一个sar adc分别在第一步和第二步的转换中进行量化转换,不仅节约了功耗,同时节约了面积和硬件开销。

13、本发明提出的第二步转换使用的缓冲器模块由于仅在第二步转换中有效,对其进行了周期性的开启和关断,即,仅在第二步时开启。周期性地开启使得平均功耗大大降低,进一步实现了低功耗设计,提高了能耗效率。

14、1、本发明创新性地将zoom技术和两步式架构结合,在第一步转换时采用zoom技术,使用sar adc进行输入信号的量化,在第二步转换时采用同一个sar adc,对环路积分器的输出进行了量化,因此复用了sar adc,充分利用了zoom技术来缩小环路的摆幅,降低了能耗,并通过两步复用进一步提升了能耗效率,同时提高了面积效率。

15、2、本发明创新性地对缓冲器模块进行了周期性地开启和关断。在第一步转换中没有开启缓冲器模块,在第二步转换中开启了缓冲器模块,将缓冲器的高能耗平均到整个周期内,大大降低了平均功耗,提高了能耗效率。

16、综上所述,本发明提出的架构和技术可以提升adc的能耗效率和面积效率。

技术特征:

1.一种高能耗效率和高面积效率的sigma-delta模数转换器,其特征在于包括:环路积分器、量化器、比较器、缓冲器、电容dac(cdac)模块和时钟产生模块,量化器为sar adc,以信号流为描述路径,其中:

2.根据权利要求1所述的一种高能耗效率和高面积效率的sigma-delta模数转换器,其特征在于所述模数转换器的操作方法,具体步骤如下:

技术总结

本发明涉及一种高能耗效率和高面积效率的Sigma‑Delta模数转换器,包括环路积分器、SAR ADC、比较器、缓冲器、CDAC模块和时钟产生模块,以信号流为描述路径,在第一步转换中,输入信号分别连接SAR ADC和CDAC模块;SAR ADC依次连接CDAC模块、环路积分器、比较器和CDAC模块,构成Sigma‑Delta环路;在第二步转换中,不接收输入信号,同时关闭比较器,打开缓冲器;当环路积分器进行重构后,环路积分器依次连接缓冲器、SAR ADC、CDAC模块和环路积分器,构成Sigma‑Delta环路。本发明提出的架构和技术可以提升ADC的能耗效率和面积效率。

技术研发人员:张书文,方来榕,徐佳伟

受保护的技术使用者:复旦大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!