一种驱动电路及输入输出端口电路的制作方法

本申请涉及但不限于集成电路技术,其中涉及一种驱动电路及输入输出端口电路。

背景技术:

1、输入输出(io)端口电路是芯片中的基本模块之一,它的主要作用是提供封装引脚到芯片内部之间的接口,将外部信号引入芯片内部进行逻辑功能的实现,并把结果输出给芯片外部的电路,根据需要可以通过配置来支持多种不同的接口标准。

2、根据信号传输方向的不同,可以将io端口电路分为驱动电路和接收电路,驱动电路根据协议标准的不同又可以分为单端驱动电路(用于支持高速多模式多通道(lvcmos)等单端传输协议)以及差分驱动电路(用于支持低电压差分信号(lvds)协议等传输协议);其中,单端驱动电路通常由电平移位器、预驱动器和驱动器三级结构组成,实现将输出信号从内部低压转换为io电压的功能;由于外部负载电平标准的多样性,通常io的设计要求兼容1.0伏到3.3伏的宽电源电压范围,因此io电路的设计不得不采用耐3.3伏高压的大尺寸金属-氧化物半导体场效应晶体管(mos)管,当io电源电压较低(例如1.0v)时,用低电源电压驱动大尺寸mos管,会导致电路速度显著变慢,无法达到高速的应用要求。申请号为2017112490908的在先申请,公开了一种利用低压器件实现耐高压的高速io电路,通过串联电阻和mos管的形式保护静电放电(esd)管,使其能够利用低压mos管耐受高压,但是其输出接口到地,以及电源到地之间均串联了电阻,一方面增加了电路的功耗,另一方面由于引入了额外的电阻和电容,也不利于高速电压的实现;申请号为2020203534641的在先申请,公开了一种编程器高速io与高压电路并存的电路,申请号为2019100238489的在先申请,公开了一种基于低压器件的高压高速io电路,提供了其他的电压保护方式,但仍然是以串联电阻为主要手段,和上述方案类似,增加了电路的功耗,同时也限制了io电路的传输速度。

3、综上,如何实现满足应用要求的单端驱动电路,成为一个有待解决的问题。

技术实现思路

1、以下是对本申请详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、本公开实施例提供一种驱动电路及输入输出端口电路,能够满足io电路的功耗和传输速度要求。

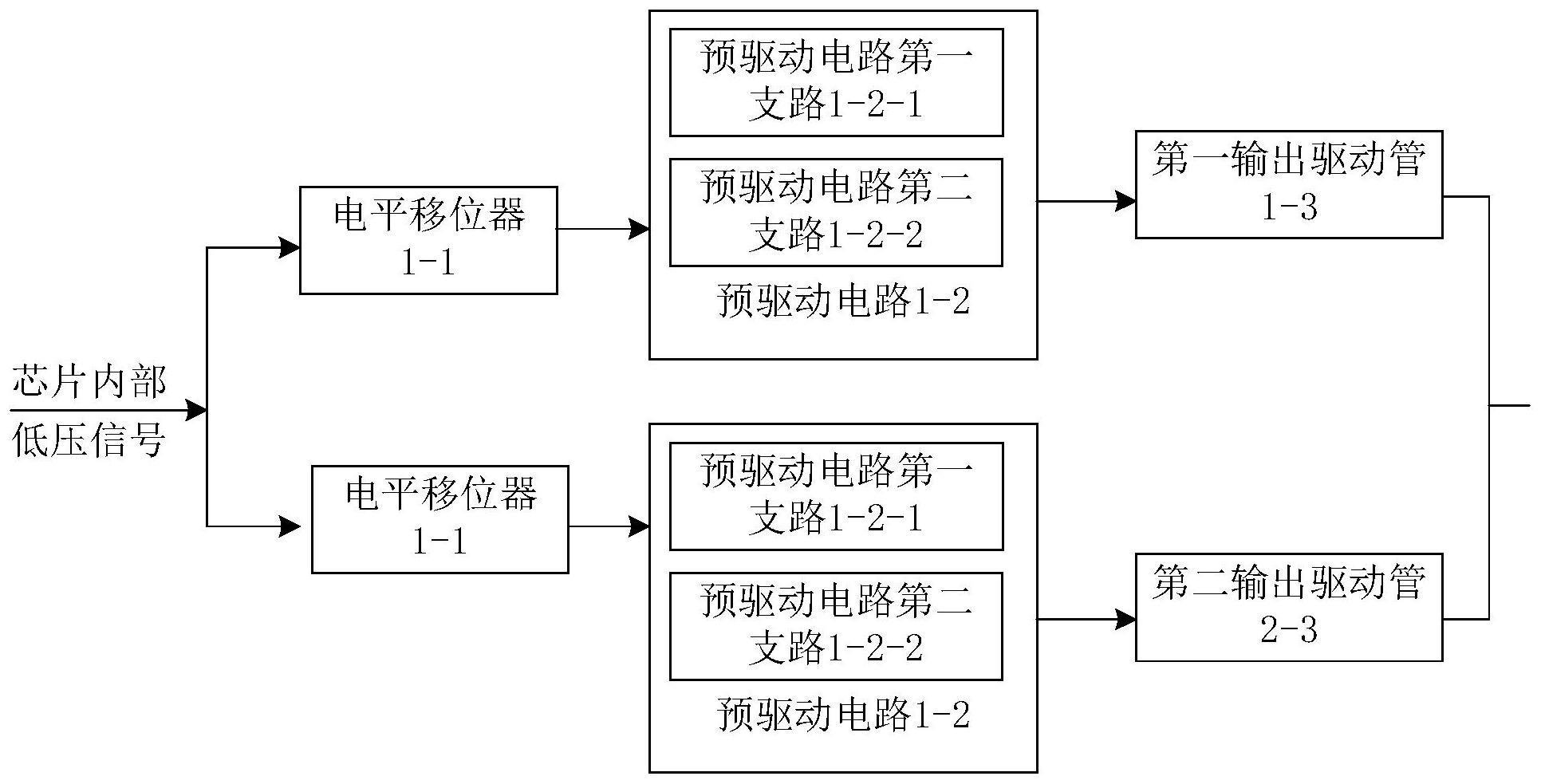

3、本公开实施例提供了一种驱动电路包括:结构相同的两个驱动支路;每一个驱动支路均包括相应的电平移位器、预驱动电路;第一个驱动支路的电平移位器与预驱动电路连接;第二个驱动支路的电平移位器与预驱动电路连接;其中,

4、电平移位器设置为:将内部低压信号转换为外部驱动所需要的输入输出(io)的电源电压;

5、预驱动电路包括由高压器件构成的预驱动电路第一支路和由低压器件构成的预驱动电路第二支路,设置为:根据电平移位器转换获得的io的电源电压的高低,选择由预驱动电路第一支路或预驱动电路第二支路驱动输出驱动管输出驱动信号;

6、其中,所述高压器件包括可承受电压大于或等于预设的第一电压阈值的器件;所述低压器件包括可承受电压小于或等于预设的第二电压阈值的器件;输出驱动管包括:与第一个驱动支路的预驱动电路连接的第一输出驱动管;与第二个驱动支路的预驱动电路连接的第二输出驱动管。

7、另一方面,本公开实施例还提供一种输入输出端口电路,包括上述的驱动电路。

8、与相关技术相比,本申请包括:结构相同的两个驱动支路;每一个驱动支路均包括相应的电平移位器、预驱动电路;第一个驱动支路的电平移位器与预驱动电路连接;第二个驱动支路的电平移位器与预驱动电路连接;其中,电平移位器设置为:将内部低压信号转换为外部驱动所需要的输入输出(io)的电源电压;预驱动电路包括由高压器件构成的预驱动电路第一支路和由低压器件构成的预驱动电路第二支路,设置为:根据电平移位器转换获得的io的电源电压的高低,选择由预驱动电路第一支路或预驱动电路第二支路驱动输出驱动管输出驱动信号;其中,所述高压器件包括可承受电压大于或等于预设的第一电压阈值的器件;所述低压器件包括可承受电压小于或等于预设的第二电压阈值的器件;输出驱动管包括:与第一个驱动支路的预驱动电路连接的第一输出驱动管,与第二个驱动支路的预驱动电路连接的第二输出驱动管。本公开实施例实现了满足宽电压范围的驱动电路,为满足io端口的传输速度要求提供了支持。

9、本申请的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本申请而了解。本申请的其他优点可通过在说明书以及附图中所描述的方案来实现和获得。

技术特征:

1.一种驱动电路,包括:结构相同的两个驱动支路;每一个驱动支路均包括相应的电平移位器(1-1)、预驱动电路(1-2);第一个驱动支路的电平移位器(1-1)与预驱动电路(1-2)连接;第二个驱动支路的电平移位器(1-1)与预驱动电路(1-2)连接;其中,

2.根据权利要求1所述的驱动电路,其特征在于,所述预驱动电路(1-2)是设置为:

3.根据权利要求2所述的驱动电路,其特征在于,所述第一控制信号和第二控制信号通过预先设定的比较器(401)产生。

4.根据权利要求3所述的驱动电路,其特征在于,所述第一控制信号包括第一电平的低压选择信号;所述第二控制信号包括第二电平的所述低压选择信号。

5.根据权利要求2至4任一项所述的驱动电路,其特征在于,所述预驱动电路第一支路(1-2-1)包括:第一逻辑电路(111)、第一开关(112)、第二开关(113)、具有上拉功能的第一金属-氧化物半导体场效应晶体管mos管(114)和具有下拉功能的第二mos管(115),所述第一开关(112)的第一端与所述第一逻辑电路(111)的输出端连接或接地,所述第一mos管(114)和所述第二mos管(115)的栅极连接后与所述第一开关(112)的第二端连接,所述第二开关(113)的第一端接所述io的电源电压,所述第二开关(113)的第二端连接第一mos管的源级,所述第一mos管(114)的漏极与所述第二mos管(115)的漏极连接后与所述输出驱动管连接,所述第二mos管(115)的源级接地;所述预驱动电路第一支路(1-2-1)是设置为:

6.根据权利要求5所述的驱动电路,其特征在于,所述第一mos管(114)和所述第二mos管(115)为耐压值大于预先设定的第三电压阈值的mos管。

7.根据权利要求2至4任一项所述的驱动电路,其特征在于,所述预驱动电路第二支路(1-2-2)包括:第二逻辑电路(123)、第三逻辑电路(126)、第三开关(121)、第四开关(122)、第五开关(124)、第六开关(125)、第七开关(127)、第八开关(128)、第九开关(129)、第十开关(1210)、具有上拉功能的第三mos管(1211)和具有下拉功能的第四mos管(1212),其中,所述第三开关(121)的第一端连接所述io的电源电压,所述第三开关(121)的第二端连接所述第二逻辑电路(123);所述第四开关(122)的第一端接地,所述第四开关(122)的第二端连接第二逻辑电路(123);所述第二逻辑电路(123)和所述第三逻辑电路(126)的输入端用于接收所述第二控制信号;所述第五开关(124)的第一端连接所述io的电源电压,所述第五开关(124)的第二端连接所述第三逻辑电路(126);所述第六开关(125)的第一端接地,所述第六开关(125)的第如二端接第三逻辑电路(126);所述第七开关(127)的第一端接收预设的保护电压,所述第七开关(127)的第二端连接第二逻辑电路(123)的输出;所述第八开关(128)的第一端接收预设的保护电压,所述第八开关(128)的连接所述第三逻辑电路(126)的输出;所述第九开关(129)的第一端接io的电源电压,所述第九开关(129)的第二端接所述第三mos管(1211)的源极,所述第三mos管(1211)的栅极连接所述第二逻辑电路(123)的输出,所述第三mos管(1211)的漏极与所述第四mos管的漏极连接后,连接至所述输出驱动管;所述第十开关(1210)的第一端接地,所述第十开关(1210)的第二端连接第四mos管(1212)的源极;所述预驱动电路第二支路(1-2-2)是设置为:

8.根据权利要求7所述的驱动电路,其特征在于,所述第三mos管(1211)和所述第四mos管(1212)为耐压值低于预先设定的第四电压阈值的mos管。

9.一种输入输出端口电路,其特征在于,包括如权利要求1至8任一项所述的驱动电路。

技术总结

本申请公开一种驱动电路及输入输出端口电路,包括:结构相同的两个驱动支路;每一个驱动支路均包括相应的电平移位器、预驱动电路;第一个驱动支路的电平移位器与预驱动电路连接;第二个驱动支路的电平移位器与预驱动电路连接;其中,电平移位器设置为:将内部低压信号转换为外部驱动所需要的输入输出(IO)的电源电压;预驱动电路包括由高压器件构成的预驱动电路第一支路和由低压器件构成的预驱动电路第二支路,设置为:根据电平移位器转换获得的IO的电源电压的高低,选择由预驱动电路第一支路或预驱动电路第二支路驱动输出驱动管输出驱动信号。本公开实施例实现了满足宽电压范围的驱动电路,为满足IO端口的传输速度要求提供了支持。

技术研发人员:褚博,王天心,林晓志,王添平,李林,周垣

受保护的技术使用者:上海先基半导体科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!