一种异构反射式阻抗调谐器及其设计方法

本发明涉及集成电路技术,尤其涉及一种异构反射式阻抗调谐器及其设计方法。

背景技术:

1、近年来,阻抗调谐器件常被用在功率放大器负载牵引测试中,用来提取功率放大器在不同阻抗点处的功率、增益以及线性度等特性,也用来对放大器的失配状态下测试。传统调谐器所采用的阻抗调谐方法常通过切换不同传输线的电长度与特征阻抗实现,由于微带传输线的阻抗实虚部与频率的强相关性和切换所需的面积问题,该方法所设计的阻抗调谐器不具备小型化与宽带调谐特征,存在成本高、体积大、运行速度慢等缺点。

2、因此,设计一款小型化、高速调节、宽带调谐和覆盖史密斯圆图阻抗范围更大的电子式调谐器是当前技术设计的难点。

技术实现思路

1、为克服现有技术的不足及存在的问题,本发明提供一种异构反射式阻抗调谐器、射频芯片及其设计方法,解决了当前技术设计难以实现小型化、高速调节、宽带调谐和大阻抗覆盖范围的问题。

2、为实现上述目的,本发明采用如下技术方案:

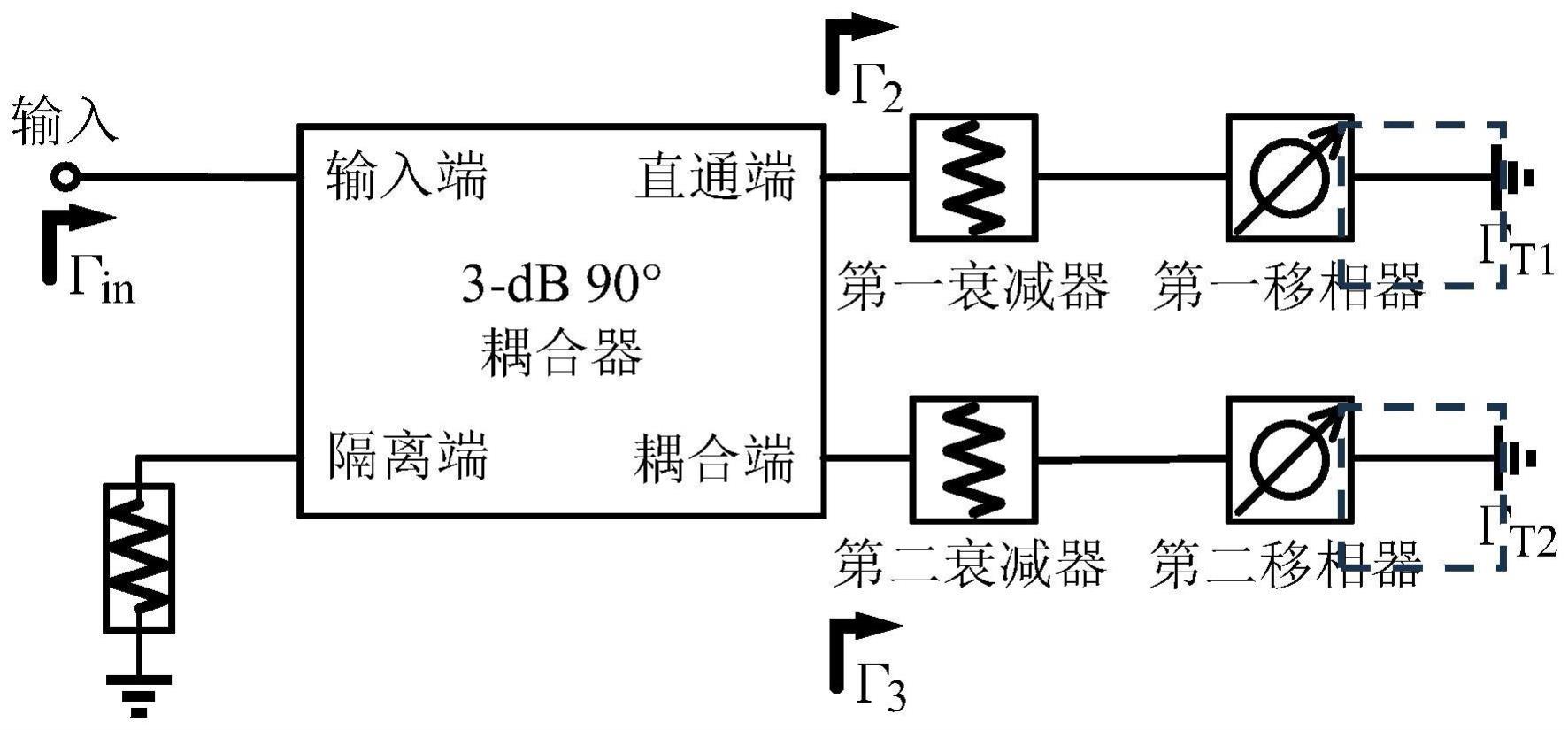

3、一方面,本发明公开了一种异构反射式阻抗调谐器,包括耦合器、第一移相器、第二移相、第一衰减器和第二衰减器,耦合器包括输入端、直通端、耦合端和隔离端,直通端、第一衰减器和第一移相器依次级联在一起,第一移相器的输出端接地,耦合端、第二衰减器和第二移相器依次级联在一起,第二移相器的输出端接地。

4、作为优选,所述第一移相器包括依次级联在一起的第一移相单元、第二移相单元、第三移相单元、第四移相单元、第五移相单元和第六移相单元,第六移相单元包括五阶高低通滤波器结构。

5、作为优选,所述第一衰减器包括依次级联在一起的第一衰减单元、第二衰减单元、第三衰减单元、第四衰减单元和第五衰减单元,第一衰减单元的衰减量为2db,第二衰减单元的衰减量为4db,第三衰减单元的衰减量为1db,第四衰减单元的衰减量为0.5db,第五衰减单元的衰减量为8db。

6、作为优选,所述第一衰减单元包括电阻r33、电阻r34、电感l14、电感l15、电感l16、开关管m33、开关管m34和开关管m35,电阻r33、电感l14和电阻r34依次串联在一起,开关管m33并联在电阻r33上,开关管m34电连接在电阻r33和电感l14之间,开关管m34、电感l15串联在一起,电感l15接地,开关管m35电连接在电阻r33和电感l15之间,开关管m35、电感l16串联在一起,电感l16接地,开关管m33、开关管m34、开关管m35、电感l15和电感l16所在的支线路呈π型。

7、作为优选,还包括异构集成衬底,异构集成衬底包括异构集成衬底包括硅基衬底、gaas衬底、介质层1、介质层2、介质层3、金属焊球、金属层m1、金属层m2、金属层m3、通孔1、通孔2和通孔3,硅基衬底、介质层1、介质层2、介质层3自下而上依次堆叠在一起,通孔1设置在介质层1上,通孔2设置在介质层2上,通孔3设置在介质层3上,金属层m1设置在通孔1和通孔2之间,金属层m2设置在通孔2和通孔3之间,金属层m3设置在通孔3和焊球之间,gaas衬底嵌入在硅基衬底中。

8、作为优选,所述第一移相器、第二移相、第一衰减器和第二衰减器采用gaas工艺设计。

9、作为优选,所述耦合器采用晶圆级封装工艺集成在金属层m1、金属层m2和金属层m3上,金属层m1作为耦合器的参考地,金属层m2作为耦合器的辅助传输线,金属层m3作为耦合器的主传输线。

10、作为优选,所述金属层m2包括微带线1,金属层m3包括微带线2,微带线1和微带线2耦合在一起,耦合在一起的微带线1和微带线2使得耦合器的输出信号相位差为90°。

11、作为优选,所述耦合器、第一衰减器、第二衰减器、第一移相器和第二移相器采用晶圆级封装工艺互联在异构集成衬底上。

12、另一方面,本发明还公开了一种异构反射式阻抗调谐器的设计方法,用于设计得到上述的一种异构反射式阻抗调谐器,包括:

13、步骤1:通过晶圆级封装工艺建立异构集成衬底,还通过ipd工艺将耦合器集成在异构集成衬底的金属层m1、金属层m2和金属层m3上,将金属层m1作为耦合器的参考地,通过耦合金属层m2和金属层m3使得耦合器的输出信号相位差为90°,金属层m2作为耦合器的辅助传输线,金属层m3作为耦合器的主传输线;

14、步骤2:采用gaas工艺设计第一衰减器和第二衰减器,其中,第一衰减器的衰减范围为0.5db-15.5db、衰减位数为5位、附加相移不超过2°,第一衰减器包括依次级联在一起的第一衰减单元、第二衰减单元、第三衰减单元、第四衰减单元和第五衰减单元,第一衰减单元的衰减量为2db,第二衰减单元的衰减量为4db,第三衰减单元的衰减量为1db,第四衰减单元的衰减量为0.5db,第五衰减单元的衰减量为8db;

15、步骤3:采用gaas工艺设计第一移相器和第二移相器,其中,第一移相器的移相范围为0°-360°,第一移相器的移相位数为6位;

16、步骤4:采用晶圆级封装工艺将耦合器、第一衰减器、第二衰减器、第一移相器和第二移相器互联在异构集成衬底上并得到所述的异构反射式阻抗调谐器,其中,将gaas衬底嵌入在硅基衬底中,将通孔1、金属层m1、通孔2、金属层m2、通孔3、金属层m3和金属焊球自下而上地垂直互连在一起。

17、本发明相比现有技术突出且有益的技术效果是:

18、在本发明中,本异构反射式阻抗调谐器采用了三维异构集成的电路结构,还结合了ipd工艺设计得到的耦合器以及gaas工艺设计得到的移相器、衰减器、耦合器,实现在5-6ghz频段内阻抗调谐的效果,其产生的阻抗点覆盖了史密斯圆图中小于1.7的等驻波比圆,实现了在c波段功率放大负载牵引测试,相较于现有技术,实现了阻抗调谐器的小型化、高速调节和宽带调谐的设计,具有小型化、高速调节控制、大阻抗覆盖范围、更小的封装尺寸以及低成本的优势,适用于c波段功率放大负载牵引测试。

技术特征:

1.一种异构反射式阻抗调谐器,其特征在于,包括耦合器、第一移相器、第二移相、第一衰减器和第二衰减器,耦合器包括输入端、直通端、耦合端和隔离端,直通端、第一衰减器和第一移相器依次级联在一起,第一移相器的输出端接地,耦合端、第二衰减器和第二移相器依次级联在一起,第二移相器的输出端接地。

2.根据权利要求1所述的一种异构反射式阻抗调谐器,其特征在于,所述第一移相器包括依次级联在一起的第一移相单元、第二移相单元、第三移相单元、第四移相单元、第五移相单元和第六移相单元,第六移相单元包括五阶高低通滤波器结构。

3.根据权利要求1所述的一种异构反射式阻抗调谐器,其特征在于,所述第一衰减器包括依次级联在一起的第一衰减单元、第二衰减单元、第三衰减单元、第四衰减单元和第五衰减单元,第一衰减单元的衰减量为2db,第二衰减单元的衰减量为4db,第三衰减单元的衰减量为1db,第四衰减单元的衰减量为0.5db,第五衰减单元的衰减量为8db。

4.根据权利要求3所述的一种异构反射式阻抗调谐器,其特征在于,所述第一衰减单元包括电阻r33、电阻r34、电感l14、电感l15、电感l16、开关管m33、开关管m34和开关管m35,电阻r33、电感l14和电阻r34依次串联在一起,开关管m33并联在电阻r33上,开关管m34电连接在电阻r33和电感l14之间,开关管m34、电感l15串联在一起,电感l15接地,开关管m35电连接在电阻r33和电感l15之间,开关管m35、电感l16串联在一起,电感l16接地,开关管m33、开关管m34、开关管m35、电感l15和电感l16所在的支线路呈π型。

5.根据权利要求1所述的一种异构反射式阻抗调谐器,其特征在于,还包括异构集成衬底,异构集成衬底包括异构集成衬底包括硅基衬底、gaas衬底、介质层1、介质层2、介质层3、金属焊球、金属层m1、金属层m2、金属层m3、通孔1、通孔2和通孔3,硅基衬底、介质层1、介质层2、介质层3自下而上依次堆叠在一起,通孔1设置在介质层1上,通孔2设置在介质层2上,通孔3设置在介质层3上,金属层m1设置在通孔1和通孔2之间,金属层m2设置在通孔2和通孔3之间,金属层m3设置在通孔3和焊球之间,gaas衬底嵌入在硅基衬底中。

6.根据权利要求5所述的一种异构反射式阻抗调谐器,其特征在于,所述第一移相器、第二移相、第一衰减器和第二衰减器采用gaas工艺设计。

7.根据权利要求5所述的一种异构反射式阻抗调谐器,其特征在于,所述耦合器采用晶圆级封装工艺集成在金属层m1、金属层m2和金属层m3上,金属层m1作为耦合器的参考地,金属层m2作为耦合器的辅助传输线,金属层m3作为耦合器的主传输线。

8.根据权利要求7所述的一种异构反射式阻抗调谐器,其特征在于,所述金属层m2包括微带线1,金属层m3包括微带线2,微带线1和微带线2耦合在一起,耦合在一起的微带线1和微带线2使得耦合器的输出信号相位差为90°。

9.根据权利要求5所述的一种异构反射式阻抗调谐器,其特征在于,所述耦合器、第一衰减器、第二衰减器、第一移相器和第二移相器采用晶圆级封装工艺互联在异构集成衬底上。

10.一种异构反射式阻抗调谐器的设计方法,其特征在于,用于设计得到权利要求5至9中任意一项所述的一种异构反射式阻抗调谐器,包括:

技术总结

本发明公开了一种异构反射式阻抗调谐器及其设计方法,采用了三维异构集成的电路结构,还结合了晶圆级封装工艺,包括IPD工艺设计得到的耦合器以及GaAs工艺设计得到的移相器、衰减器,通过对移相器和衰减器工作方式的控制,实现阻抗幅值和相位的变化,进而实现阻抗调谐功能,该异构反射式阻抗调谐器可采用可编程控制,适用于通信系统中放大器的负载牵引测试。

技术研发人员:苏国东,韩磊,刘军,苏江涛,游彬

受保护的技术使用者:杭州电子科技大学

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!